#### ISLAMIC UNIVERSITY OF TECHNOLOGY

#### **REMOTE DATA ACQUISITION SYSTEM USING FPGA**

By Husnain Al Bustam (082405) Nafiz Ur Rahman (082427) Ferdous Ibna Idrish (082467)

> Supervised by Dr. Md. Fokhrul Islam Co-Supervised by Md. Shahzamal

## SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

AT

ISLAMIC UNIVERSITY OF TECHNOLOGY DHAKA, BANGLADESH 12<sup>th</sup> SEPTEMBER, 2012

## ISLAMIC UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

The thesis entitled "**Remote Data Acquisition System Using FPGA**", by **Husnain Al Bustam, Nafiz Ur Rahman, Ferdous Ibna Idrish** has been accepted in partial fulfillment of the requirement for the degree of **Bachelor of Science in Electrical and Electronic Engineering** on 12.09.2012.

Approved by Dr. Md. Fokhrul Islam

**Dr. Md. Fokhrul Islam** Project Supervisor Department of Electrical & Electronic Engineering (EEE)

**Md. Shahzamal** Project Co-Supervisor Bangladesh Atomic Energy Commission, Bangladesh.

### Prof. Dr. Md. Shahid Ullah

Head of the department Electrical and Electronic Engineering (EEE)

## ISLAMIC UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

Date: 12th September, 2012

It is hereby declared that neither this thesis nor any part thereof has been submitted elsewhere for the award of any degree or diploma.

| Author 1      |                       |

|---------------|-----------------------|

|               | Husnain Al Bustam     |

| Author 2      |                       |

|               | Nafiz Ur Rahman       |

| Author 3      |                       |

|               | Ferdous Ibna Idrish   |

| Supervisor    |                       |

|               | Dr. Md. Fokhrul Islam |

| Co Supervisor |                       |

|               | Md. Shahzamal         |

## TO OUR PARENTS

## ABSTRACT

Single cost-efficient VLSI chip nowadays turns out to be a solution to microelectronic design problems. In these designs embedded system architectures are used which are comprised of software programmable components accompanied with dedicated hardware processing modules integrated into the VLSI chip [1]. Also emerging new designs which are based on heterogeneous embedded system architectures, offer flexible low-cost design in a short design cycle, integrating multiple software programmable components together with dedicated hardware components into a single cost-efficient VLSI chip. With the help of new technology it has now become possible not only to introduce programmability in these single chip architectures but also maintaining most of the advantages of customized VLSI solutions [1]. Once some applications which were too difficult for computing hardware, now with impressive advances in Very Large Scale Integration (VLSI) technology are becoming more feasible<sup>[2]</sup>. Utilizing the prebuilt logic blocks and programmable routing resources engineers and designers now configure FPGAs (FPGA stands for Field Programmable Gate Array) to implement custom hardware. The configuration of FPGA is specified with the help of hardware description language. FPGA technology is now adopting among the engineers scientists at all levels of expertise as higher level tools evolve to deliver the fruits of reprogrammable silicon [2]. The "Remote Data Acquisition System Using FPGA" has been entirely implemented on the FPGA of the Spartan-3E Starter Kit. DAQs are complex systems which are the basis for building and monitoring tools that enable the supervision of local and remote systems. Data is transferred from the data loggers via radio telemetry, cellular, serial ports, Ethernet, satellite peripherals etc. The mobility and flexibility of the data loggers and sensors make the applications of this technology limitless. In everywhere we can see the magical touch of science and engineering in the present world which enables human being to have the maximum comfort and security of life. In that contrast our developed data acquisition system is such a device that could be used for biomedical applications, nuclear research, or data acquisition from such a place where the presence of human being is risky as well as harmful, for the example in the radioactive areas. The

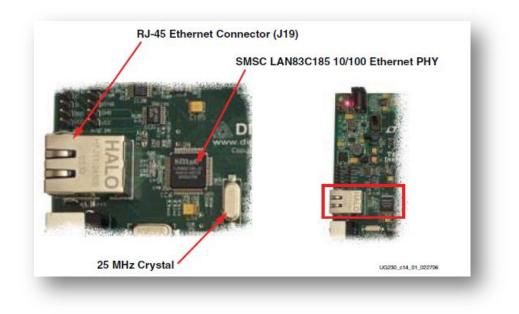

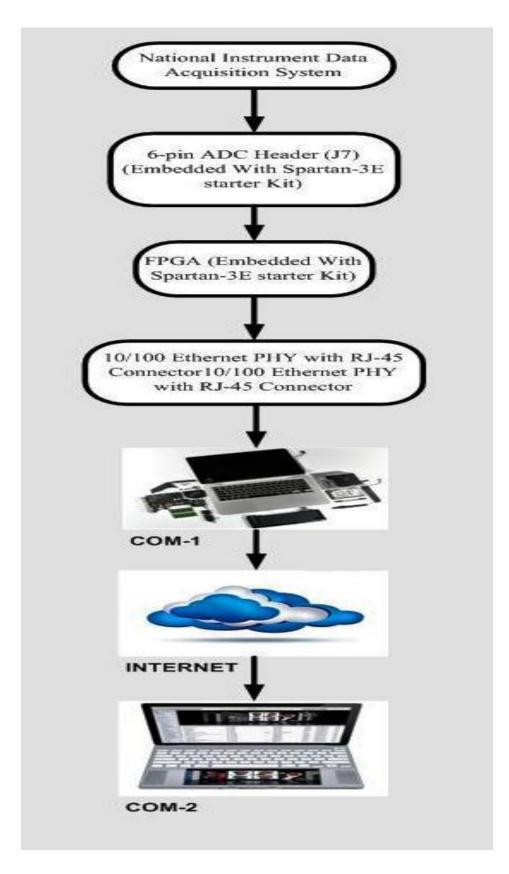

developed system will communicate through the SMSC LAN83C185 Ethernet PHY with remote pc via internet. Of course the Ethernet port of the Spartan-3E starter kit has to be interfaced with the personal computers as well as that pc should be connected with the remote pc through internet. The configuration of the PCs used in this R and D work- Intel® Desktop Board DG41WV mother board which has LAN support Gigabit (10/100/1000 Mbits/sec) LAN subsystem using the Realtek\* RTL8111D Gigabit Ethernet Controller and Intel® Core™2 Duo Processor. The data transfer rate of the Ethernet port of Spartan-3E starter kit is 10/100 Mbits/Sec. So our developed system could transfer data at the rate of 10/100 Mbits/Sec. National instrument DAQ interfaced with the ADC of the Spartan-3E starter kit to acquire analog signal from the outer world. The ADC process the digital data to FPGA, therefore those data is processed through the SMSC LAN83C185 Ethernet PHY to the personal computer of the concerned person who intended to acquire and send that data through internet in a remote place. The graphical control of the system has been developed using the LAB VIEW program.

## ACKNOWLEDGEMENTS

We would like to thank Dr. Md. Fokhrul Islam, our supervisor, for his many suggestions and constant support during this research. We are also thankful to Md. Shahzamal, our co supervisor for his guidance in the theoretical aspects of the research when we were in chaos and confusion. Mr. Tnaveer Ahmed Bhuiyan, an Alumni of AIUB currently researching in University of Texas, Dallas, shared with us his knowledge of speech enhancement and provided many useful references and friendly encouragement. Of course, we are grateful to our parents for their patience and love. Without them this work would never have come into existence (literally).

Finally, we wish to thank the following: Mr. Mahbubul Hoq (Director-IE,AERE), Dr. Carlos *Leitão* (Researcher, GoLP is a research unit, University of Lisbon, Portugal) and all the other friends who gave us love and support.

The Authors

IUT,OIC, Bangladesh September 2012

# **TABLE OF CONTENTS**

## Page

| ACKNOWLEDGEMENT                  | VII  |

|----------------------------------|------|

| LIST OF FIGURES                  | XII  |

| LIST OF TABLES                   | XVI  |

| LIST OF SYMBOLS AND ABBREVIATION | XVII |

#### CHAPTERS

| 1. | Introduction                                         |   |

|----|------------------------------------------------------|---|

|    | 1.1. Background02                                    | 2 |

|    | 1.2. Motivation02                                    | 2 |

|    | 1.3. The Research Goal03                             | ; |

| 2. | Data Acquisition System (DAQ)                        |   |

|    | 2.1. Introduction                                    | ) |

|    | 2.2. Types of DAQ08                                  |   |

|    | 2.2.1. Wireless Data Acquisition Systems09           | ) |

|    | 2.2.2. Serial Communication Data Acquisition Systems | ) |

|    | 2.2.3. USB Data Acquisition Systems09                | ) |

|    | 2.2.4. Ethernet Data Acquisition Systems10           | ) |

|    | 2.3. Data Acquisition Plug-in Boards10               | ) |

|    | 2.4. Switch Boxes11                                  | - |

|    | 2.5. Stand-alone Data Loggers11                      | - |

|    | 2.6. Application of DAQs12                           | 2 |

|    | 2.6.1. Wireless DAQ13                                | ; |

|    | 2.6.2. Ethernet DAQ14                                | • |

|    | 2.6.3. USB DAQ14                                     | ł |

|    | 2.7. Remote DAQ15                                    | 5 |

|    | 2.7.1. Available Remote DAQs16                       | 5 |

|    | 2.7.2. Retriever                                     | 6 |

|    | 2.7.3. Wireless Modem Models                               | 16 |

|----|------------------------------------------------------------|----|

| 3. | CISC Architecture                                          |    |

|    | 3.1. Introduction                                          | 20 |

|    | 3.2. History of CISC Architecture                          | 20 |

|    | 3.3. Attributes of CISC Architecture                       | 22 |

|    | 3.4. Recent Development of CISC Architecture               | 24 |

|    | 3.5. Advantages of CISC Architecture                       | 24 |

|    | 3.6. Disadvantages of CISC Architecture                    | 25 |

|    | 3.7. Application of CISC Architecture                      | 26 |

| 4. | FPGA                                                       |    |

|    | 4.1. Introduction                                          | 28 |

|    | 4.2. History                                               | 28 |

|    | 4.3. FPGA Structures                                       | 29 |

|    | 4.3.1. Basic Structure                                     | 29 |

|    | 4.4. Configuring a FPGA                                    |    |

|    | 4.5. Advantages of FPGA                                    |    |

|    | 4.6. Disadvantages of FPGA                                 |    |

| 5. | Hardware and Software                                      |    |

|    | 5.1. Introduction                                          | 33 |

|    | 5.2. Hardware                                              |    |

|    | 5.2.1. Spartan-3E-starter kit                              |    |

|    | 5.3. USB TO RS232 SERIAL Adapter CABLE DB9 PIN PL2303      | 42 |

|    | 5.3.1. USB TO RS232 SERIAL Adapter CABLE                   | 42 |

|    | 5.4. Software                                              |    |

|    | 5.4.1. VHDL                                                | 43 |

|    | 5.4.2. Lab VIEW                                            | 44 |

|    | 5.4.3. Xilinx 13.2 ISE                                     | 45 |

| 6. | Remote Data Acquisition System                             |    |

|    | 6.1. Interfacing the Peripherals of Spartan-3E Starter Kit | 47 |

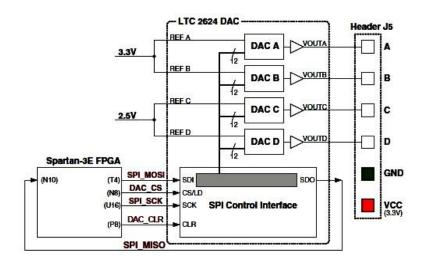

|    | 6.1.1. DAC                                                 | 47 |

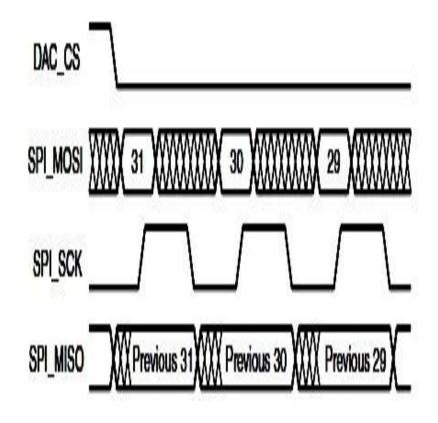

|    | 6.1.2. SPI Communication                                   |    |

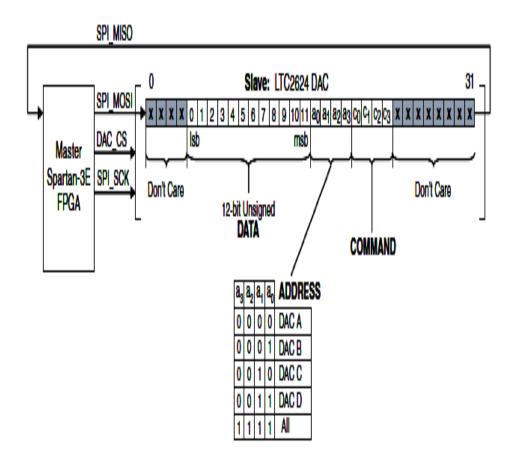

| 6.1.3.      | Communication Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

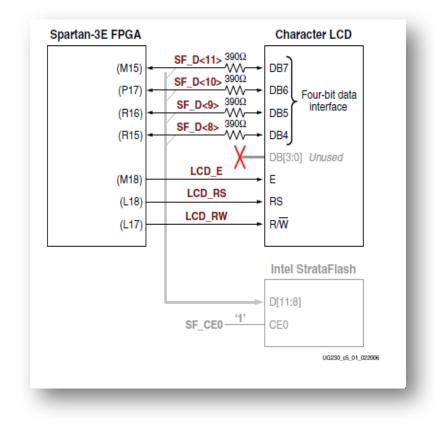

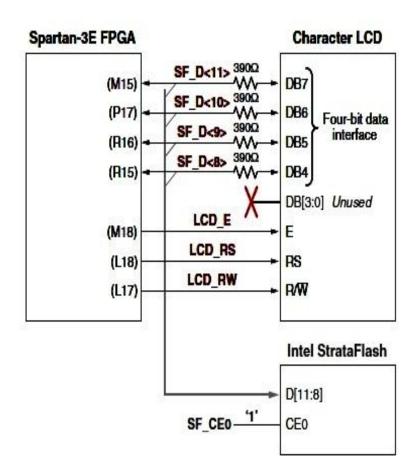

| 6.1.4.      | Character LCD Screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

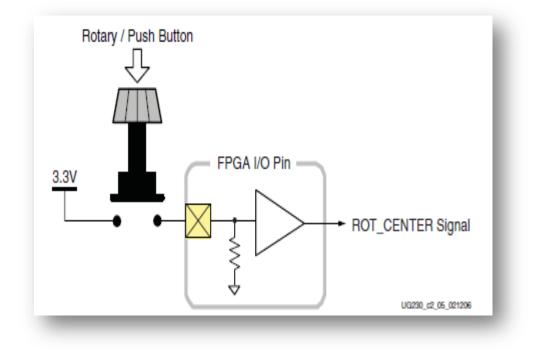

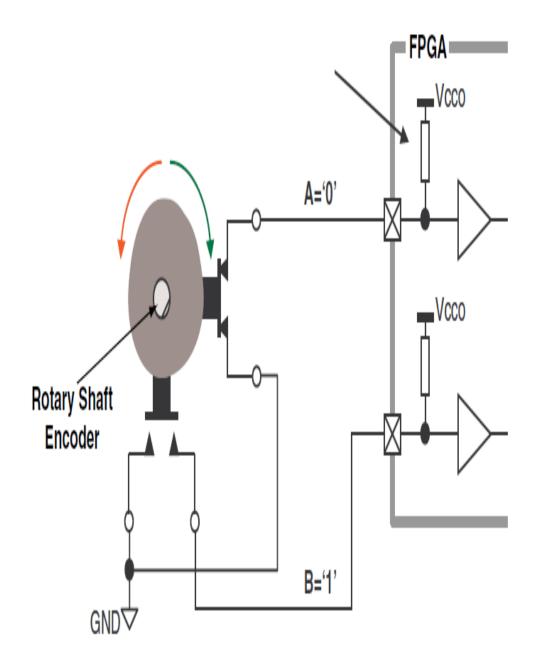

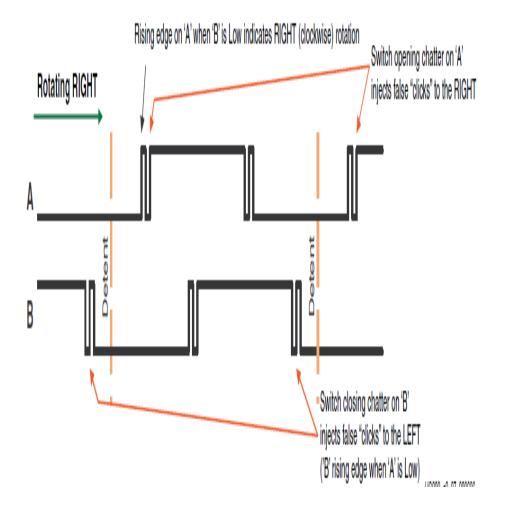

| 6.1.5.      | Rotary Push-Button Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

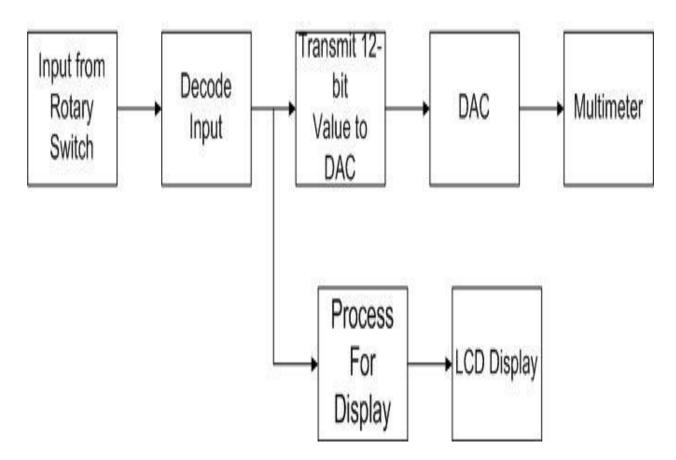

| 6.2. Work   | ring Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3. ADC    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4. Progr  | rammable Pre-Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4.1.      | Programmable Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4.2.      | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4.3.      | SPI Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5. Analo  | og to Digital Converter (ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5.1.      | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5.2.      | SPI Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6. Interf | facing of the Ethernet Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6.1.      | Design Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6.2.      | Open Core Ethernet Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6.3.      | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6.4.      | Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.7. Remo   | ote Data Acquisition System                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Result An   | alysis and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1. Resul  | lt Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

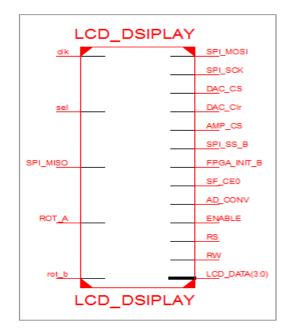

| 7.1.1.      | DAC Implementation on FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

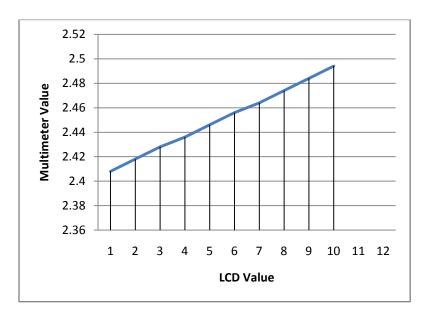

| 7.1.2.      | Tables and Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

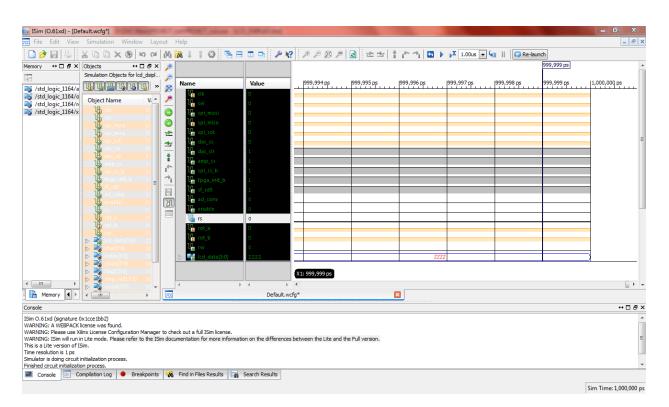

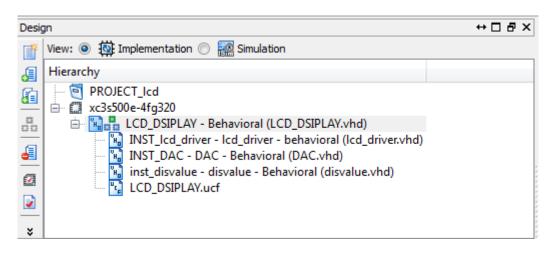

| 7.1.3.      | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2. Meas   | ure Light Intensity using Photodiode                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

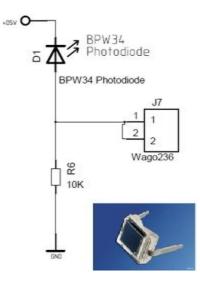

| 7.2.1.      | Photodiode BPW34 as light sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

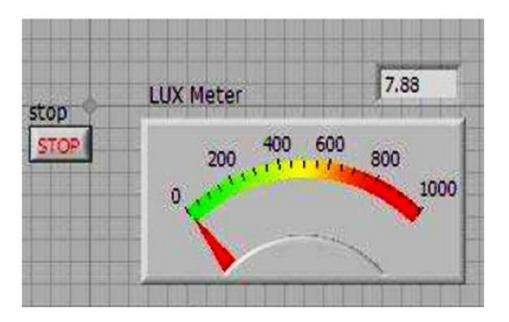

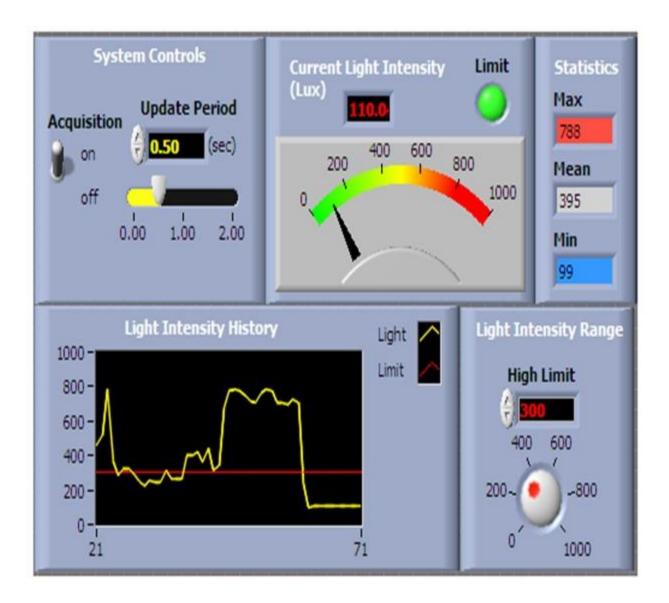

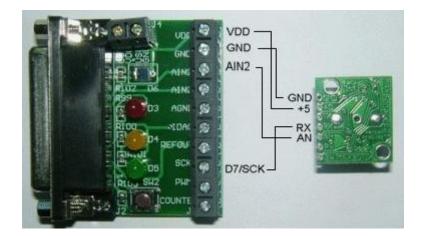

| 7.2.2.      | Build a Light Intensity Logger                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3. Meas   | ure Distance using the Ultrasonic Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.4. Temp   | perature Simulation and Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

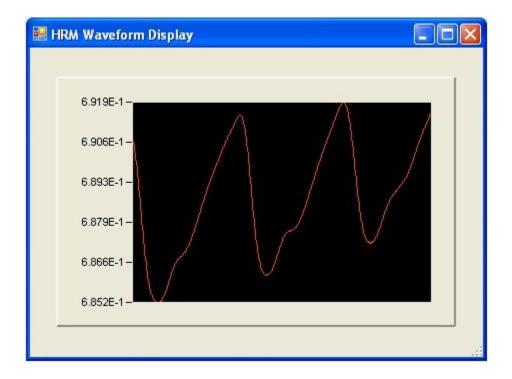

| 7.5. Optic  | al Heart Rate Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.6. Discu  | ission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.6.1.      | DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | <ul> <li>6.1.4.</li> <li>6.1.5.</li> <li>6.2. Work</li> <li>6.3. ADC.</li> <li>6.4. Programing</li> <li>6.4.1.</li> <li>6.4.2.</li> <li>6.4.3.</li> <li>6.5.1.</li> <li>6.5.2.</li> <li>6.6.1.</li> <li>6.6.2.</li> <li>6.6.3.</li> <li>6.6.4.</li> <li>6.7. Remonds</li> <li>7.1.1.</li> <li>7.1.2.</li> <li>7.1.3.</li> <li>7.2. Meass</li> <li>7.2.1.</li> <li>7.2.1.</li> <li>7.2.2.</li> <li>7.3. Meass</li> <li>7.4. Temp</li> <li>7.5. Option</li> <li>7.6. Disconds</li> </ul> | 6.1.3. Communication Protocol.         6.1.4. Character LCD Screen.         6.1.5. Rotary Push-Button Switch.         6.2. Working Principle.         6.3. ADC.         6.4. Programmable Pre-Amplifier         6.4.1. Programmable Gain.         6.4.2. Interface.         6.4.3. SPI Control Interface.         6.5. Analog to Digital Converter (ADC)         6.5.1. Interface.         6.5.2. SPI Control Interface.         6.6.1. Design Strategy.         6.6.2. Open Core Ethernet Controller.         6.6.3. Design.         6.6.4. Host.         6.7. Remote Data Acquisition System.         Result Analysis and Discussion         7.1. BAC Implementation on FPGA.         7.1.1. DAC Implementation on FPGA.         7.1.2. Tables and Figures.         7.1.3. Simulation Results.         7.2.1. Photodiode BPW34 as light sensor.         7.2.2. Build a Light Intensity Logger.         7.3. Measure Distance using the Ultrasonic Sensor.         7.4. Temperature Simulation and Calibration.         7.5. Optical Heart Rate Monitor.         7.6. Discussion         7.6.1. DAC |

| REFERENCES                            | 87  |

|---------------------------------------|-----|

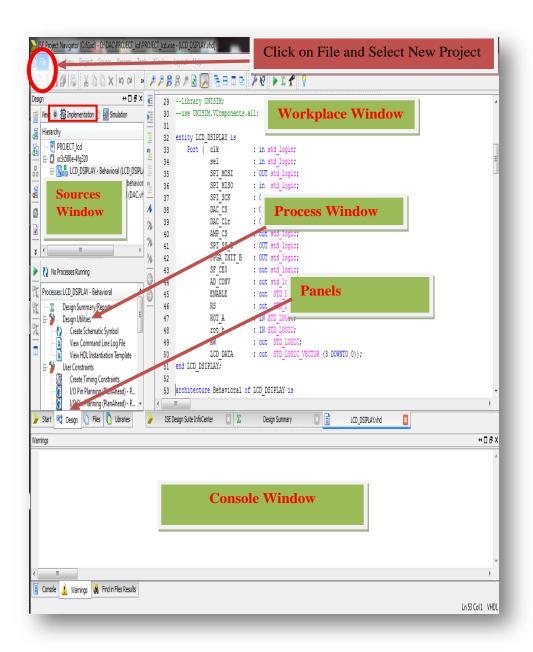

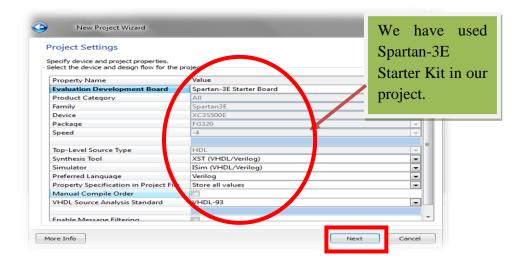

| APPENDIX-I (XILINX-13.2 ISE TUTORIAL) | 94  |

| APPENDIX-II (VHDL TUTORIAL)           | 121 |

| APPENDIX-III (CODES)                  | 134 |

## **LIST OF FIGURES**

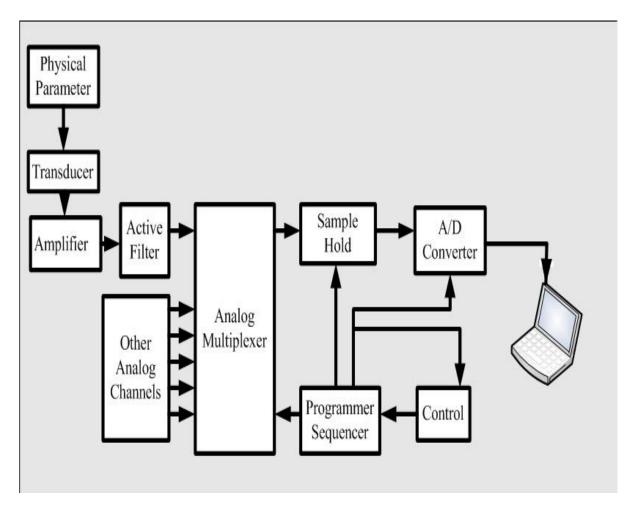

| Figure-2.1. Components of data acquisition system                                    | 07 |

|--------------------------------------------------------------------------------------|----|

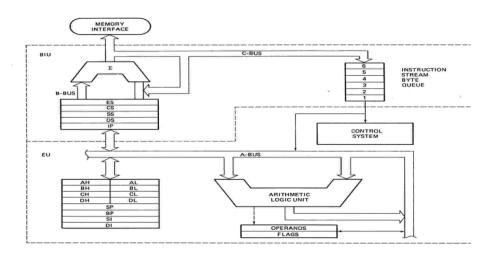

| Figure-3.1. Intel 8086 Architecture, the 1st member of x86 family                    | 23 |

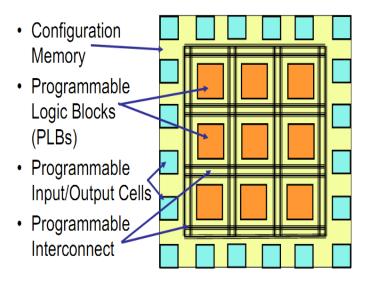

| Figure-4.1. Basic structure of FPGA                                                  | 30 |

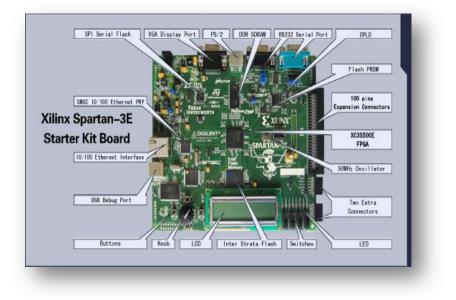

| Figure-5.1. Spartan-3E Starter Kit Board                                             | 36 |

| Figure-5.2. Spartan-3E Starter Kit Board                                             | 36 |

| Figure-5.3. Standard USB Type A/Type B Cable                                         | 37 |

| Figure-5.4. Connect the USB Type B Connector to the Starter Kit Board Connector      | 37 |

| Figure-5.5. 10/100 Ethernet PHY with RJ-45 Connector                                 | 38 |

| Figure-5.6. Character LCD Interface                                                  | 38 |

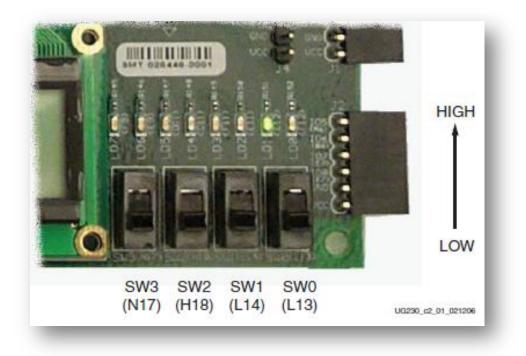

| Figure-5.7. Four Slide Switches and Eight LEDs                                       | 39 |

| Figure-5.8. Push-Button Switches Require Internal Pull-up Resistor in FPGA Input Pin | 39 |

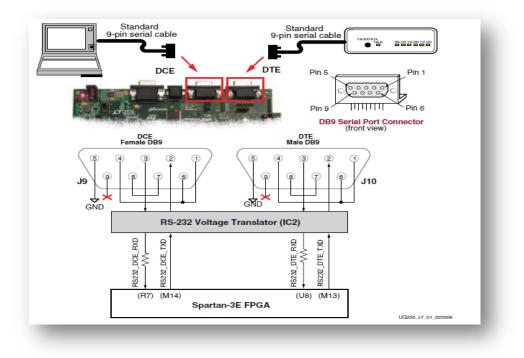

| Figure-5.9. RS-232 Serial Ports                                                      | 40 |

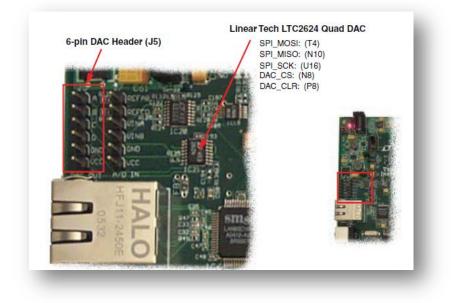

| Figure-5.10. Digital-to-Analog Converter and Associated Header                       | 40 |

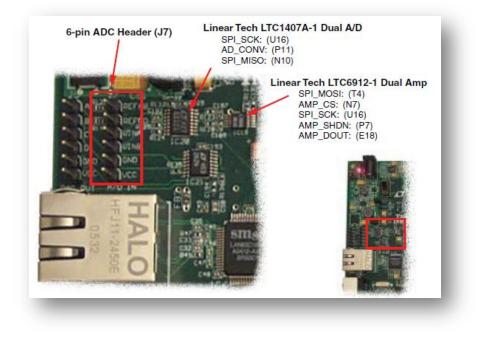

| Figure-5.11. Analog to Digital Converter (Two-Channel Analog Capture Circuit)        | 41 |

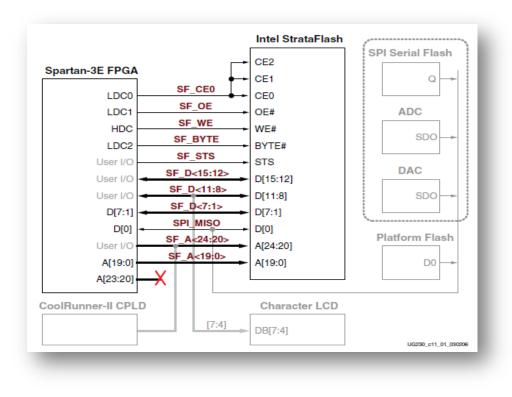

| Figure-5.12. Connections to Intel StrataFlash Flash Memory                           | 41 |

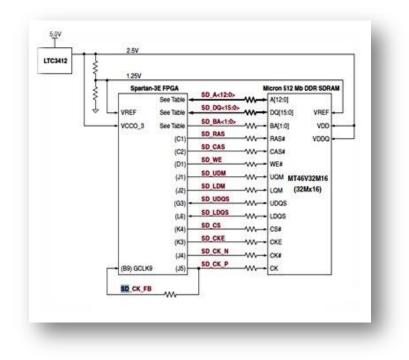

| Figure-5.13. FPGA Interface to Micron 512 Mbit DDR SDRAM                             | 42 |

| Figure-5.14USB TO RS232 Serial cable adapter                                         | 43 |

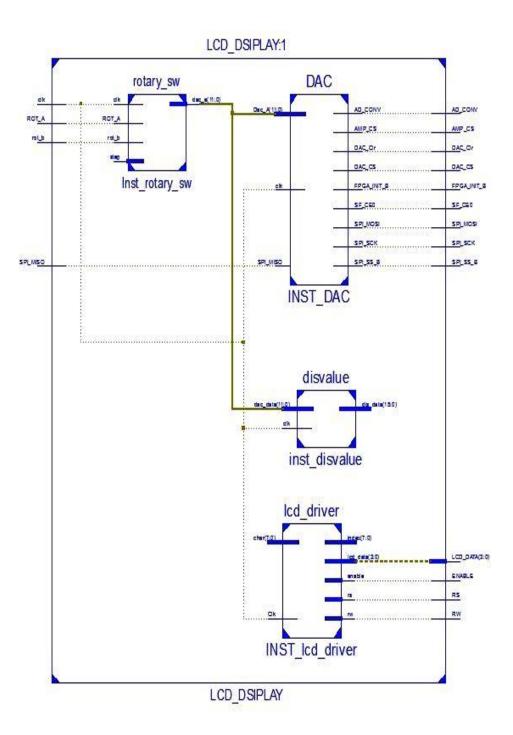

| Figure-6.1. DAC connection schematics                                                | 47 |

| Figure-6.2. SPI communication waveform                                               | 48 |

| Figure-6.3. SPI communication protocol                                               | 49 |

| Figure-6.4. Character LCD interface                                                  | 50 |

| Figure-6.5. Rotary Switch Shaft Encoder Circuitry                                    | 51 |

| Figure-6.6. Output from Rotary Shaft Encoder Circuitry                               | 52 |

| Figure-6.7. Block Diagram of the Developed System                                    | 53 |

| Figure-6.8. Block diagram of the system (Software)                                   | 54 |

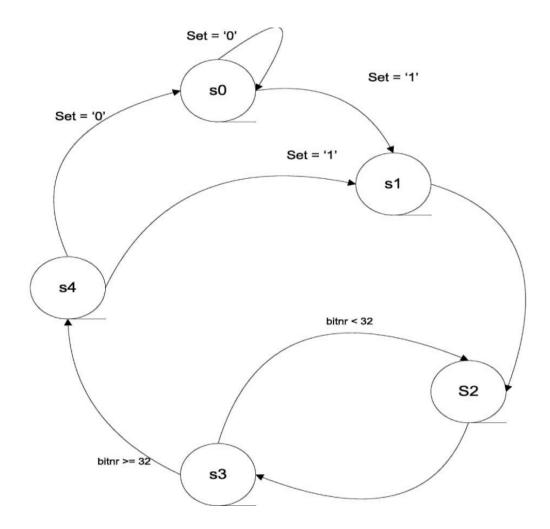

| Figure-6.9. State diagram of the DAC                                                 | 55 |

| Figure-6.10. State diagram of the dis_value component                                | 56 |

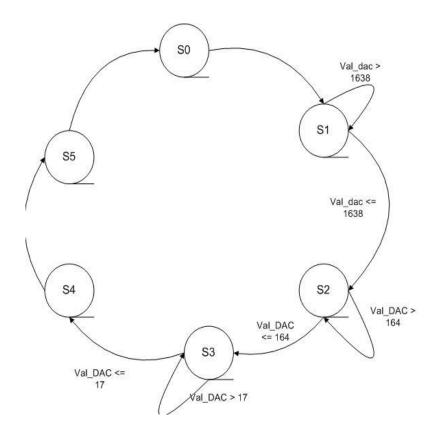

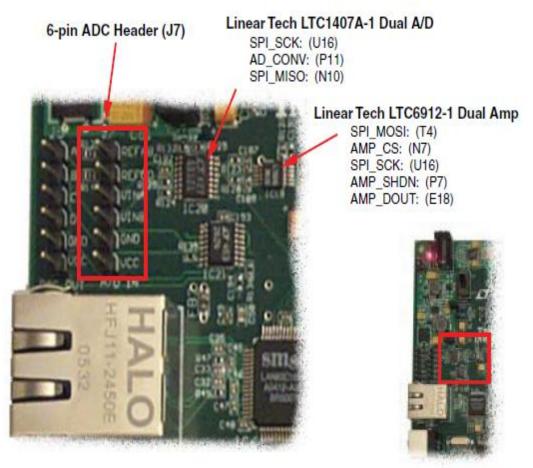

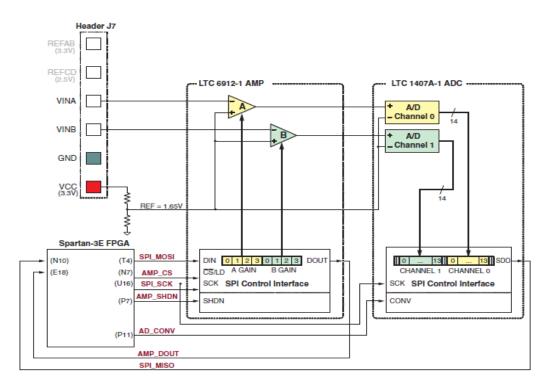

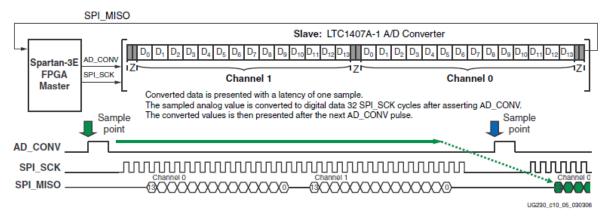

| Figure-6.11. Two-Channel Analog Capture Circuit                                   | 57      |

|-----------------------------------------------------------------------------------|---------|

| Figure-6.12. Detailed View of Analog Capture Circuit                              | 58      |

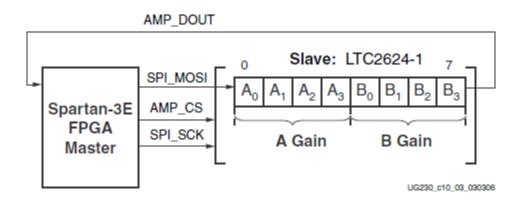

| Figure-6.13. SPI Serial Interface to Amplifier                                    | 60      |

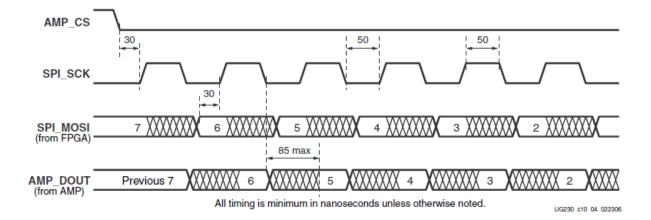

| Figure-6.14. SPI Timing When Communicating with Amplifier                         | 60      |

| Figure-6.15. Analog-to-Digital Conversion Interface                               | 62      |

| Figure-6.16. Detailed SPI Timing to ADC                                           | 62      |

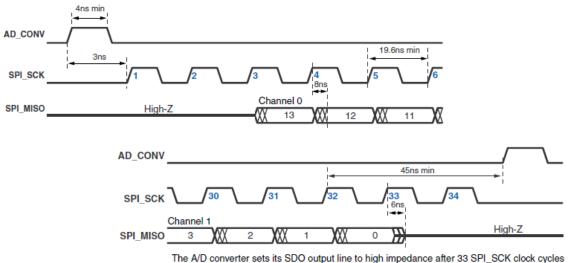

| Figure-6.17. Design Diagram                                                       | 64      |

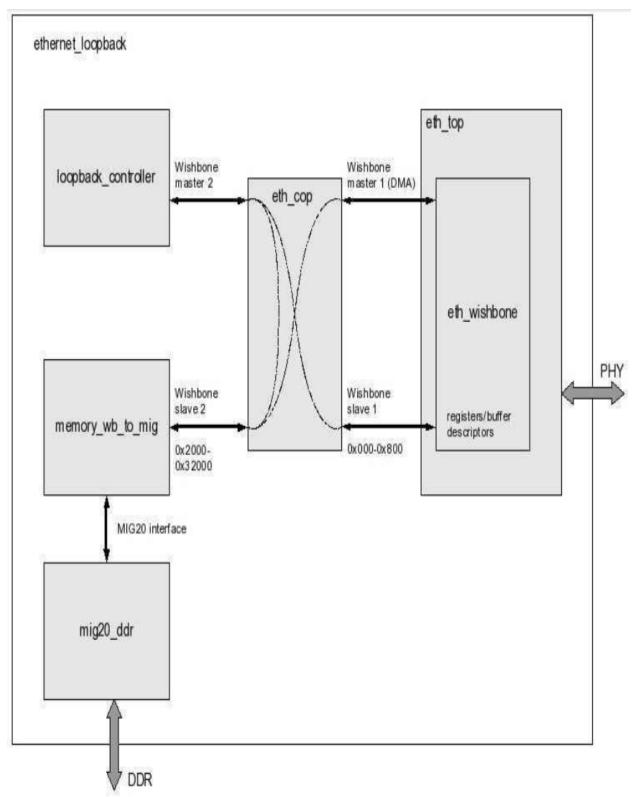

| Figure-6.18. Remote High Speed Data Acquisition System                            | 67      |

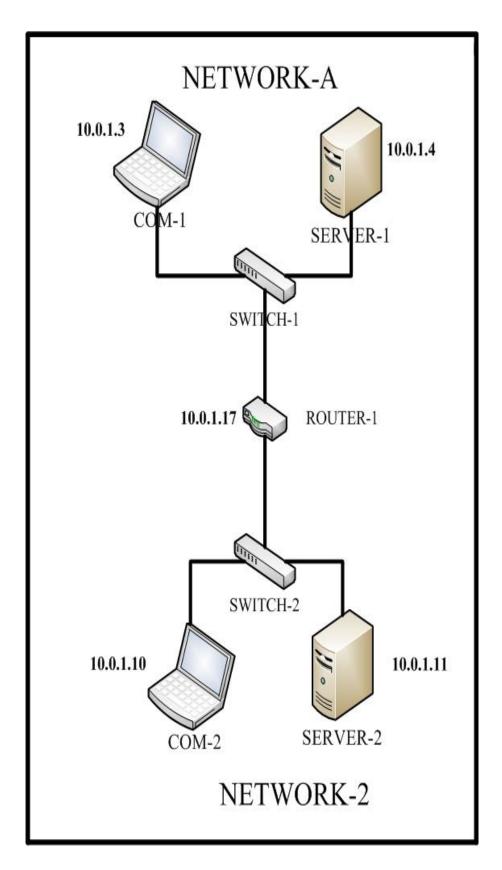

| Figure-6.19. Network Architecture                                                 | 68      |

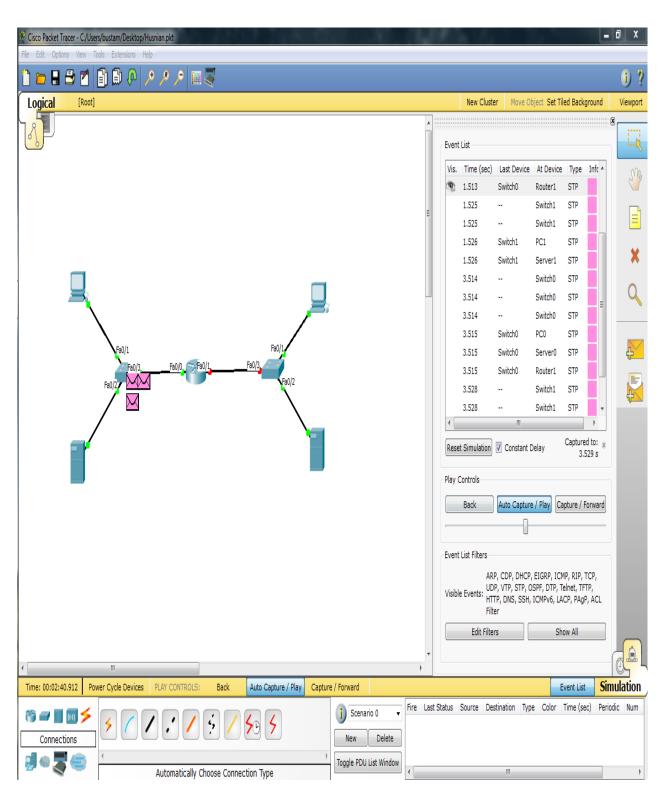

| Figure-6.20. Simulation Using the CISCO Packet Tracer-5.3                         | 70      |

| Figure-7.1. Experimental Setup                                                    | 72      |

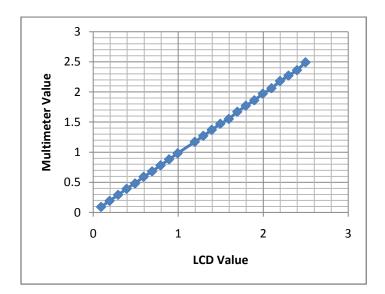

| Figure-7.2. For 100mV                                                             | 74      |

| Figure-7.3. For 10mV                                                              | 75      |

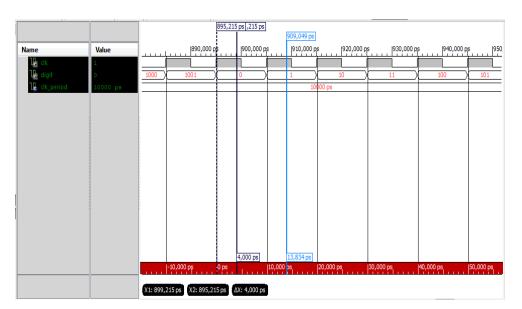

| Figure-7.4. Simulation                                                            | 76      |

| Figure-7.5. Behavioral                                                            | 76      |

| Figure-7.6. RTL Schematic                                                         | 77      |

| Figure-7.7. Design Summary                                                        | 77      |

| Figure-7.8. Photodiode BPW34                                                      | 79      |

| Figure-7.9. Develop a LabVIEW VI that reads the voltage across the resistor and c | onverts |

| the voltage to lux                                                                | 79      |

| Figure-7.10. Front Panel View (Light Intensity Logger)                            | 80      |

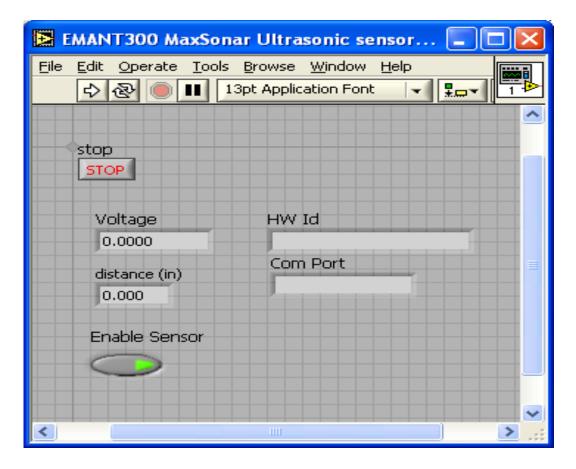

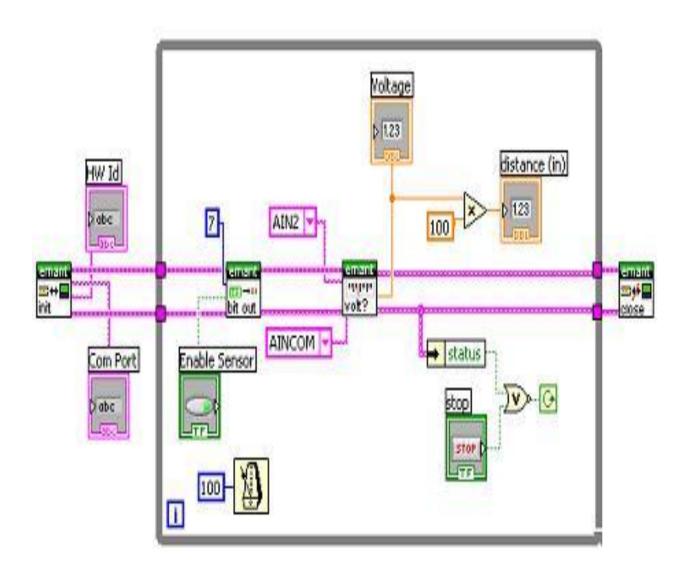

| Figure-7.11. Front View (Ultrasonic Sensor)                                       | 81      |

| Figure-7.12. Block Diagram (Ultrasonic Sensor)                                    | 82      |

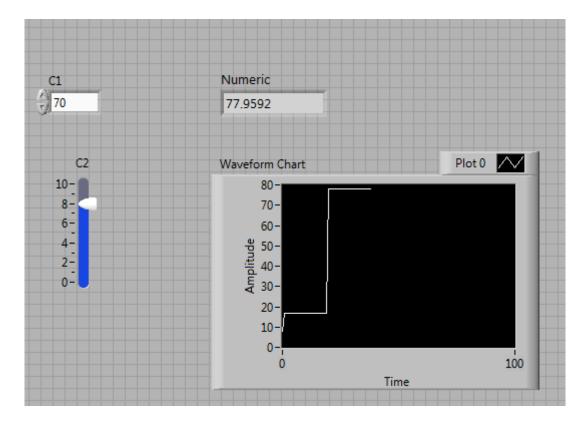

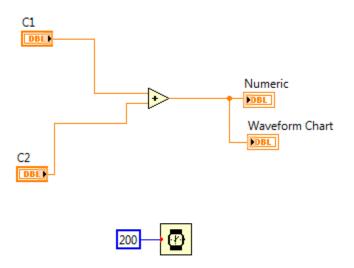

| Figure-7.13. Front Panel View (Temperature)                                       | 83      |

| Figure-7.14. Block Diagram (Temperature)                                          | 83      |

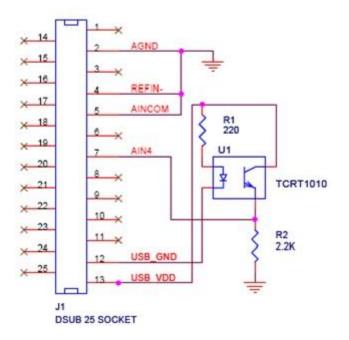

| Figure-7.15. Optical heart rate monitor schematic                                 | 84      |

| Figure-7.16. IR emitter and detector encased in Velcro                            | 85      |

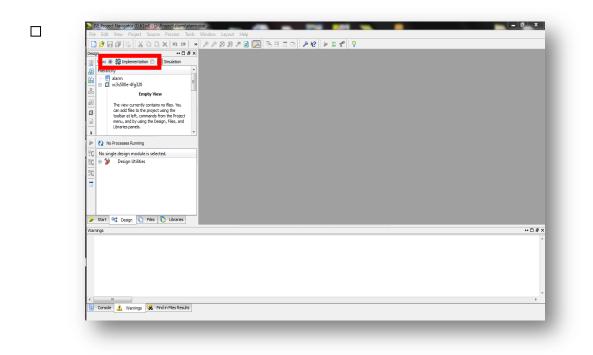

| Figure-A1. ISE Project Navigator (0.61xd)                                         | 88      |

| Figure-A2. Project Navigator Window                                               |         |

| Figure-A3. Creating New Project                                                   | 90      |

| Figure-A4. Creating New Project (Cont.)                                           | 90      |

| Figure-A5. Creating New Project (Cont.)                                        | 91  |

|--------------------------------------------------------------------------------|-----|

| Figure-A6. Creating New Project (Completed)                                    | 92  |

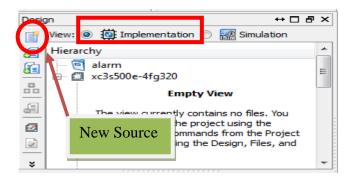

| Figure-A7. Creating New Source                                                 | 92  |

| Figure-A8.New Source Wizard                                                    | 93  |

| Figure-A9.New Source Wizard (Continue)                                         | 93  |

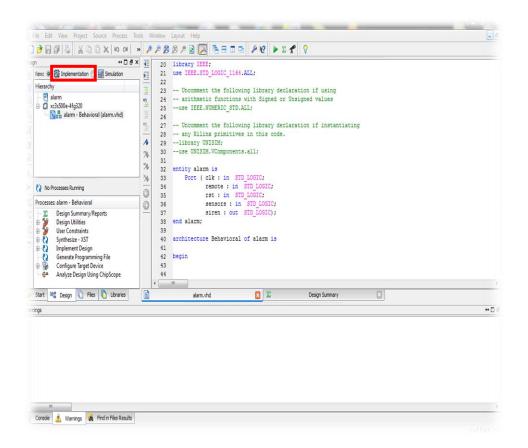

| Figure-A10. Project Navigator Window for the Project "alarm"                   | 94  |

| Figure-A11. Checking Syntax (Successful)                                       | 97  |

| Figure-A12. New Source Wizard (Test Bench)                                     | 97  |

| Figure-A13. New Source Wizard (Test Bench)                                     | 98  |

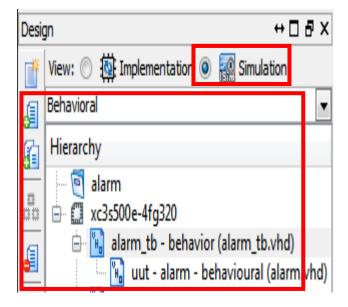

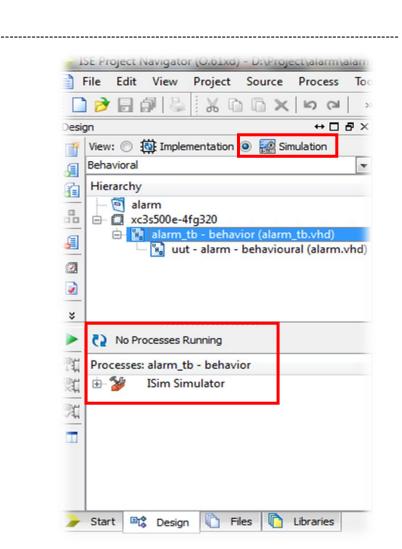

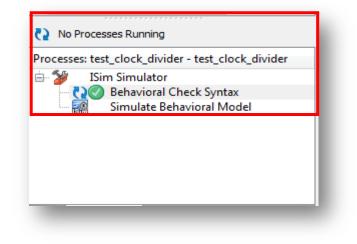

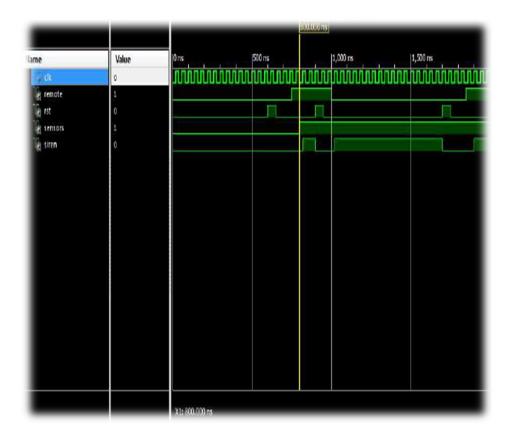

| Figure-A14. Design (Simulation)                                                | 100 |

| Figure-A15. Simulation                                                         |     |

| Figure-A16. Isim Window                                                        | 101 |

| Figure-A17. Expanded User Constraints                                          | 102 |

| Figure-A18. Unconstrained Clocks                                               | 102 |

| Figure-A19. Profile Generated for Clock "CLK"                                  |     |

| Figure-A20. Profile Generated for Clock "REMOTE"                               | 103 |

| Figure-A21. Constrained Clocks                                                 | 104 |

| Figure-A22. Profile Generated After "I/O Planning (Plan Ahead) Post Synthesis" | 105 |

| Figure-A23. Planning I/O Ports constraints                                     |     |

| Figure-A24. ISE iMPACT Window                                                  |     |

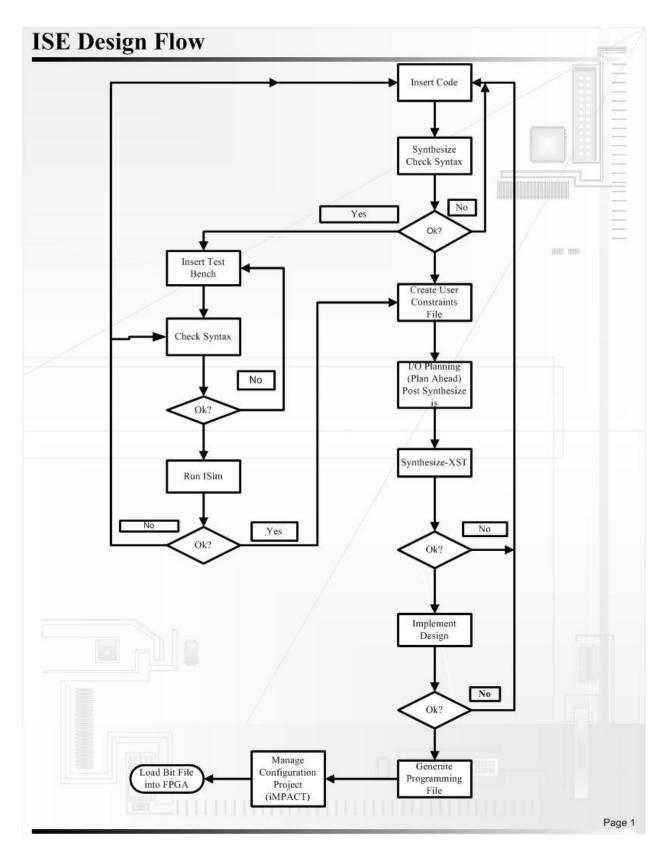

| Figure-A25. ISE Design FlowFigure-A26. Process Window                          | 107 |

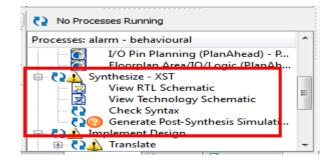

| Figure-A26. Process Window                                                     | 108 |

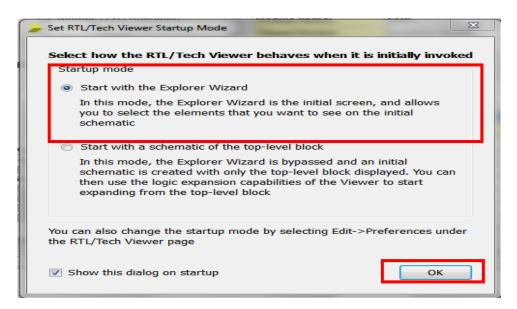

| Figure-A27. Set RTL/Tech Viewer Startup Mode                                   | 108 |

| Figure-A28. "Create RTL Schematic"-Wizard                                      | 109 |

| Figure-A29. "Create RTL Schematic"-Wizard (Continue)                           | 109 |

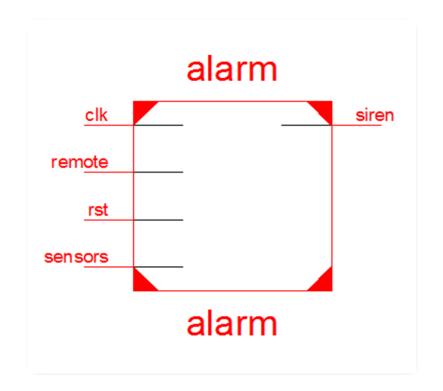

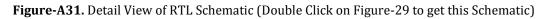

| Figure-A30. RTL Schematic                                                      | 110 |

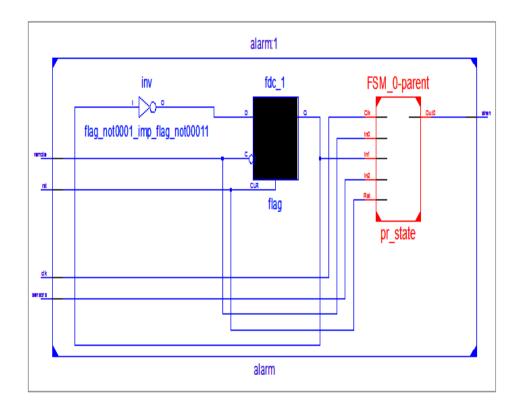

| Figure-A31. Detail View of RTL Schematic                                       | 110 |

| Figure-A32. Set RTL/Tech Viewer Startup Mode                                   | 111 |

| Figure-A33. "Create Technology Schematic"-Wizard                               | 111 |

| Figure-A34. "Create Technology Schematic"-Wizard (Continue)                    | 112 |

| Figure-A35. Technology Schematic                                               | 112 |

| Figure-A36. View of Technology Schematic (Double) |     |

|---------------------------------------------------|-----|

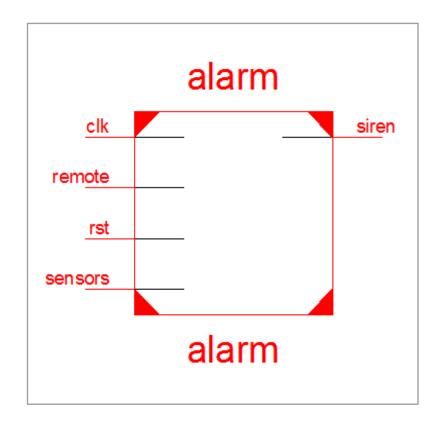

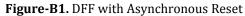

| Figure-B1. DFF with Asynchronous Reset            | 115 |

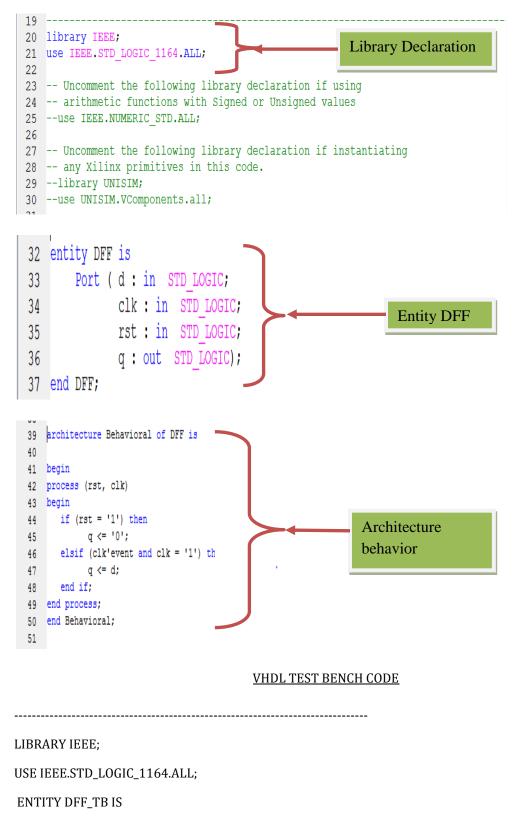

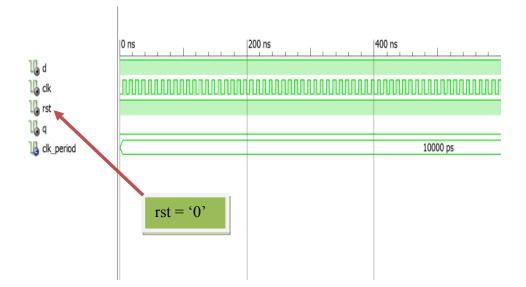

| Figure-B2. When rst= '0', then q<=d               |     |

| Figure-B3. When rst = '1', then q <= '0'          | 119 |

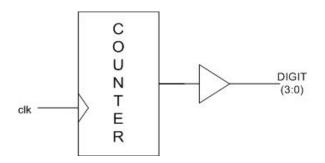

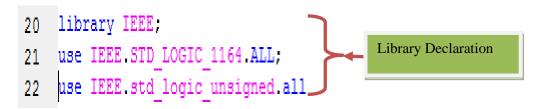

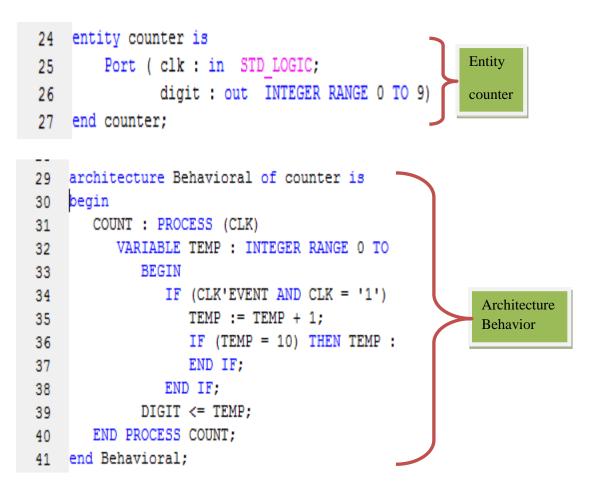

| Figure-B4. Counter of Example-2                   | 119 |

| Figure-B5. Simulation Result                      |     |

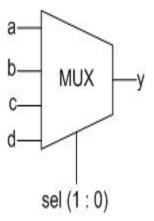

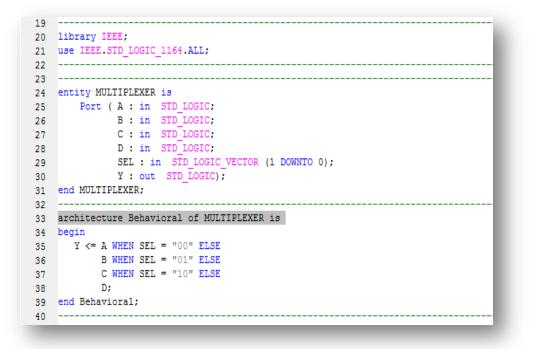

| Figure-B6. 4-input Multiplexer                    |     |

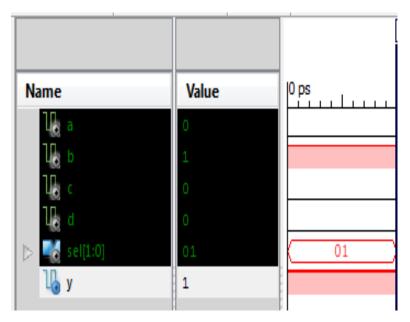

| Figure-B7. Y <= A WHEN SEL = "00"                 |     |

| Figure-B8. Y <= A WHEN SEL = "01"                 |     |

| Figure-B9. Y <= A WHEN SEL = "10"                 |     |

| Figure-B10. Y <= A WHEN SEL = "11"                |     |

# **LIST OF TABLES**

| Table-1. Programmable Gain Settings for Pre-Amplifier | 59 |

|-------------------------------------------------------|----|

| Table-2. AMP Interface Signals                        | 59 |

| Table-3. ADC INTERFACE SIGNALS                        | 61 |

| Table.4. Network Design                               | 69 |

| TABLE -5. FOR 100mV Step                              | 72 |

| TABLE -6. FOR 10mV Step                               | 74 |

# LIST OF SYMBOLS AND ABBREVIATION

| ADC       | Analog to Digital Converter                         |

|-----------|-----------------------------------------------------|

| ASIC      | Application Specific Integrated Circuits.           |

| CISC      | Complex Instruction Set Computer.                   |

| CLBs      | Configurable Logic Blocks                           |

| СРІ       | Clock Per Instruction                               |

| CPLD      | Complex Programmable Logic Device                   |

| DAC       | Digital to Analog Converter                         |

| DAQ/DAS   | Data Acquisition System                             |

| DDS       | Direct Digital Synthesis                            |

|           | Double Data Rate Synchronous Dynamic Random Access  |

| DDR SDRAM | Memory                                              |

| DSP       | Digital Signal Processing                           |

| EEPROM    | Electrically Erasable Programmable Read-Only Memory |

| FSM       | Finite State Machine                                |

| FPGA      | Field Programmable Gate Array                       |

| HDL       | Hardware Description Language                       |

| ICON      | Integrated Controller                               |

| IEEE      | Institute of Electrical and Electronic Engineers    |

| ILA       | Integrated Logic Analyzer                           |

| IP Core   | Intellectual Property Core                          |

| ISE       | Integrated Software Environment                     |

| Lab VIEW  | Libratory Virtual Instrument Workbench.             |

| LAN       | Local Area Network                                  |

| LCD       | Liquid Crystal Display                              |

| LED       | Light Emitting Diode                                |

| LUT       | Lookup Table                                        |

|           |                                                     |

| PLD   | Programmable Logic Devices          |

|-------|-------------------------------------|

| RAM   | Random Access Memory                |

| ROM   | Read-Only Memory                    |

| RTL   | Resistor-Transistor logic           |

| SPI   | Serial Peripheral Interface         |

| SPLDs | Simple PLDs                         |

| SRAM  | Static Random Access Memory         |

| UCF   | User Constraints File               |

| VGA   | Video Graphics Array                |

| VHDL  | VHSIC Hardware Description Language |

| VHSIC | Very High Speed Integrated Circuits |

| VIO   | Virtual Input and Output            |

# CHAPTER 1 INTRODUCTION

#### 1.1. Background

Digital system which is also known by other name such as logic design, digital logic, switching circuits etc. can process only digital signal dealing with only a limited numbers of discreet values [3]. Digital system is characterized by its manipulation of discreet elements of information such as electric impulses, the decimal digits, arithmetic operation, punctuation marks or any other set of meaningful symbols [4]. The subject matter of digital design is the design of digital electronic circuits such as logic gates, flip-flops, shift registers, counters etc. The main application areas of digital design are the digital computers, control systems, data communications and many other applications that require electronic digital hardware. The HDL (Hardware Description Language) is used to describe the behavior of a digital system. As part of course work in "Digital Logic Design" we were given idea about the VHDL (A Hardware Description Language) that raises our interest to work in the field of digital system design on FPGA. While doing industrial training in Institute of Electronics, Bangladesh Atomic Energy Commission we came to know about the FPGA and how to program it. At the end of year, 2011 there was short course on "Digital System Designing on FPGA" in Bangladesh Atomic Energy Commission where for the first time we were introduced with the "Spartan-3E Starter Kit". Our first task was to interface the peripherals such as ADC, DAC, LCD, Rotary Switch, and Push-Button Switch of the Spartan-3E Starter Kit. After that we started thinking of a project and according to the advice of our supervisor and co-supervisor we undertook a project which is almost similar to this project that is, "Data Acquisition System Using FPGA". The main difference between this project and that DAQ is that medium of communication with Personal Computer (PC). This project concerned about the communication using the SMSC LAN 83C185 Ethernet PHY of Spartan-3E Starter Kit while that DAQ communicates via RS-232 Serial Ports.

#### 1.2. Motivation

The Nuclear Electronics Lab, Institute of Electronics (IE), AERE (Atomic Energy Research Establishment) is responsible for developing all electronic equipment for nuclear research. Nuclear research areas are always health threatening in some extents. So in that kind of environment for effective research if we use a data acquisition system it would be worthwhile. This is the primary motivation of our. Besides there are several projects are going on in Energy Institute, AERE which requires data acquisition remotely. There are facilities of Cancer Therapy and many radioactive tests for detection of diseases in AERE which most often require data acquisition. Recently IE has established a VLSI lab which is very first time in Bangladesh opens the new horizon in microelectronic research. So considering all these stated circumstances we have taken this as our undergraduate project. But the main challenge of this work is that we have make the system portable as well as the data communication should be fast. Again Bangladesh is third world country so we think that if we could make data acquisition system locally that will be beneficial for the people of country as well as huge amount money could be saved that we usually spend buying DAQs from outside.

#### **1.3.** The Research Goal