# Nano-Integrable Optical Logic Gate Implementation in Photonic Crystal Waveguide Using Beam Interference Principle

by

Md. Istiac Ahmed (170021069) Mohammed Radoan (170021132) Md. Arefin Rabbi Emon (170021134)

# BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Board Bazar, Gazipur-1704, Bangladesh. May, 2022. © 2022 Md. Istiac Ahmed (170021069) Mohammed Radoan (170021132) Md. Arefin Rabbi Emon (170021134)

All Rights Reserved.

# **CERTIFICATE OF APPROVAL**

The submitted thesis entitled, "**Nano-Integrable Optical Logic Gate Implementation in Photonic Crystal Waveguide Using Beam Interference Principle**" submitted by Md. Istiac Ahmed, St. No. 170021069, Mohammed Radoan, St. No. 170021132, Md. Arefin Rabbi Emon, St. No. 170021134 of Academic Year 2017-18 has been found as satisfactory and accepted as partial fulfillment of the requirement for the Degree BACHELOR OF SCIENCE in ELECTRICAL AND ELECTRONIC ENGINEERING on April 20, 2022.

Approved by:

Md. Farhad Hassan (Supervisor) Assistant Professor, Electrical and Electronic Engineering Department, Islamic University of Technology (IUT), Gazipur.

# **Declaration of Authorship**

We, the authors of this thesis entitled "Nano-Integrable Optical Logic Gate Implementation in Photonic Crystal Waveguide Using Beam Interference Principle", declare that this book and all the findings presented in it are our own. We further confirm that:

- This thesis is submitted as the partial fulfillment of the Bachelor of Science in Electrical and Electronic Engineering degree at Islamic University of Technology (IUT).

- No part of this work has been submitted elsewhere for the award of any Degree or Diploma.

- We have always clearly attributed the sources when we have consulted the published work of others.

Submitted by:

Md. Istiac Ahmed Student ID: 170021069

Mohammed Radoan Student ID: 170021132

Md. Arefin Rabbi Emon Student ID: 170021134

# **Table of Contents**

| Ac | knov   | edgement                                      | xi  |

|----|--------|-----------------------------------------------|-----|

| Ał | ostrac |                                               | xii |

| 1  | Intr   | duction and Background                        | 1   |

|    | 1.1    | Nanophotonics: The Beginning                  | 1   |

|    | 1.2    | Photonic Crystals                             | 2   |

|    |        | 1.2.1 Semiconductor of Light                  | 3   |

|    | 1.3    | Photonic Crystal Applications                 | 4   |

|    |        | 1.3.1 Optical Fibers                          | 4   |

|    |        | 1.3.2 Nanoscopic Lasers                       | 5   |

|    |        | 1.3.3 RF Antennas                             | 5   |

|    |        | 1.3.4 Photonic Crystal Mirrors                | 6   |

|    |        | 1.3.5 Photonic Integrated Circuit             | 6   |

|    |        | 1.3.6 Photonic Crystal LEDs                   | 7   |

|    |        | 1.3.7 Photonic Crystal Sensors                | 7   |

|    |        | 1.3.8 Photonic Crystal Filters                | 8   |

|    | 1.4    | Photonic Crystal Waveguides (PhCWs)           | 8   |

|    |        | 1.4.1 Point Defects                           | 9   |

|    |        | 1.4.2 Line Defects                            | 10  |

|    | 1.5    | Optical Logic Gates using PhCWs               | 11  |

|    | 1.6    | Literature Review                             | 12  |

|    |        | 1.6.1 Plasmonic Waveguide-based Optical Gates | 13  |

|    |        | 1.6.2 PhCW-based Logic Gates                  | 15  |

|    | 1.7    | Thesis Objective                              | 19  |

|    | 1.8    | Thesis Outline                                | 20  |

| 2  | Perf   | rmance Metrics of Optical Logic Gates         | 21  |

|    | 2.1    | Transmission Ratio (TR)                       | 21  |

|    | 2.2    | Contrast Ratio (CR)                           | 21  |

|    | 2.3    | Extinction Ratio (ER)                         | 22  |

| 3  | Bea    | m Inter | rference Principle                                         | 23 |

|----|--------|---------|------------------------------------------------------------|----|

|    | 3.1    | Const   | ructive Interference                                       | 24 |

|    | 3.2    | Destru  | uctive Interference                                        | 25 |

|    | 3.3    | Condi   | tions for Interference                                     | 25 |

|    | 3.4    | Interfe | erence in Photonic Crystal Waveguides                      | 27 |

|    |        | 3.4.1   | Path Difference between Two Input Signals                  | 27 |

|    |        | 3.4.2   | Phase Difference between Two Input Signals                 | 28 |

|    |        | 3.4.3   | Usage of Extra Reference signal                            | 28 |

| 4  | Des    | ign, Op | timization, and Performance Analysis of the Proposed Logic |    |

|    | Gat    | es      |                                                            | 29 |

|    | 4.1    | Struct  | ural Layout and Design Parameters                          | 29 |

|    | 4.2    | Param   | netric Optimization                                        | 30 |

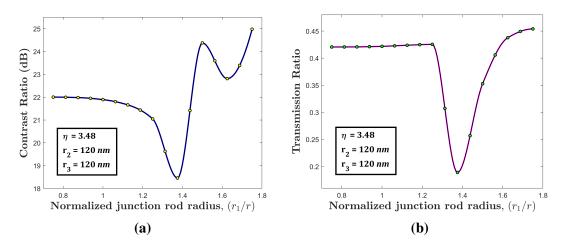

|    |        | 4.2.1   | Junction Rod 1 Radius                                      | 31 |

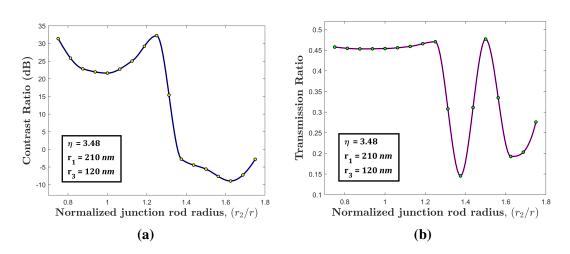

|    |        | 4.2.2   | Junction Rod 2 Radius                                      | 31 |

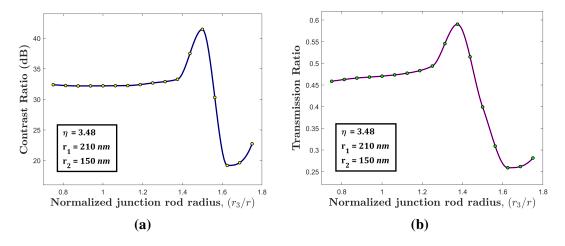

|    |        | 4.2.3   | Junction Rod 3 Radius                                      | 32 |

|    |        | 4.2.4   | Variation of RI of Silicon Rods                            | 33 |

|    |        | 4.2.5   | Optimization Results                                       | 33 |

| 5  | Sim    | ulation | Results                                                    | 34 |

|    | 5.1    | All-op  | ptical AND Logic Gate                                      | 34 |

|    |        | 5.1.1   | Input Combination A=0, B=0                                 | 35 |

|    |        | 5.1.2   | Input Combination A=1, B=0                                 | 35 |

|    |        | 5.1.3   | Input Combination A=0, B=1                                 | 36 |

|    |        | 5.1.4   | Input Combination A=1, B=1                                 | 36 |

|    |        | 5.1.5   | Obtained Truth Table and Transmission Ratio, TR            | 37 |

|    |        | 5.1.6   | Performance Analysis: CR and ER                            | 37 |

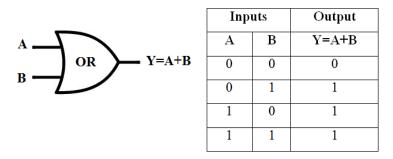

|    | 5.2    | All-op  | ptical OR Logic Gate                                       | 38 |

|    |        | 5.2.1   | Input Combination A=0, B=0                                 | 39 |

|    |        | 5.2.2   | Input Combination A=1, B=0                                 | 39 |

|    |        | 5.2.3   | Input Combination A=0, B=1                                 | 40 |

|    |        | 5.2.4   | Input Combination A=1, B=1                                 | 40 |

|    |        | 5.2.5   | Obtained Truth Table and Transmission Ration, TR           | 41 |

|    |        | 5.2.6   | Performance analysis: CR and ER                            | 41 |

| 6  | Con    | clusion | and Future Works                                           | 43 |

|    | 6.1    | Concl   | usion                                                      | 43 |

|    | 6.2    | Future  | e Works                                                    | 44 |

| Re | eferer | nces    |                                                            | 45 |

# **List of Figures**

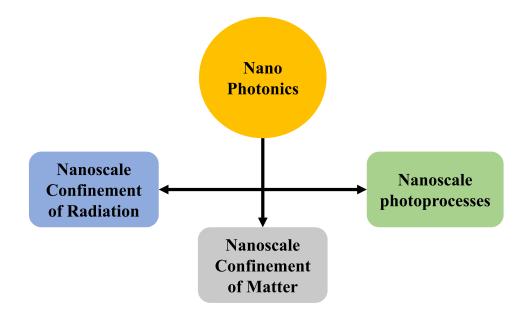

| 1.1  | Branches of nanophotonics [1]                                               | 2  |

|------|-----------------------------------------------------------------------------|----|

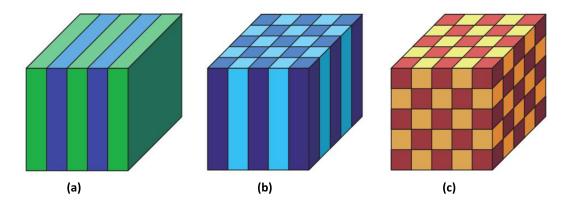

| 1.2  | (a) One dimensional (1D), (b) two dimensional (2D), (c) three dimen-        |    |

|      | sional (3D) photonic crystal [2].                                           | 2  |

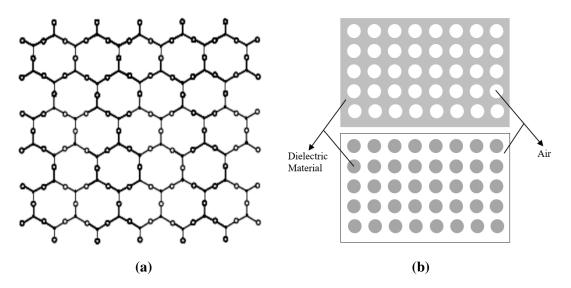

| 1.3  | (a) Crystalline structure of semiconductor (Si) [3]. (b) 2D photonic        |    |

|      | crystal                                                                     | 3  |

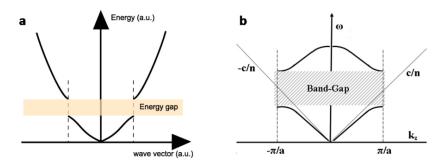

| 1.4  | (a) Semiconductor bandgap. (b) Photonic crystal bandgap [4]                 | 4  |

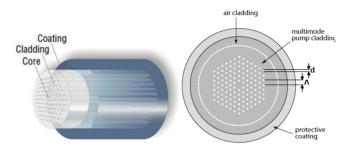

| 1.5  | PCF structure with air cladding [5]                                         | 4  |

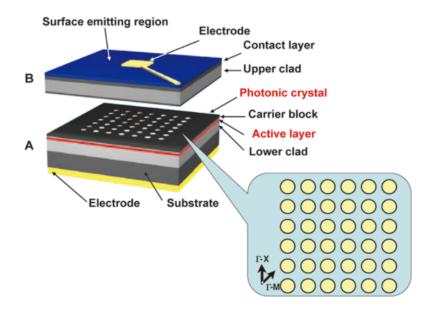

| 1.6  | Photonic crystal laser structure [6]                                        | 5  |

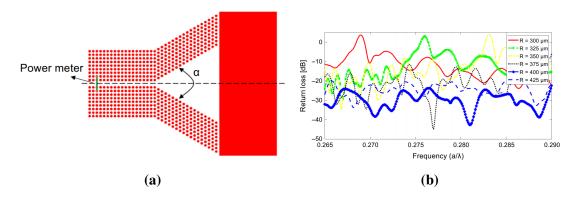

| 1.7  | (a) Proposed RF horn antenna. (b) Return Loss for different hole radius     |    |

|      | [7]                                                                         | 5  |

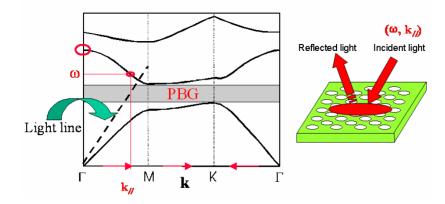

| 1.8  | Operating principle of photonic crystal mirror [8]                          | 6  |

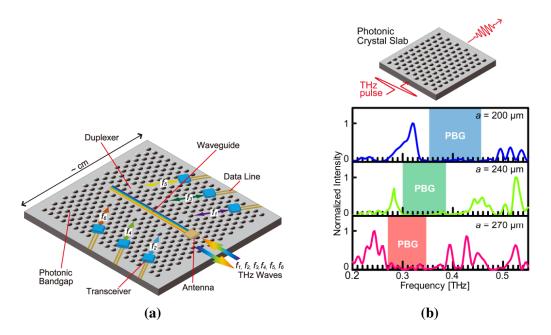

| 1.9  | (a) Schematic of a THz wave IC for a 6-channel photonic crystal fre-        |    |

|      | quency division multiplexing transreceiver. (b) Transmission spectra        |    |

|      | for varying lattice constant, a [9]                                         | 6  |

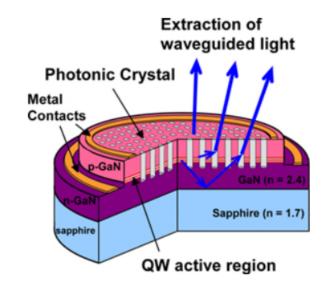

| 1.10 | Photonic crystal incorporation inside an Indium-gallium-nitride (In-        |    |

|      | GaN) LED [10]                                                               | 7  |

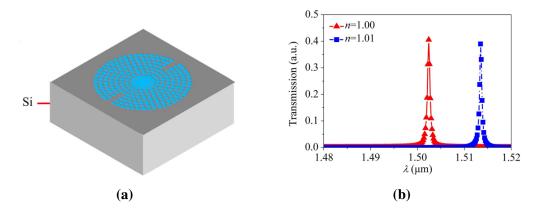

| 1.11 | (a) 3D structure of the photonic crystal cavity sensor. (b) Transmission    |    |

|      | spectra for varying refractive index, $\eta$ [11]                           | 7  |

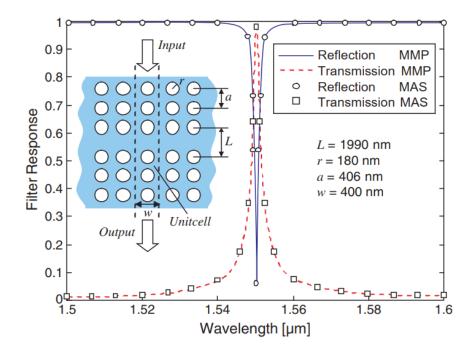

| 1.12 | A PhC slab filter and its output specta [12]                                | 8  |

| 1.13 | Cavity created in a photonic crystal slab through aperiodicity in the       |    |

|      | lattice [13]                                                                | 9  |

| 1.14 | (a) Photonic crystal structure with a point defect. (b) E-field distribu-   |    |

|      | tion and light confinement in the cavity.                                   | 9  |

| 1.15 | Channel waveguide created in a photonic crystal slab through line de-       |    |

|      | fect [13]                                                                   | 10 |

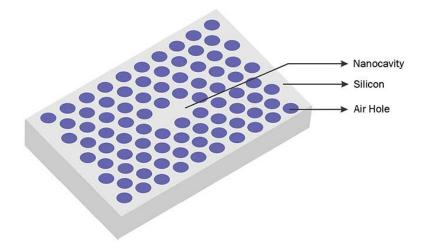

| 1.16 | (a) Photonic crystal structure with a line defect. (b) E-field distribution |    |

|      | and light confinement in the channel waveguide                              | 10 |

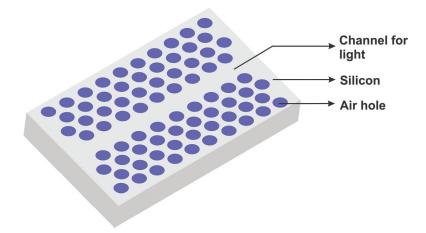

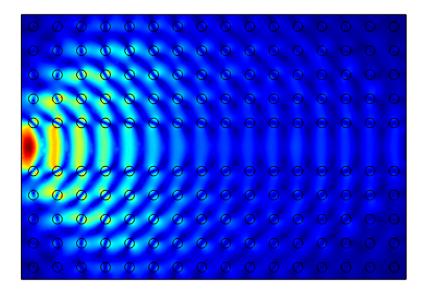

| 1.17 | Propagation loss and leakage through photonic crystal                       | 11 |

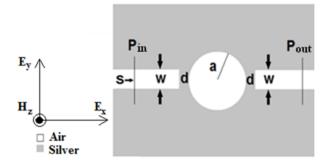

| 1.18 | Basic structure of the nanodisk resonator [14]                              | 13 |

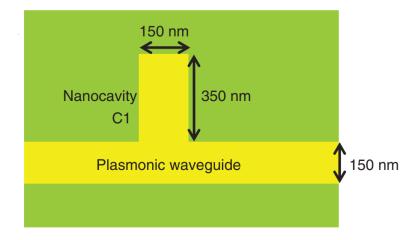

| 1.19 | Schematic of the nonlinear plasmonic nanocavity [15]                        | 14 |

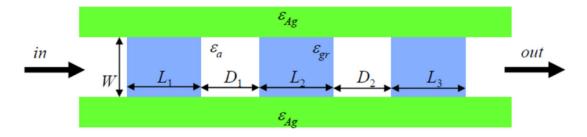

| 1.20 | Schematic of the slot waveguide [16]                                        | 15 |

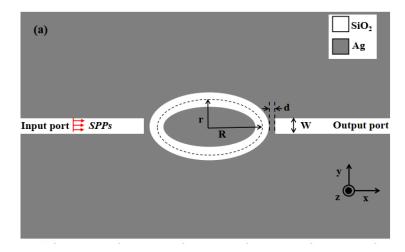

| 1.21                                                                                                                                                      | Proposed elliptical ring resonator [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1.22                                                                                                                                                      | Proposed schematic of 2D silicon PhC [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16                                                                                                                                 |

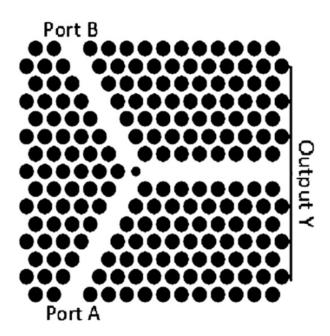

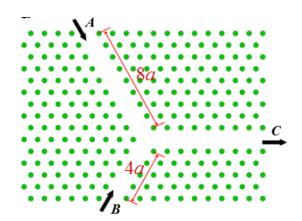

| 1.23                                                                                                                                                      | Proposed Y-shaped structure [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16                                                                                                                                 |

| 1.24                                                                                                                                                      | Schematic of the proposed MMI-based structure [20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                 |

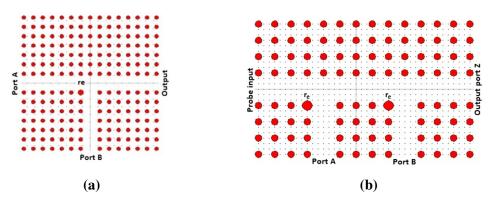

| 1.25                                                                                                                                                      | AND gate (a) with probe input, (b) without probe input [21]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                                 |

| 1.26                                                                                                                                                      | Full adder arrangement [22].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18                                                                                                                                 |

| 1.27                                                                                                                                                      | Proposed XOR/XNOR gate [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                 |

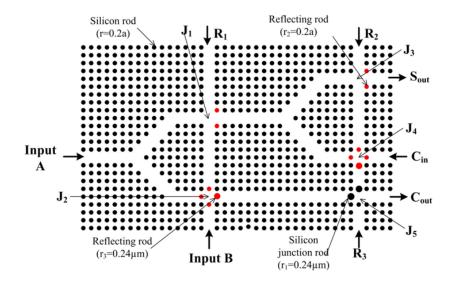

| 1.28                                                                                                                                                      | Schematic of the AOX gate [24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19                                                                                                                                 |

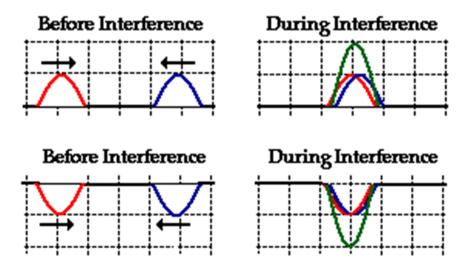

| 3.1                                                                                                                                                       | Constructive interference of upward and downward displacement [25].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                                                                                                 |

| 3.2                                                                                                                                                       | Destructive interference of two symmetrical waves [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                 |

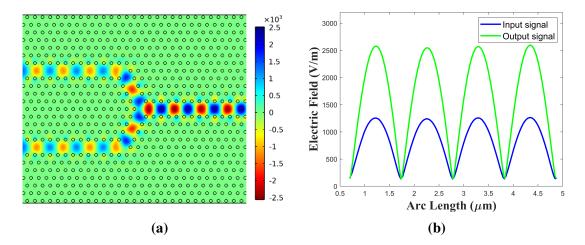

| 3.3                                                                                                                                                       | (a) Constructive interference of two signals, (b) input signal Vs. output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

|                                                                                                                                                           | signal for constructive interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                                                                                                 |

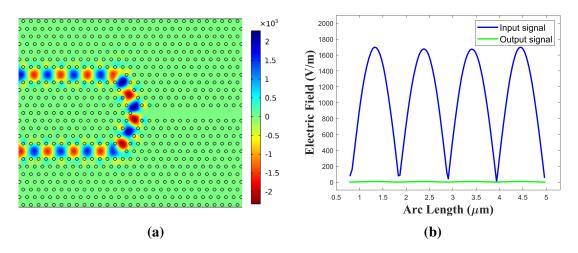

| 3.4                                                                                                                                                       | (a) Destructive interference of two signals, (b) input signal Vs. output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

|                                                                                                                                                           | signal for constructive interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                                                                                                 |

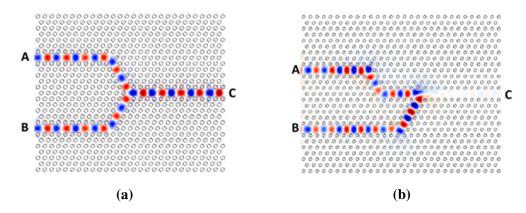

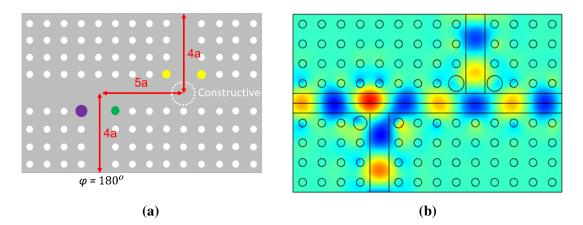

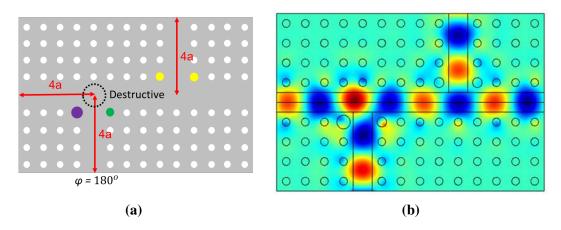

| 3.5                                                                                                                                                       | (a) Constructive interference, (b) destructive interference of input sig-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

|                                                                                                                                                           | nals [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                                                 |

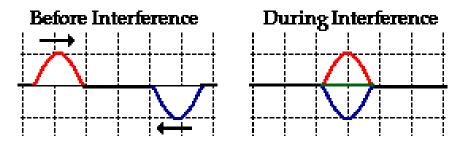

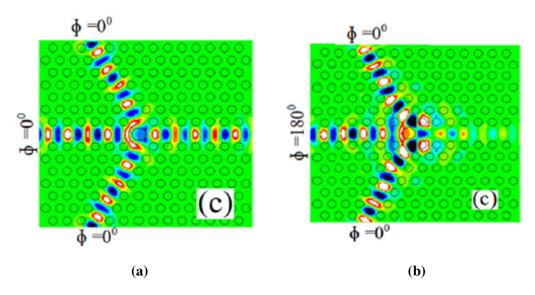

| 3.6                                                                                                                                                       | Using reference signal to vary the mode of operation. (a) Constructive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

|                                                                                                                                                           | interference with $0^{\circ}$ phase-shifted reference signal, (b) destructive in-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

|                                                                                                                                                           | terference with 180° phase-shifted reference signal [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                 |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                                                                                                 |

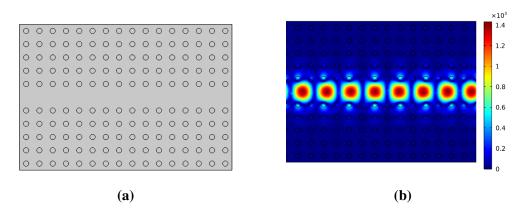

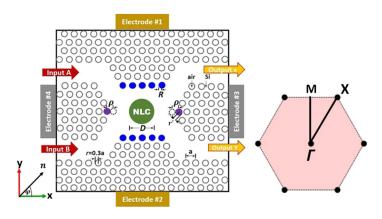

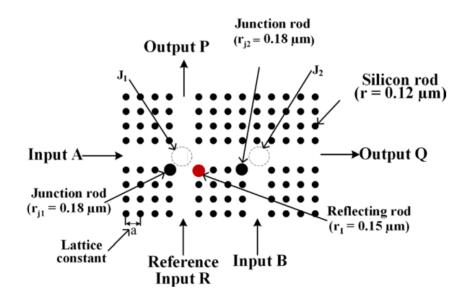

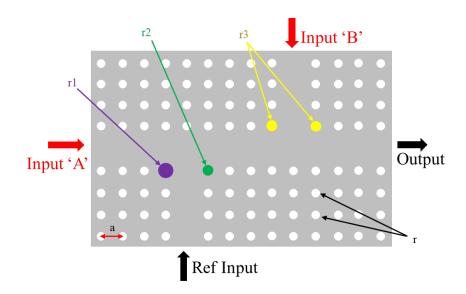

| 4.1                                                                                                                                                       | Two-dimensional (2D) model of the proposed logic gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                                 |

| 4.1<br>4.2                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |

|                                                                                                                                                           | Two-dimensional (2D) model of the proposed logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                 |

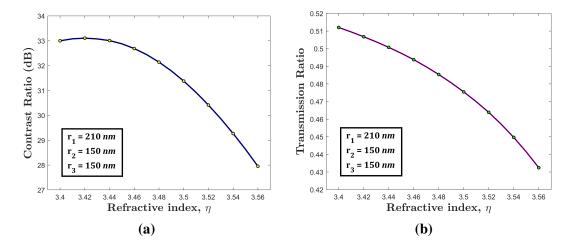

| 4.2                                                                                                                                                       | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29<br>31                                                                                                                           |

| 4.2<br>4.3                                                                                                                                                | Two-dimensional (2D) model of the proposed logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>31<br>31                                                                                                                     |

| 4.2<br>4.3<br>4.4                                                                                                                                         | Two-dimensional (2D) model of the proposed logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>31<br>31<br>32                                                                                                               |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                                                                                 | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29<br>31<br>31<br>32<br>33                                                                                                         |

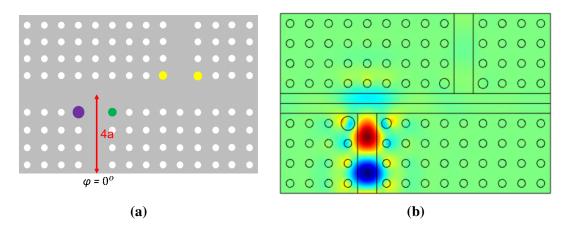

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> </ul>                                                                               | Two-dimensional (2D) model of the proposed logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>31<br>31<br>32<br>33                                                                                                         |

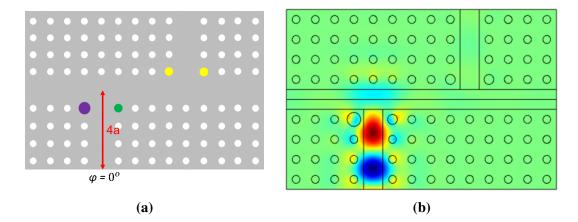

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> </ul>                                                                               | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of $R_1$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of $R_1$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of $R_1$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of $R_1$ , $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>31<br>31<br>32<br>33<br>34                                                                                                   |

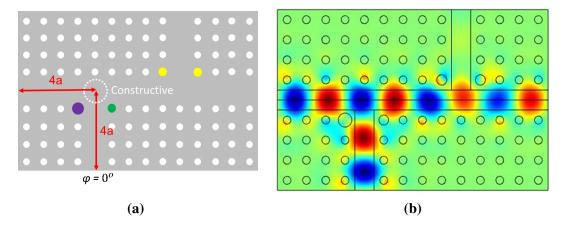

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> </ul>                                                                  | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of $RI$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of $RI$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of $RI$ , $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29<br>31<br>31<br>32<br>33<br>34                                                                                                   |

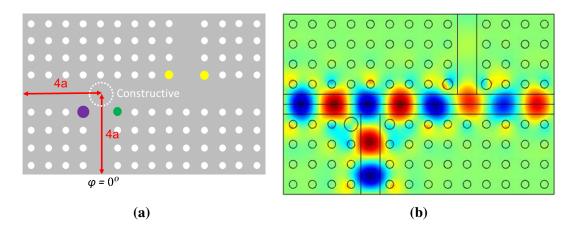

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> </ul>                                                                  | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of $RI$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> </ul>                                     |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul>                                                     | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of $RI$ , $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> </ul>                                     |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul>                                                     | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=1 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b)                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> </ul>                         |

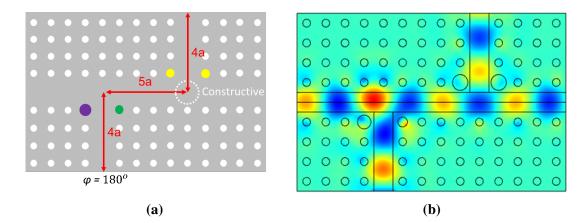

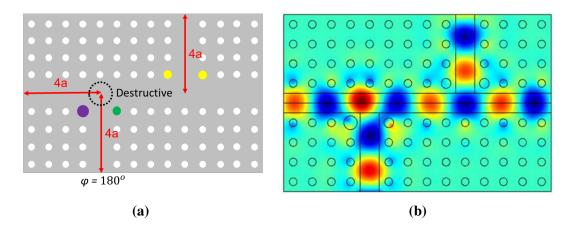

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                                        | Two-dimensional (2D) model of the proposed logic gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> </ul>                         |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                                        | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=1 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=1 AND B=0 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=1 (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) corresponding electric field distribution for A=0 AND B=1 | <ul> <li>29</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> <li>36</li> </ul>                         |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>                           | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>29</li> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> </ul> |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul>              | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>29</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ul> |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ul> | Two-dimensional (2D) model of the proposed logic gate (a) Contrast ratio, (b) transmission ratio for the variation of $r_1$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_2$ (a) Contrast ratio, (b) transmission ratio for the variation of $r_3$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$ (a) Contrast ratio, (b) transmission ratio for the variation of RI, $\eta$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>29</li> <li>31</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> </ul> |

| 5.9  | (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) |    |

|------|-------------------------------------------------------------------------------|----|

|      | corresponding electric field distribution for A=1 OR B=0                      | 39 |

| 5.10 | (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) |    |

|      | corresponding electric field distribution for A=0 OR B=1                      | 40 |

| 5.11 | (a) Path covered by the input signals in terms of lattice constant, $a$ , (b) |    |

|      | corresponding electric field distribution for A=1 OR B=1                      | 40 |

|      |                                                                               |    |

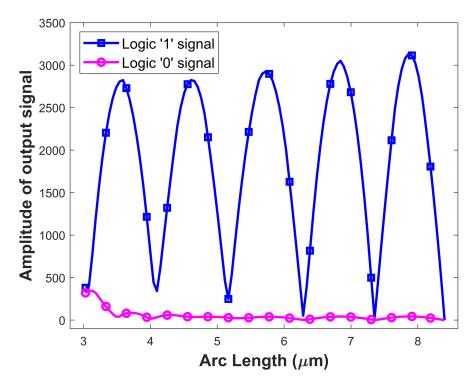

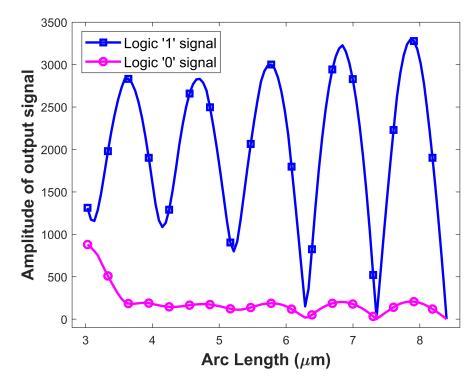

5.12 Line plot of waveguide signal for logic '1' and logic '0' (OR gate). . . 41

# **List of Tables**

| 1.1 | ON/OFF Ratio for Nanodisk Resonator Gates                            | 14 |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Contrast Ratio for the Gates                                         | 17 |

| 1.3 | Contrast Ratio for AOX Gates                                         | 19 |

| 3.1 | Conditions for Constructive and Destructive Interference             | 27 |

| 4.1 | Structural Parameters for the Proposed Logic Gate                    | 30 |

| 4.2 | Structural Parameters and Performance Results for the Proposed Logic |    |

|     | Gate                                                                 | 33 |

| 5.1 | Obtained Truth Table and TR for AND gate                             | 37 |

| 5.2 | Obtained Truth Table and TR for OR gate                              | 41 |

| 6.1 | Comparative Analysis of the Recent All-optical Logic Gates           | 44 |

# List of Abbreviations

| PhCs   | Photonic Crystals                            |  |  |  |  |  |  |  |

|--------|----------------------------------------------|--|--|--|--|--|--|--|

| FEM    | Finite Element Method                        |  |  |  |  |  |  |  |

| dB     | Decibel                                      |  |  |  |  |  |  |  |

| PCF    | Photonic Crystal Fiber                       |  |  |  |  |  |  |  |

| EM     | Electromagnetic                              |  |  |  |  |  |  |  |

| RF     | Radio Frequency                              |  |  |  |  |  |  |  |

| LED    | Light Emitting Diode                         |  |  |  |  |  |  |  |

| PCCS   | Photonic Crystal Cavity Sensor               |  |  |  |  |  |  |  |

| PhCWs  | Photonic Crystal Waveguides                  |  |  |  |  |  |  |  |

| PBGs   | Photonic Band Gaps                           |  |  |  |  |  |  |  |

| PhCRRs | Photonic Crystal Ring Resonators             |  |  |  |  |  |  |  |

| SOA    | Semiconductor Optical Amlifier               |  |  |  |  |  |  |  |

| MMI    | Multi-mode Interference                      |  |  |  |  |  |  |  |

| MZI    | Mach-Zehnder Interferometer                  |  |  |  |  |  |  |  |

| ENIAC  | Electronic Numerical Integrator And Computer |  |  |  |  |  |  |  |

| SPP    | Surface Plasmon Polariton                    |  |  |  |  |  |  |  |

| MIM    | Metal Insulator Metal                        |  |  |  |  |  |  |  |

| IMI    | Insulator Metal Insulator                    |  |  |  |  |  |  |  |

| ERR    | Elliptical Ring Resonator                    |  |  |  |  |  |  |  |

| BPSK   | Binary Phase Shift Keying                    |  |  |  |  |  |  |  |

| TR     | Transmission Ratio                           |  |  |  |  |  |  |  |

| CR     | Contrast Ratio                               |  |  |  |  |  |  |  |

| ER     | Extinction Ratio                             |  |  |  |  |  |  |  |

| RI     | Refractive Index                             |  |  |  |  |  |  |  |

| IC     | Integrated Circuit                           |  |  |  |  |  |  |  |

|        | 5                                            |  |  |  |  |  |  |  |

# Acknowledgment

"All praise and gratitude be to Allah, the most beneficent, the most merciful."

We can never deny the endless mercy bestowed upon us by the Almighty Allah (SWT). At the very beginning, therefore, we express our deepest gratitude to the Almighty for granting us the wisdom and capability to reach this far with the successful completion of this work. Alhamdulillah for everything!

We are grateful to our supervisor Md. Farhad Hassan, Assistant professor, Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT), for introducing us to the realm of research. His guidance, constant assistance, and knowledge have always inspired us to attain the best possible work. We appreciate him for making us relaize the importance of self-learning.

We are in debt to Dr. Rakibul Hasan Sagor, Associate professor, Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT). He was always kind enough to share his invaluable opinions and directions throughout our journey of academic and research.

We would like to specially mention Infiter Tathfif, Lecturer, Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT), for sharing his research experience. His diverse and phenomenal research works have inspired us to look into new sectors of photonics.

To conclude we would like to mention our parents as it was never possible to achieve our goals without their mental support.

# Abstract

Optical logic gates are the best alternative to low-speed semiconductor-based integrated circuitry. Attractive features like small size, ultrahigh speed, tunability, reduced power consumption, and high selectivity have raised the demand for optical gates to a greater extent. By now research has ensured a promising field for optics-based technologies. However, the best logic gate arrangement is yet to be developed. In this work, a highly efficient photonic crystal waveguide-based structure has been proposed to implement all-optical AND-OR gates. The proposed structure implies the beam interference principle to carry out the logic operations. The proposed structure has a dimension of  $8.4 \times 5.4 \ \mu m^2$  with silicon nanorods embedded in the air background. Numerical analysis has been done using the Finite Element Method (FEM) in COM-SOL Multiphysics software. Performance analysis shows that the optimized structural parameters give a high contrast ratio of 41.24 dB and 30.17 dB for OR and AND gates, respectively. Also, the extinction ratio has been found as high as 37.51 dB and 25.21 dB for OR and AND gates, respectively. These values have surpassed most of the recent works of all-optical logic gates. Simple design, high-performance factors, and compact size make the structure a suitable choice for on-chip integration.

# **Chapter 1**

# **Introduction and Background**

# **1.1** Nanophotonics: The Beginning

Back in the previous century, technologists put their utmost effort into reducing the device dimension. Along with gigantic size, the valve-based circuitry came with low operating speed. And the speed was also affected by continuous heating and delayed response. However, with the advent of semiconductor circuitry, it became possible to reduce the device dimension significantly to nm range. Nano-integrable semiconductor circuitry could attain GHz speed and offered transistor technologies. The underlying principle in semiconductors is to control the electron properties utilizing energy bands.

However, networking and communication applications demand higher operating speeds. Therefore, optical devices have become an attractive choice as it was always desirable to attain optical speed. Another reason for this is that the semiconductor technology is assumed to be limited due to heat dissipation difficulties in microchips [28]. It took a long time to develop a technology that can fusion light and nanodevices. Thus nanophotonics has made it possible to achieve both high speed and smaller dimensions. Nanophotonics is a multi-branch sector (Fig.1.1) offering different integration approaches [29].