06 October 2023 (Afternoon)

## ISLAMIC UNIVERSITY OF TECHNOLOGY (IUT) ORGANISATION OF ISLAMIC COOPERATION (OIC) Department of Computer Science and Engineering (CSE)

MID SEMESTER EXAMINATION DURATION: 1 HOUR 30 MINUTES WINTER SEMESTER, 2022-2023 FULL MARKS: 75

## CSE 4305: Computer Organization and Architecture

Programmable calculators are not allowed. Do not write anything on the question paper. Answer all <u>3 (three) questions</u>. Figures in the right margin indicate full marks of questions whereas corresponding CO and PO are written within parentheses.

Dynamic Random Access Memory (DRAM) is a common type of computer memory used for temporary data storage. Several key steps are involved in performing a read operation in a DRAM module.

Figure 1: Timing Diagram of a DRAM read operation for Question 1

- a) Explain the key steps of DRAM read operation based on the timing diagram represented in Figure 1. Draw another timing diagram for the DRAM write operation showing all key steps. (COI)

- (PO1)

- b) Explain the total access time (T<sub>1</sub>) required to respond to a read or write request based on the timing diagram given in Figure 1. What is the next job of a DRAM chip after performing the read operation? Explain the necessity of this task and its execution. Assume that this task requires T<sub>1</sub> time.

- c) Given the information in Question 1.b), what is the memory cycle time if T<sub>1</sub> is 60ns and T<sub>2</sub> is 40ns? What is the maximum data rate supported by this DRAM, presuming a 1-bit output? What data transfer rate can be achieved by implementing a 32-bit wide memory system using these chips?

- d) Draw the memory cell structures of 1-bit DRAM cell and 1-bit SRAM cell.

- :040

- (PO1)

- a) With appropriate examples and/or figures, define the following terms:

- j. Instruction Set Architecture

- ii. Cylinder

- iii. Data Channel

- iv. Moore's Law

- v. Victim Cache

b) To assess a computer system following a SPEC benchmark suit, we have to consider a specific 4+ calculation procedure. 3+3

- i. Explain the steps of the calculation procedure using a flowchart.

- What kind of Pythagorean mean will be used to calculate the overall metric? Justify (PO: your answer.

- iii. How will the pipeline-based system be considered in this assessment process?

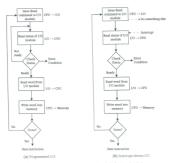

- c) The flowchart shown in Figure 2(a) outlines the necessary steps for any data transfer be-5 tween the CPU and 1/O devices. However, instrump-driven 1/O, as shown in Figure 2(b), (CO)) is often considered to improve the efficiency of any system. Considering both diagrams, ese (PO2) plain how interruption could be incorporated into the system. Additionally, apply Amahl's have to determine the enhancement in performance while using interruption.

Figure 2: Flowcharts of data transfer between CPU and I/O for Question 2.c)

| ŝ. | a) Consider a main memory system with 32-bit byte-level addressing and a cache with 64-byte<br>line size. Assume a four-way set-associative cache with a tag field in the address of 9 bits. | 4+<br>3+3      |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | <ol> <li>Determine the values of the following parameters:</li> <li>Number of addressable units</li> </ol>                                                                                   | (CO4)<br>(PO1) |

|    | <ul> <li>Number of blocks in main memory</li> </ul>                                                                                                                                          |                |

|    | <ul> <li>Number of lines in set</li> </ul>                                                                                                                                                   |                |

|    | <ul> <li>Number of sets in the cache</li> </ul>                                                                                                                                              |                |

|    | <ul> <li>Number of lines in the cache</li> </ul>                                                                                                                                             |                |

|    | ii. What modifications to the memory system configuration can be performed to make it a<br>Direct mapping and fully-associative mapping system, respectively?                                |                |

|    | <li>iii. Illustrate the address formats in direct mapping, fully-associative mapping, and four-set<br/>associative mapping approaches.</li>                                                  |                |

|    | b) What happens when the Error Correction System finds an error with a check bit instead of a                                                                                                | 8              |

error correction code is used to fix single-bit and detect double-bit errors in a 1024-bit data

Assume that the disk head starts at track 0. Let the disk receive a request to access a random sector on a random track. Now, calculate the following parameters:

word? Justify your answer.

Average seek time

Average rotation latency

Transfer time for a sector

Total average time to satisfy a request

Size of a cylinder for a double-sided four-platter disk

Disk cancelide tight-platter disk

c) Consider a single-platter disk with the following parameters: Rotation speed: 7200 rpm Number of tracks on one side of the platter: 30,000 Number of sectors per track: 600 Sector size: 1kB Seek time: Ins for every hundred tracks travened

CSE 4305