May 29, 2024

B.Sc. in CSE, 4<sup>th</sup> Semester

## ISLAMIC UNIVERSITY OF TECHNOLOGY (IUT) ORGANISATION OF ISLAMIC COOPERATION (OIC) DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

Semester Final Examination S Course No.: EEE 4483 Course Title: Digital Electronics and Pulse Techniques

Summer Semester, A. Y. 2022-2023 Time: 3 Hours Full Marks: 150

There are 6 (six) questions. Answer all 6 (six) questions. The symbols have their usual meanings. Programmable calculators are not allowed. Marks of each question and corresponding COs and POs are written in the brackets. Assume reasonable values for any data that seems to be missing.

- (a) Statch the circuit diagram of a monostable multiventor using OPAMP to generate 16 a pulse wave where the lower couloge level is the statch arts, and the upper values (CO2, level is the unstable statch. Discuss the openation of this circuit with proper wave PO2) shapes and derive an operation for the mismoshable timing period. If the value of the capation is the EC immung trends it A Tayl. A Coccurstien 275 of the prostances statch are a static period of the value of the capation of the state of the operation of the state of the capation of the state o

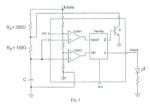

- b) For the circuit shown in Fig. 1, derive the expression of the time period of the output signal. Determine the value of the capacitor (C) to make the time period equal to (CO2, 2.5ms, Determine the duty cycle of the output signal. Sketch the wave shapes of the output voltage and the voltage across the capacitor with proper scaling and labelling.

2. a) Steedy the block diagram of a 3-bit successive approximation AD converter. For this 5-bit successive approximation AD converter summariants of the steep of the stee

- b) With proper circuit diagram, derive the expression of total conversion time of a dual used in a dual slope A/D converter. The reference voltage is set to, VREF = 7.75 V. binary form of the digital output, when the analog input voltage is V<sub>IN</sub> = - 3.15 V.

- With suitable diagrams discuss the Read, Write and Refresh operation of a one transistor DRAM memory cell. (CO1,

- b) Sketch the MOS-based OR ROM memory cell array to store the data given in 10

| Table 1 |       |       |       |       |       |

|---------|-------|-------|-------|-------|-------|

| BL[0]   | BL[1] | BL[2] | BL[3] | BL[4] | BL[5] |

|         | 0     | 0     |       | 0     | 0     |

|         | 0     | 0     |       |       | 1     |

| 0       |       | 0     | 0     | 0     |       |

|         |       | 1     | 0     |       | 1     |

|         | 0     | 0     | 0     |       | 0     |

| 0       | 0     |       |       | 0     |       |

- 4. a) With suitable diagram briefly discuss the operation of 6T SRAM.

- b) Sketch the circuit diagram of programmable logic array corresponding to the

$$f1 = AB + ABC'$$

$f2 = B'C + A'BC'$

$f3 = A + A'B + ABC'$

Describe which type of logic circuit is presented in Fig. 2. For this circuit, sketch the input-output characteristics curve, determine the different input & output voltage

- b) Sketch the circuit diagram of 3 input OR gate using Diode Logic and describe it's

- Sketch the circuit diagram of 2 input XOR gate using CMOS logic

| 6. | a) | Sketch the circuit diagram of 3-input NAND gate using Diode Transistor Logic (DTL) and discribe the operation of the circuit for two possible cases:<br>(i) when all the inputs are at logical '1' store<br>(ii) when all one of the inputs is at logical '0' state<br>(Assume reasonable values of different components for the analysis) | 12<br>(CO1,<br>PO1) |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|    | b) | With proper reasoning, describe how TTL gates overcome the speed limitation of DTL gates.                                                                                                                                                                                                                                                  | 10<br>(CO1,<br>PO1) |

|    | c) | Describe the difference between depletion type MOSFET and enhancement type MOSFET.                                                                                                                                                                                                                                                         | 3<br>(CO1,<br>PO1)  |