1

### Proposition of a new model for memristive window function through comparative analysis

A Thesis Submitted to the Academic Faculty in Partial Fulfillment of the Requirements for the Degree of

### BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Submitted by

### FARDEEN HASIB MOZUMDER (ID : 132420) KOUSHIK AHMED ANKON (ID : 132467) MAHMUDUL HASAN (ID : 132453) ALI KHALID NADA (ID : 132497)

### UNDER THE SUPERVISION OF

### Dr . Khondokar Habibul Kabir

**Assistant Professor**

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Gazipur, Bangladesh

November 2016

### Proposition of a new model for memristive window function through comparative analysis

Approved by:

#### Dr. Khondokar Habibul Kabir

Supervisor and Assistant Professor, Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT), Boardbazar, Gazipur-1704.

Date: .....

### Abstract

4

This work presents a set of mathematical tools for the analysis and modelling of memristor devices. The mathematical framework takes advantage of the compliance of the memristor's output dynamics with the family of Bernoulli differential equations which can always be linearised under an appropriate transformation. Based on this property, a set of conditionally solvable general solutions are defined for obtaining analytically the output for all possible types of ideal memristors. To demonstrate its usefulness, the framework is applied on HP's memristor model for obtaining analytical expressions describing its output for a set of different input signals. It is shown that the output expressions can lead to the identification of a parameter which represents the collective effect of all the model's parameters on the nonlinearity of the memristor's response. The corresponding conclusions are presented for series and parallel networks of memristors as well. The analytic output expressions enable also the study of several device properties of memristors. In particular, the hysteresis of the current-voltage response and the harmonic distortion introduced by the device are investigated and both interlinked with the nonlinearity of the system. Moreover, the reciprocity principle, a property form classical circuit theory, is shown to hold for ideal memristors under specific conditions.

Based on the insights gained through the analysis of the ideal element, this work takes a step further into the modelling of memristive devices in an effort to improve some of the macroscopic models currently used. In particular, a method is proposed for extracting the window function directly from experimentally acquired input-output measurements. The method is based on a simple mathematical transformation which relates window to sigmoidal functions and a set of assumptions which allow the mapping of the sigmoidal to current-voltage measurements. The equivalence between the two representations is demonstrated through a new generalised window function and several existing sigmoidals and windows. The proposed method is applied on three sets of experimental measurements which demonstrate the usefulness of the window modelling approach and the newly proposed window function. Based on this method the extracted windows are tailored to the device under investigation. The analysis also reveals a set of non-idealities which lead to the introduction of a new model for memristive devices whose response cannot be captured by the window-based approach.

### ACKNOWLEDGMENTS

We thank Allah before all, whose many blessings have made us who we are today. We would like to thank our parents, family members, and those very close to our hearts. Without their guidance and support, we would not have made this far in our lives. Every moment with them will be cherished and also motivates us to go further into new dimensions in this life.

We give our sincere and grateful thanks and appreciations to our supervisor, Dr. Khondokar Habibul Kabir, for his help, guidance, and infinite support through this project and for his guidance through our years in electrical engineering department. Without your guidance and support, the completion of this project would not be possible.

We would like to dedicate our appreciation to our co-supervisor ,Mr. Mehedi Hassan Galib ,for his great support and guidance through out this graduation project.

We would like to thank all other faculty members of the Department of "Electrical and Electronics Engineering" of Islamic University of technology, who had been involved with us through thick and thin and helped us in our academic journey.

# Contents

| Contents                  | 08 |

|---------------------------|----|

| List of Tables            | 10 |

| List of Figures           | 12 |

| Symbols and Abbreviations | 15 |

| 1 Introduction            |    |

| 1.1 | What  | is a memristor and how it was defined     | 22   |

|-----|-------|-------------------------------------------|------|

| 1.2 | Why i | s the memristor interesting: Applications | 25   |

|     | 1.2.1 | Digital Applications                      | . 25 |

|     | 1.2.2 | Analog Applications                       | 29   |

| 1.3 | Motiv | ations and Contributions                  | 31   |

### 2 Background Theory

| 2.1 | Memr  | istors and Memristive Systems | 35 |

|-----|-------|-------------------------------|----|

|     | 2.1.1 | How the memristor was defined | 36 |

|     | 2.1.2 | The memristor                 | 36 |

| 39 |

|----|

| 41 |

|    |

| 45 |

| 48 |

| •  |

| 4 | Pro | posed window function    | •55 |

|---|-----|--------------------------|-----|

| 5 | Cor | nclusion                 |     |

|   | 5.1 | Summary of contributions | 58  |

|   | 5.2 | Future work              | 60  |

|   | 5.3 | Final thoughts           | .62 |

| iography64 |

|------------|

|------------|

# List of Tables

# **List of Figures**

| Figure 1.1 |    |

|------------|----|

| Figure 2.1 |    |

| Figure 2.2 |    |

| Figure 2.3 |    |

| Figure 3.1 |    |

| Figure 3.2 | 51 |

| Figure 3.3 | 53 |

| Figure 3.4 |    |

| Figure 4.1 | 57 |

# Symbols and Abbreviations

| ANN                | Artificial Neural Network                                              |

|--------------------|------------------------------------------------------------------------|

| CNN                | Cellular Neural Network                                                |

| CMOS               | Complementary Metal-Oxide-Semiconductor                                |

| CMOL               | CMOS/nanowire/MOLecular hybrid circuit                                 |

| BDE                | Bernoulli Differential Equation                                        |

| LDE                | Linear Differential Equation                                           |

| ODE                | Ordinary Differential Equation                                         |

| FPGA               | Field-Programmable Gate Array                                          |

| mFPGA              | Memristor-FPGA hybrid circuit                                          |

| nFPGA              | Nano-FPGA hybrid circuit                                               |

| FPNI               | Field-Programmable Nanowire Interconnect                               |

| HP                 | Hewlett-Packard                                                        |

| KCL                | Kirchhoff's Current Law                                                |

| KVL                | Kirchhoff's Voltage Law                                                |

| PLA                | Programmable Logic Array                                               |

| nanoPLA            | Nano-Programmable Logic Array                                          |

| STDP               | Spike-Timing-Dependent Plasticity                                      |

| THD                | Total Harmonic Distortion                                              |

| VLSI               | Very-Large-Scale Integration                                           |

|                    |                                                                        |

| P(t), Q(t)         | Time dependent coefficients of Bernoulli's differential equation       |

| I(t)               | Integrating factor for Bernoulli's differential equation               |

| $\zeta = y^{1-n}$  | Change  of  variable  linearising  Bernoulli's  differential  equation |

| inf <sub>R</sub> S | Infinum; greatest lower bound of $S$ in $R$                            |

| sup <sub>R</sub> S | Supremum; least upper bound of $S$ in $R$                              |

| В                  | Incremental capacitance; constant capacitance in the linear case       |

|                    |                                                                        |

| $f_{\rm C}(v,q)=0$                                          | Constitutive relation for the nonlinear capacitor                             |

|-------------------------------------------------------------|-------------------------------------------------------------------------------|

| <i>q</i>                                                    | Charge (temporal integral of current)                                         |

| i                                                           | Current                                                                       |

| d                                                           | Euclidean distance; used to measure model's accuracy                          |

| $\phi$                                                      | Flux-linkage (temporal integral of voltage); referred also as flux            |

| γm                                                          | Formula for evaluating the amplitude of harmonics; $m = 0, 1, 2, 3$           |

| $a_{0}, a_{n}, b_{n}$                                       | Coefficients of the Trigonometric Fourier Series; $n = 1, 2, 3,$              |

| $C_0, C_n$                                                  | Magnitude of <i>n</i> -th harmonic component; $n = 1, 2, 3,$                  |

| $f_j$                                                       | Frequency; $j = 0, 1, 2, 3,$                                                  |

| L                                                           | Incremental inductance; constant inductance in the linear case                |

| $f_L(\phi, i) = 0$                                          | Constitutive relation for the nonlinear inductor                              |

| И                                                           | Input signal                                                                  |

| У                                                           | Integrated input                                                              |

| K(k), F( $\varphi$ , k)                                     | Complete and incomplete elliptic integral of the first kind                   |

| $E(k), E(\varphi, k)$                                       | Complete and incomplete elliptic integral of the second kind                  |

| arphi                                                       | Argument of elliptic integral                                                 |

| k                                                           | Modulus of Jacobian elliptic functions and integrals                          |

| W                                                           | Incremental memductance; constant conductance in the linear case              |

| F                                                           | Generalised memristance of memristive system                                  |

| М                                                           | Incremental memristance; constant resistance in the linear case               |

| Μ                                                           | Instantaneous memristance                                                     |

| $f_M(\phi, q) = 0$                                          | Constitutive relation for the nonlinear memristor                             |

| $\mu_{v}$                                                   | Mobility of charge carriers                                                   |

| $\alpha$ , $\alpha_j$                                       | Model's parameter(s) of appropriate dimensions; $j = 1, 2, 3,$                |

| β                                                           | Dimensionless parameter controlling the nonlinearity of memristor             |

| $\widetilde{eta}$                                           | Parameter $\beta$ rescaled such that $\tilde{\beta} \in (0, 1)$               |

| $\boldsymbol{\mathcal{K}}_{1},\boldsymbol{\mathcal{K}}_{2}$ | Constant of proportionality; $\kappa_1$ in $dW/dt$ , $\kappa_2$ in $dM/dt$    |

| θ                                                           | Binary parameter determining the state of hybrid model; $\theta \in \{0, 1\}$ |

| Z                                                           | Set of natural numbers $0, \pm 1, \pm 2, \pm 3, \dots$                        |

| $Z^+$                                                       | Set of positive natural numbers 1, 2, 3,                                      |

| $Z_0^+$                                                     | Set of positive natural numbers 0, 1, 2, 3,                                   |

| Ν                                                           | Set of integer numbers 0, 1, 2, 3,                                            |

| $N^+$                                                       | Set of integer numbers 1, 2, 3,                                               |

| R                                                           | Set of real numbers                                                           |

| $R^+$                                                       | Set of positive real numbers excluding zero                                   |

| У                                                           | Output signal                                                                 |

|                                                             |                                                                               |

| $\rho(t)$                              | Instantaneous electric power                                                               |

|----------------------------------------|--------------------------------------------------------------------------------------------|

| R                                      | Incremental resistance; constant resistance in the linear case                             |

| Ro                                     | Initial memristance at $t = 0$                                                             |

| $R_{OFF}$                              | The maximum resistance value of a memristor                                                |

| $R_{ON}$ $f_{R}(v, i) = 0 \text{ Con}$ | The minimum resistance value of a memristor nstitutive relation for the nonlinear resistor |

| S                                      | Sigmoidal curve                                                                            |

| L                                      | Lower asymptote of a sigmoidal curve                                                       |

| $y_{\sigma}$     | Point of inflexion of a sigmoidal curve                            |

|------------------|--------------------------------------------------------------------|

| G                | State function of memristive system                                |

| h                | Function of the input signal; constituent part of state equation   |

| Z.               | Internal state variable/vector                                     |

| Zmax             | Value of internal state variable at which the window is maximised  |

| W                | Thickness of memristor's doped region                              |

| D                | Total thickness of memristor's oxide layer                         |

| $\mathcal{W}_0$  | Initial thickness of doped region at $t = 0$                       |

| t                | Time                                                               |

| x                | Normalised time                                                    |

| v                | Voltage                                                            |

| $H_{\lambda}(t)$ | Bipolar piecewise linear waveform                                  |

| λ                | Determines rise and fall time of Bipolar piecewise linear waveform |

| A                | Amplitude of a periodic waveform                                   |

| $T_0$            | Period of a waveform; $T_0 = 1/f_0$                                |

| $\sigma(t)$      | Sinusoidal waveform                                                |

| $\Lambda(t)$     | Triangular waveform                                                |

| f                | Window function                                                    |

| $\hat{f}$        | Modified window function                                           |

| δ                | Controls the shift of the roots in the modified window             |

| <b>F</b> max     | Maximum value of the window function at $z = z_{max}$              |

| η                | Window parameter; scales the maximum of window                     |

| р                | Window parameter; controls the flatness around the maximum         |

| r                | Window parameter; controls the skewness                            |

| $ar{f}$          | Reciprocal of a window function; $1/f(z)$                          |

| F(z)             | Integrated reciprocal of a window function                         |

| W                | Electric work                                                      |

### **Chapter 1**

## Introduction

Without entering into any technical details and formal definitions this chapter will introduce the field of memristors and memristive systems, the motivation and the contributions of this project. Starting with a brief history of the memristor, the chapter introduces the concept of memristors and memristive systems in order to initiate the reader. This is followed by a short overview of the field of memristors and its applications in an effort to justify the significance of the field. From this overview two areas of the existing literature in memristors which lack behind will be identified as the motivation of this work. These two areas are: the incomplete circuit theory for the analysis of ideal memristors and the inadequate modelling of devices which fails to describe non-linearities of the device. Finally, with the aim of improving these two areas, we define a window function which will address the problem mentioned above.

### **1.1** What is a memristor and how it was defined

Leon Chua, a professor at Berkeley university, with his seminal 1971 paper challenged the well established perception of classical electronics that the three fundamental 2-terminal passive circuit elements are only the resistor, the inductor and the capacitor [1].

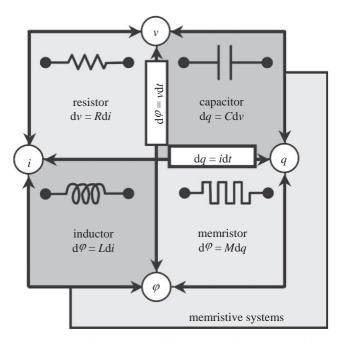

Based on simple symmetry arguments he claimed that a fourth fundamental 2-terminal passive circuit element is necessary to complement the other three. More specifically, Chua realised that out of the six possible pairwise combinations between the four fundamental circuit variables [2], namely, the current, voltage, charge, and flux-linkage, only five had been identified. He therefore postulated mathematically the *memristor* as the element relating the charge and the flux-linkage in order to establish the missing link (see Figure 2.1).

As its name indicates, the memristor (from memory-resistor) behaves similarly to a nonlinear resistor in the sense that, its current-voltage characteristic is nonlinear. In fact, instantaneously the memristor can be viewed as a resistor, however, unlike the conventional ohmic element, it is a dynamic element with memory [1]. Its memory property stems from the fact that its memristance (or simply instantaneous resistance) is determined by the entire past history of the input (time integral of the voltage or current) driving the element [3,4]. In other words, its memristance, which is measured in Ohms, encodes how much charge (for current driven), or flux-linkage (for voltage driven) has passed through the device over time. Therefore, an ideal memristor will keep changing its memristance as long as an input is applied on the component. Once the driving signal is removed, the ideal device will maintain its state indefinitely or, until the driving signal is applied again. Its intrinsic non-volatile memory property and its multiplicative transfer function give also rise to one of the qualitative characteristics of memristors, namely, the hysteretic current-voltage responses crossing the origin. An indicative example of a hysteretic current-voltage characteristic of an ideal memristor is illustrated in Figure 2.2b. This distinctive behaviour of the memristor cannot be reproduced by any combination of ideal passive resistors, inductors and capacitors. It is in this sense that Chua considers the memristor a rightful candidate for the fourth fundamental 2-terminal passive circuit element [5–7].

It is interesting to remark that the memristor is not the only proposed resistive element exhibiting non-volatile memory. For example, a decade earlier than Chua, Bernard Windrow introduced the *memistor*, a three-terminal passive transistor-like element in which one of its terminals (the control electrode) is used to adjust the resistance between the remaining two electrodes. Although the memistor is passive and exhibits non-volatile history-dependent resistance as well, it is a three-terminal element and should not be confused with the memistor, which is a 2-terminal element [8,9]. In fact, it has been recently suggested that a memistor can be built from two memristors [10].

Soon after the introduction of the memristor, Chua and his student Kang observed that systems or devices may exist which exhibit characteristics (e.g. non-volatile memory, hysteresis, zero-crossing) similar to those of memristors. However, the definition of the ideal memristor is inadequate to capture their behaviour. They therefore introduced the notion of *memristive systems* to enable the modelling of a broader class of nonlinear dynamical systems whose behaviour resembles that of memristors [6,11]. Unlike the memristor, the definition of the new generalised system allows the memristance state to depend on one or more variables which are not restricted to the charge (or flux-linkage). Thus, these systems are not limited to electronic devices since their input/output waveforms need not be current and voltage and the memristance may not have units of Ohms. This renders the memristor a special case of memristive systems which is electrically driven and its state variable, determining the memristance, is exclusively the charge or the flux-linkage.

The introduction of memristors and memristive systems suggested a new taxonomy in nonlinear circuit theory in which classical nonlinear resistors, inductors and capacitors are not sufficient for accurately modelling the behaviour of complex nonlinear circuits [6,7]. Chua and Kang demonstrated the usefulness of these new family of ideal elements by showing that a variety of different systems, such as discharge tubes, the thermistor, Josephson junctions and the Hodgkin-Huxley circuit model of the neuron, can be modelled as memristive systems [6,11,12]. Nevertheless, for almost 40 years extremely few researchers explored further the new ideas presented by Chua and Kang.

The theoretical prediction of the memristor remained unverified for several decades because its existence was suggested during a period when researchers were still experimenting with devices at the micrometre-scale. However, it is evident from the several experimental devices identified as memristive [13–18] that this behaviour is exposed on the nanometre-scale [19,20]. Although some examples of solid state devices appeared in the literature whose behaviour pointed to that of a memristor, researchers failed to identify them as such (see References [15,21–23] for several examples). The first nanoscale solid-state device recognised as a memristor was fabricated very recently, in 2008, by Hewlett-Packard (HP) Labs [13,24,25]. In an attempt to understand the source of the behaviour of their device, HP has provided a simple heuristic model which, although an extreme idealisation, has become a point of reference in the literature of memristors [13].

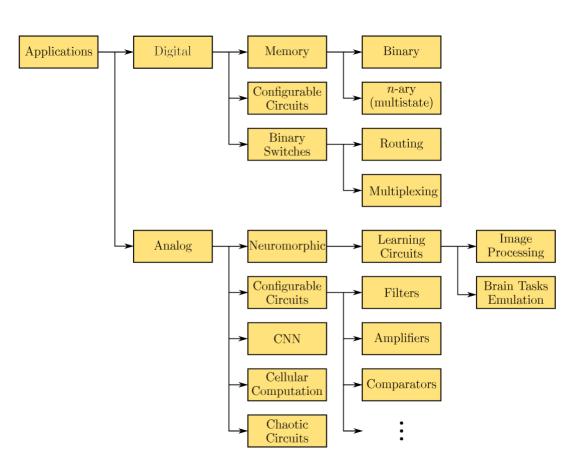

**Figure 1.1:** Classification of memristor's applications: The classification is performed based on how the memristance is utilised. In digital applications, only a pre-specified number of discrete resistance levels is utilised. In analog applications, a continuous range between a minimum and a maximum resistance level is exploited.

### **1.2** Why is the memristor interesting: Applications

The report of the experimental realisation of the memristor by HP reignited the interest of both the scientific community and the electronics industry [21].<sup>1</sup> The large interest for this new element emerges from its many attractive properties (small size [15], low-power consumption [27–29], high-speed [29–31], non-volatile binary [17,32], or multistate [30,33,34], or continuous [17] resistance switching memory and synapse-like behaviour [35]) which make the memristor ideal candidate for improving the performance of already existing applications (e.g. digital memories, digital reconfigurable

logic circuits) and opening up the way for applications previously impossible to materialise (e.g. neuromorphic circuits, learning/adaptive circuits, reconfigurable analog circuits) [36,37]. Figure1.1presents a classification of memristors' applications based on how their memristance is utilised. The applications are explained in more detail in the following sections.

An equally important role in the large interest in memristors has played the search of the VLSI community for alternative technologies to extend the lifetime of the well established and extensively used CMOS technology. It has become clear that further scaling of CMOS transistors' gate length is becoming increasingly difficult [37-40]. One proposed solution which may prolong the use of the CMOS technology without requiring further scaling is the combination of CMOS circuits with molecular switches. Such hybrid circuits divide the functionality so that the merits of both worlds are exploited: the rich functionality offered by CMOS circuits and the nanoscale size and low-power consumption of molecular switches. In this scenario the memristor will be the element acting as the molecular switch [37,39,41,42]. In addition, the fabrication process of such nano-devices is simpler (only one critical dimension needs to be controlled) [37], cheaper [36,37] and in many cases compatible with the CMOS fabrication processes currently used in the industry [32,43,44], however, at the expense of an increased proportion of defective devices [45,46]. Nevertheless, the benefits outperform the obstacles of this approach and were not enough to hold back groups which managed to demonstrate hybrid CMOS-memristor circuits with high yield of molecular switches [30,47] and techniques to work around any remaining defects [42,48,49].

A plethora of applications taking advantage of all these unique properties of memristors have been proposed and are actively explored. Their application space can be divided into *digital* and *analog*, depending on how the range of memristance levels of the device is utilised. For digital applications, only a finite number (two for binary or  $2^n$  for  $2^n$ -ary, with n = 2, 3, ...) of discrete resistance levels are used. On the other hand, for analog applications the continuous range of resistances between a minimum and a maximum is used, enabling true analog computation.

#### **1.2.1** Digital Applications

The most important digital applications proposed until now may be further separated into three major categories: 1) digital memories (binary or  $2^n$ -ary), 2) configurable/-

programmable digital logic circuits and 3) bistable switches for routing, multiplexing/demultiplexing. All these applications are based on the same principle: a single programmable memristor acting as a switch which can be configured to two (for binary) resistance levels by applying an appropriate input pulse. If each of the two resistance levels is assigned to one of the two logical values (Logic '0' and Logic '1'), then every device becomes a binary memory cell able to store 1-bit or, a binary switch which can represent one of the two possible outcomes of a Boolean function or, simply a switch which allows or blocks the propagation of a signal [32,37,43,44,50]. Similarly, a 2  $^{n}$ - ary memristor can be switched to  $2^{n}$  resistance levels, hence, it is able to store a *n*-bit value.<sup>2</sup> Therefore, what changes from one application to the other is how the discrete states are interpreted.

The area of most intensive research is digital memories and in particular binary memories. The choice of the memristor as the fundamental memory cell is motivated by its nanoscale dimensions, allowing extremely dense memories, the potential for low-energy consumption during switching and by the zero power consumption for retaining its state when idle due to its intrinsic non-volatility. More importantly the use of memristors has the potential to revolutionise the computer industry by enabling a new paradigm in which computers can be instantly switched on or off with practically zero booting times [24,51]. Many memristive devices have been reported which demonstrate the required non-volatile bistability and have been used for building small-scale binary memories [17,30,32,43,44,47,52,53], however, large-scale commercial memories have not been developed yet. Nevertheless, these early prototypes indicate the feasibility and the potential of memristor-based memories as a technology that can compete or even overpass the currently used ones. This is also backed by the recommended focus areas of the latest International Technology Roadmap for Semiconductors (ITRS 2011) [54] and the joined announcement by HP and Hynix of their plans to release into the market memristor-based memories in 2014 [55,56]. The possibility to increase even further the density of such memories is also explored by following strategies for stacking multiple layers of memristors on top of each other [53,57] with each layer containing fundamental memory cells configurable to two or more resistance levels [58]. Although progress is slow compared to binary memories, devices have been studied which are suitable for multilevel memories [30,33,34,58,59] and circuits for writing to and reading from memristor-based multilevel memories have been proposed [60].

Digital reconfigurable logic circuits is another field for which the use of memristors is investigated and promoted [19,37,43,44]. These are FPGA-like circuits consisting of a large number of general purpose computational and memory blocks. The various blocks can be wired to each other through a reconfigurable network of interconnections in order to synthesise almost any type of Boolean function to perform massively parallel application-specific computation [41,42]. To benefit from the potentially higher densities and lower power footprint, memristor-based memories can replace the currently used memory blocks. Additionally, memristors can serve as the switches at the programmable interconnections of the signal routing network between the blocks [37]. Finally, memristors can perform some of the computation provided by the functional blocks, however, fundamentally different (to conventional transistor-based logic) approaches are required to implement Boolean functions in this case [61]. The most important of the the approaches proposed are: wired-AND logic [43,62], threshold logic [63,64] and implica*tion logic* [61,65,66]. Implication logic is the only computationally complete <sup>3</sup> method amongst the three. Additionally, it enables *stateful* logic where the memristors can take part in both, the computation and storage of the final outcome making this approach the most attractive [61].

In order to best utilise the advantages offered by using memristors and also overcome the challenges presented by the fact that this is 2-terminal *passive* element, fundamen- tally different circuit architectures need to be adopted as well [67]. The majority of architectures proposed for the digital and analog applications are based on the idea of a nano-crossbar array. Such an array consists of two stacked layers of parallel electrodes (nanowires) positioned perpendicular to each other, thus, forming a two-dimensional grid. At each point of intersection, in between the two nanowires, a thin layer of resis- tance switching material is placed so that each junction operates as a memristor. The two electrodes of each crosspoint serve as the two terminals of the memristor. By apply- ing an appropriate pulse to a crosspoint device, its conductance can be independently configured or sampled [41,42,49,62,68].

Unfortunately, an integrated circuit consisting only of memristors has very limited functionality, especially when used for computation. Being passive, memristors cannot supply energy to drive subsequent parts of the circuit, they cannot offer signal amplification or restoration and other essential operations offered by the active transistors [37,68].

The dominating solution proposed to overcome this bottleneck is to augment the memristive crossbar array with a CMOS circuit layer. With this approach circuit designers can benefit from the advantages offered from both technologies: the functional flexibility and high fabrication yield of CMOS circuits and the high density, low-power consumption and non-volatile memory and programmability of memristors [37,50,68]. Many variants of this hybrid-CMOS/nanocrossbar architecture have been suggested and explored by researchers (CMOL [41,48,49,68,69], FPNI [42,44], nanoPLA [69,70], mFPGA [71] and 3D nFPGA [53,57,72–74]). Each variation results from different compromises between the design specifications and how the functionality is divided between the two layers [42].

#### 1.2.2 Analog Applications

The digital applications for which the use of memristors is proposed is nothing extremely innovative or radically new. Most of them are well established applications for which the memristor can potentially offer a big boost in their performance hence extending their lifetime for a few more years. A far more interesting domain of applications are the analog applications which exploit the continuous range of resistances of the device [51].

The memristor compacts in the dimensions of a nanoscale device useful properties and functionality (e.g. multiplicative transfer function, non-volatile and configurable resistance-memory, continuous resistance range, low-power consumption) [45]. These features enable the hardware implementation of systems whose realisation is extremely difficult using currently available technologies. The difficulties arise not because current technologies are incapable of replicating the necessary functionality, but because they cannot do so efficiently in terms of chip area and power consumption [20]. This causes problems in any attempt of scaling up the system in order to perform any useful and realistic task [75]. Initial memristor realisations have demonstrated promising results which indicate that such devices can help in overcoming these severe obstacles (for some indicative examples see References [17,25,30–32,34,35,43,44,76,77] which demonstrate all the aforementioned properties).

One of the most fascinating analog applications, which has attracted most of the atten- tion along with digital memories, is *bioinspired* circuits and in particular *neuromorphic*. These systems employ an *artificial neural network* (ANN) which mimics a particular functionality of a biological neural network inspired from the human or other animal's neural system to perform a certain task or computation. The ANN consists of the neu- rons (nodes of the network) and the synapses (edges of the network) which connected together form the neural network. The neuron applies a nonlinear function on the in- coming signal and according to the result of this operation transmits signals to other subsequent neurons connected to it through the synapses. The synapse multiplies the incoming signal by its weight and, if the network is *adaptive* [76], at the same time readjusts its weight according to a nonlinear function which depends on the history of the input signal. This diverse and complex functionality of the synapse which combines non-volatile plasticity, memory and a multiplicative transfer function can be replicated by a single memristor [45]. In a realistic neural network able to perform a useful task, each neuron is connected to approximately  $10^3$ - $10^4$  synapses. Assuming a target den- sity of  $10^6$  neurons per cm<sup>2</sup>, it is not possible to maintain the high ratio of synapses per neuron using only conventional transistor technology due to both space and power limitations. However, using transistors to implement the relatively sparse neurons and memristors to implement the synapse, such systems may become feasible [75].

The potential of memristors enabling large-scale neuromorphic circuits has led many researchers to experiment with such systems through simulations or by fabricating actual devices. Some of the most important examples are *adaptive* or *learning* cir- cuits [19,20,35,45,46,75,76,78–81]. These circuits implement a neural network whose synaptic weights are updated according to a learning algorithm (e.g. Hebbian [78], STDP [35,75]) which takes into account external stimulus and feedback from other interconnected neurons [19,20,45,76]. The use of memristor-based neuromorphic circuits was also demonstrated for *image's features extraction* [82]. For example, in two different studies a sequence of images was used to train a memristor-based neural network employing STDP learning to recognise the orientation of edges in a similar way to the V1 visual cortex layer of the human brain [45,75]. Another subcategory of bioinspired systems (not necessarily neuromorphic) which can benefit from memristors is *cellular* computation. Such hardware systems emulate the behaviour of biological cells. For example, the adaptive behaviour of a type of amoeba cell to environmental changes was simulated with a passive network incorporating a memristor [83]. Finally, a regular grid of memristors was used to determine the solution to a maze problem in an effort to show massively parallel computation using memristors [84].

The analog applications do not stop only at the more exotic neuromorphic circuits. Conventional analog circuits can benefit by including memristors in their setup. In such circuits the memristor can act as a configurable resistor which is operated normally at low voltages/currents (below a threshold) and programmed using high voltage/current pulses (above a threshold) [85]. As a result, circuits become partially configurable and thus able to adapt to a range of different requirements or conditions. In this way the need of rebuilding the whole circuit for a range of different specifications is eliminated [86]. Analog programmable circuits have already been explored theoretically, mostly through simulations. Some representative examples are: analog filters [23], gain amplifiers [85–87], threshold comparators [85], switching thresholds Schmitttriggers [85] and frequency relaxation oscillators [85]. In all these examples, features of the circuit such as, their bandwidth, gain, threshold and oscillation frequency, were configured, within a certain range, by adjusting the resistance of the memristor(s) accordingly. Other circuits have been also reported which make use of the memristor as an analog memory cell (e.g. signal correlator [88,89]) or simply take advantage of it's nonlinearity to improve some performance factors (e.g. extending the linear range of a differential amplifier [90]).

Finally, two other major fields of analog electronics which explore the use of memristors are *chaotic oscillators* and *cellular neural networks* (CNN). Several studies exploit the dynamical and nonlinear behaviour of the memristor in circuits for generating chaotic behaviour [91–96], with an important proportion of them being based on Chua's modified circuit [94–96].<sup>4</sup> Such circuits can be potentially used in cryptography and communications [93,97]. Similarly, the community of CNNs is trying to benefit by using memristors to implement the template weights, memory and logic used in these networks [21,98–100]. However, in both areas the work presented until now is theoretical and limited to software simulations (with the exception of Reference [93] which uses hardware emulation). Thus the feasibility of these attempts is yet to be proven in practise.

### **1.3** Motivations and Contributions

The potential for the commercialisation of many of the aforementioned applications has led to numerous attempts to fabricate memristor devices based on different material combinations. Depending on the application targeted, each experimental attempt was aiming at optimising some performance specification such as read/write speed [29–31], endurance, retention time, ON/OFF resistance ratio [30,32,47], number of discrete

resistance levels [30,33,34], a continuous range of resistance levels [17], power consumption [27–29] and compatibility with standard fabrication processes [32,43,44]. These efforts have resulted to the identification of a wide range of resistance switching devices demonstrating memristive behaviour. In all cases the resistance change, from the high to the low resistance level and vice-versa, is electrically induced (i.e. by applying an appropriate voltage/current pulse). However, the detailed underlying physical mechanisms responsible for these permanent changes vary significantly and are still the subject of active research since they are not well understood [14–16,101]. Indicative examples, out of the several published, range from oxide-based [13,25,27,28,31,33, 34,77,102–105], phase-transition [106], single-component nanowires [107], amorphous materials [17,30,35], spintronic [108–111] and nanoparticle assemblies [112]. A few of these studies go a step further, beyond just fabrication, to investigate [25,47,102,113– 115] and model [13,77,116–120] the underlying physical mechanisms that give rise to the observed behaviour. The extremely small dimensions and the diverse physical phenomena make this process difficult. As a result, the physical models presented until now have limited applicability and are only relevant to the specific device under consideration. Thus, until a standardised memristor technology is established and well modelled [75,85,121], researchers have turned to the use of macroscopic models which approximately capture the input-output dynamics without looking at the microscopic detail [7,25,67,80,100,121–126].

Despite the remarkable activity and progress in the field of memristors, it should be clear from the above discussion that research is mainly focused on the fabrication of memristors and their use in applications. A very limited amount of efforts is dedicated to the analysis and understanding of the properties and behaviour of the ideal element. This approach has generated a large gap on the theoretical front of memristors. Unlike other conventional elements, there is no well established circuit theory for studying memristors as individual elements or, as part of a larger network of memristors which may include other conventional circuit elements. The theory on memristors is limited to the original papers [1,6,11]. As a result, a big challenge in the effort to understand, and hence optimally design, memristors still remains the development of a general mathematical framework for their analysis that goes beyond mere computational simulations.

Motivated by this lack of tools for the analysis of memristors, a mathematical frame- work has been introduced which can provide analytic solutions for their input-output dynamics and facilitate the study of their properties. The framework is based on the compliance of the ideal memristor's dynamics with *Jacob Bernoulli's* differential equa-

tion, a classic nonlinear equation which is always linearisable, under an appropriate transformation [127]. Based on this property, a set of conditionally solvable general solutions have been defined for obtaining analytically the output as an explicit function of the input for all possible types of ideal memristors. This formulation provides a powerful and systematic methodology for the analysis, characterisation and design of devices governed by Bernoulli dynamics that does not rely on computationally expensive sweeping of parameters.

The usefulness of this formalism was demonstrated using HP's ideal memristor model as an example. In particular, by applying the mathematical framework analytic expressions were obtained for the model's output as an explicit function of the input for a set of widely used input waveforms, namely, the sinusoidal, triangular and bipolar piecewise linear. The analytic output expressions have revealed that the model's parameters of diverse origin (material, fabrication, input) can be combined into a single quantity which collectively determines the nonlinearity of the memristor's dynamics and hence its device properties. These results have been extended further for series and parallel networks of memristors. More specifically, analytic expressions were obtained describing the output of a series or parallel network of memristors characterised by HP's model. These expressions were also used to study the effect of series parasitic resistance.

The analysis of the output expressions has also provided useful insights into important properties of the memristor such as the hysteresis of the current-voltage characteristic curves and the harmonic distortion introduced at the output by the device. Both of these properties were related to the nonlinearity of the memristor through the identified parameter which governs its behaviour. Moreover, based on HP's memristor, two general memristive models were defined. Their output response is evaluated analytically using the framework and it is discussed under which conditions they give rise to a memristor. The discussion reveals a family of functional forms which will lead to a memristor. The study of the ideal memristor's properties concludes by looking at its compliance with the *reciprocity principle* [128,129]. It is shown that ideal memristors behave as reciprocal elements if certain requirements are satisfied. The property is demonstrated using the analytical output expressions obtained for HP's model and it is also extended to series and parallel networks of memristors.

Another issue which was implied by the previous discussion, is the lack of universal models for describing the behaviour of fabricated devices. Such models are difficult to obtain because of the diverse phenomena, between different devices, that give rise

to memristive behaviour and also because a standard memristor technology has not been established yet in the market. As a result research groups studying memristors, especially the ones with no access to a real device, resort to macroscopic models which attempt to approximately capture the device dynamics. The most common approach followed when defining such macroscopic models is the use of a *window function* [7,13, 121–123]. These are empirical functions which attempt to model the nonlinear dynamics of the internal state variable of the memristor. The problem is that in most cases these functions have been arbitrarily defined without any relevance to experimental inputoutput measurements.

With the aim of improving the window functions currently used, and consequently the macroscopic models, an alternative way of using experimental current-voltage measurements has been suggested which can help in acquiring an improved and more suitable window function for the device under consideration. The method applies to a certain class of memristors whose resistance state follows a *sigmoidal curve* with respect to the charge or flux (integrated current or voltage). It is shown that such sigmoidal curves can be easily obtained from experimental measurements and converted to a corresponding unique window function by applying a simple mathematical transformation. Based on these observations, an experimental procedure was suggested through which a more appropriate window function can be obtained.

The proposed procedure for extracting the window is tested using experimentally obtained measurements from real devices reported in the literature as memristors [17,34, 107]. For some of the datasets, the analysis revealed an underlying sigmoidal, verifying the relevance of the window-sigmoidal modelling approach. For some other datasets, it was shown that, although an underlying sigmoidal was not identified, it was still possible to approximate their response using simpler models such as HP's. For these models the analysis has identified additional factors which must be taken into account during the modelling of such devices. These factors have led to the introduction of a new memristive model which describes the observed responses more accurately. Finally, the ideality of these devices was discussed, concluding that many fabricated devices are mistakenly referred to as memristors rather than memristive systems. Nevertheless, it is suggested that the theory for ideal memristors can still be applied to such devices, verifying the significance of studying the ideal component. The understanding developed for the behaviour and properties of the ideal memristor was crucial during the analysis of the fabricated devices.

### **Chapter 2**

## **Background Theory**

Chapter1 introduced informally the reader to the concept of memristors and memristive systems and presented an overview of the field highlighting two major gaps in the literature which have constituted the motivation behind this project. This chapter presents more formally the two notions and the background theory which will form the basis for understanding the results discussed in the subsequent chapters. The chapter begins by explaining the symmetry arguments on which the memristor was originally postulated. This is followed by the formal definitions of memristors and memristive systems and a discussion of some of their fundamental properties and characteristics. Then, a detailed description is given of HP's ideal memristor model which will be used extensively in Chapter4as the example model to demonstrate the mathematical framework introduced in Chapter3. Following HP's model, the window function modelling approach is introduced, together with some of its most important examples, as one of the major methods used to model the nonlinear dynamics of the internal state variables of memristive systems. In Chapter5, a new generalised window function will be proposed combining all the features of the examples presented here and introducing additional flexibility. Finally, the chapter concludes by discussing some practical issues which arise when window functions are used in practice and the preferred approach for avoiding them is presented.

### 2.1 Memristors and Memristive Systems

#### 2.1.1 How the memristor was defined

Consider the four fundamental circuit variables which according to elementary circuit theory are the: voltage v, current i, charge q, and flux-linkage  $\phi$  [5]. There are six distinct relations linking these variables pairwise (see Figure 2.1). Two of these relations correspond to the definitions of charge and flux-linkage as time-integrated variables:

$$q(t) = \int_{-\infty}^{t} i(t)dt \tag{2.1}$$

$$\phi(t) = \int_{-\infty}^{t} v(t)dt \tag{2.2}$$

with  $q_0$  and  $\phi_0$  the initial charge and flux at t = 0. Three other links are given by the implicit equations that define the constitutive laws of the generalised nonlinear fundamental circuit elements:

$$f_R(v, i) = 0$$

for the resistor **R**, (2.3)

$$f_{c}(v,q) = 0$$

for the capacitor C, (2.4)

$$f_L(\phi, i) = 0$$

for the inductor L. (2.5)

In order to complete the symmetry of the system-theoretic structure, Chua's insight was to postulate that the remaining link between q and  $\phi$  should be completed by another constitutive relation:

$$f_{\mathcal{M}}(\phi, q) = 0,$$

(2.6)

which would correspond to a missing element: the *memristor*. In this sense, the memristor complements the other three fundamental circuit elements as the fourth ideal passive two-terminal component [1,3,6].

#### 2.1.2 The memristor

A memristor, by definition, is a 2-terminal electronic element characterised by the constitutive relation  $f_M(\phi, q) = 0$  relating the charge q and the flux  $\phi$ , where q and  $\phi$  are given by (2.1) and (2.2) respectively [1]. Stating this more simply, the memristor is an element whose input-output response is uniquely determined by a charge-flux  $(q - \phi)$

**Figure 2.1:** The symmetry arguments based on which the memristor was defined. The diagram shows the six possible binary relations between the four fundamental circuit variables (current *i*, voltage *v*, charge *q* and flux  $\phi$ ). The two first relations are given by the definition of *q* and  $\phi$  as the time integral over *i* and *v* respectively. The remaining four relations give rise to the four fundamental 2-terminal passive circuit elements: the resistor **R** (relates *v* and *i*), the capacitor **C** (relates *q* and *v*), the inductor **L** (relates  $\phi$  and *i*) and the memristor **M** (relates *q* and  $\phi$ ). The last relation between the *q* and  $\phi$  is the one identified by Chua [1]. The symbol of each circuit element is also presented. To highlight that these are the generalised nonlinear components, their symbol is enclosed in a rectangle with its negative terminal indicated by a thicker edge. Adapted from Reference [13].

curve. The memristor is classified as *ideal* and *passive* if its  $q - \phi$  curve satisfies the following properties [1,2,130]: <sup>1</sup>

**2-1.1** unique

2-1.2 nonlinear

2-1.3 continuously differentiable

2-1.4 strictly monotonically increasing.

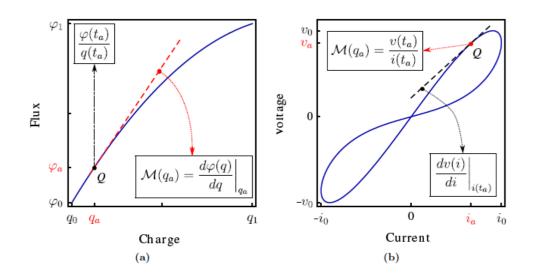

Figure 2.2ashows a  $q - \phi$  curve satisfying the criteria listed above and therefore representing an ideal passive memristor. Its corresponding current-voltage (i - v) response is shown in Figure 2.2bwhen the device is driven by a sinewave input.

The memristor is referred to as *charge-controlled*, or *flux-controlled* if its constitutive relation (2.6) can be re-expressed as an explicit function of q or  $\phi$  respectively:

$$\phi = \phi(q)$$

for the charge-controlled, (2.7)

$$q = \hat{q}(\phi)$$

for the flux-controlled. (2.8)

By assuming ideal memristors, (2.7) and (2.8) satisfy the properties (2-1.1)-(2-1.4) hence it can be shown that they are the inverse of each other:

$$\hat{q}^{-1}(q) = \phi(q) \quad \Leftrightarrow \quad \phi^{-1}(\phi) = \hat{q}(\phi).$$

(2.9)

Differentiating (2.7) and (2.8) with respect to time *t*, results in:

$$\frac{d\phi}{dt} = \frac{d\phi}{dq}\frac{dq}{dt} \qquad \text{for the charge-controlled,} \tag{2.10}$$

From (2.1) and (2.2), dq/dt = i and  $d\phi/dt = v$  respectively. Replacing these into (2.10) and (2.11) results in the representation of the memristor on the i - v plane. For the charge-controlled case it is given by:

$$v = \mathsf{M}(q)i(t), \tag{2.11}$$

where  $\mathbf{M}(q) = d\phi(q)/dq$  is the *incremental memristance*<sup>2</sup> measured in Ohms ( $\Omega$ ) and corresponds to the gradient of the  $q - \phi$  curve at an operating point (OP)  $Q(q_a, \phi_a)$  as illustrated in Figure 2.2. Similarly, for the flux-controlled case, the i - v representation is given by:

$$i = \mathbf{W}(\phi)v(t), \tag{2.12}$$

**Figure 2.2: (a)** An ideal  $q - \phi$  curve satisfying the criteria (2-1.1-2-1.4) and **(b)** its i-v response under a sinusoidal excitation. In both figures the same operating point (OP)  $Q(q_a, \phi_a)$  is shown. At Q in (a) the instantaneous memristance  $\phi(t)/q(t)$  and the incremental memristance  $\mathbf{M}(q) = d\phi(q)/dq$  are shown. For the same OP (b) shows the instantaneous resistance  $v(t)/i(t) = \mathbf{M}(q)$  and the incremental resistance dv(i)/di. The incremental memristance is equal to the instantaneous resistance when evaluated at the same OP. However, all four quantities will be equal with each other only if the  $q \phi$  curve becomes linear. In this case the memristor is indistinguishable from a linear resistor.

Moreover, restricting the memristors to ideal allows the substitution of (2.9) in (2.12):

$$\mathbf{M}(q) = 1/\mathbf{W}(\hat{q}^{-1}(q)) \quad \Leftrightarrow \quad \mathbf{M}(\boldsymbol{\phi}^{-1}(\boldsymbol{\phi})) = 1/\mathbf{W}(\boldsymbol{\phi}). \tag{2.13}$$

Hence, for an ideal memristor the distinction between charge- and flux-controlled is just a mathematical formality. In practise, such an element should have a unique description (i.e.  $q - \phi$  curve) irrespective of whether it is driven by a voltage or current input [19].

Equations (2.12) and (2.13) provide a more convenient route for accessing the memristance of a device especially in an experimental setup where the current and voltage are easier to measure. It is important to have in mind though that, the i - v response changes when the memristor is driven by a different input signal. Therefore, the i - vcurves, such as the one shown in Figure 2.2b, cannot be used to predict the output of the device. The memristor's response is uniquely defined by its characteristic  $q - \phi$ curve for any type of excitation.

39

**Limiting Linear Characteristics:** A passive memristor driven by a periodic waveform degenerates to a linear resistor as the excitation frequency increases towards infinity.

This property is illustrated in Figure2.3which shows that the area enclosed by the hysteretic loops decreases as the frequency increases until the i - v response collapses to a straight line representing the limiting linear resistor [11,21]. On the other hand, an ideal memristor under a dc-bias should eventually settle to one of its two limiting memristances ( $R_{ON}$  or  $R_{OF F}$ ). The final settling value of the memristance depends on the polarity of the bias [11,19].

**Closure Theorem:** A one-port<sup>4</sup> containing only memristors is equivalent to a single memristor [1,6].

**Existence and Uniqueness Theorem:** Any network containing only strictly passive memristors has one, and only one, solution [1,2].

The combination of these two theorems shows that a network of strictly passive memristors is equivalent to a single and unique memristor. This will form the basis which will enable in Chapter4the expression of the output of a network of memristors as an explicit function of its input.

Based on the insights presented in the above discussion it is now easier to justify the conditions (2-1.1-2-1.4) imposed on the  $q-\phi$  curve for an ideal memristor [1,2,130,131]:

- *unique*: This is necessary so that the memristor responds in exactly the same way irrespective of the type of waveform applied on the device. Assuming the same initial conditions  $(q_0, \phi_0)$ , it ensures that a certain amount of charge (or flux) flowing through the element causes always the same change in the memristance.

- *nonlinear*: The nonlinearity of the  $q \phi$  differentiates the memristor from a linear resistor. From (2.10) (or (2.11)) the memristance is equal to the slope of the  $q \phi$

curve. Therefore, a linear  $q - \phi$  would correspond to a device with a constant memristance which, from (2.16), will be indistinguishable from a constant linear resistor.

- continuously differentiable: This property ensures that the gradient, which represents the memristance, is uniquely defined at every point along the  $q \phi$  curve and it is finite ( $M(q) < +\infty$ ,  $\forall q$ ).

- strictly monotonically increasing: The strict monotonicity is imposed so that the  $q \phi$  curve always has a unique inverse such that (2.9) holds with the implications already explained above. Additionally, it makes sure that the memristance is positive and non-zero in order to guarantee strict passivity. A direct consequence of these restrictions is that the  $q \phi$  curve of an ideal memristor must be a one- to-one function. It is important to remark that, the *uniqueness* requirement is implied from this condition. Nevertheless, *uniqueness* was separately stated to highlight its importance. Similarly, the strict sense of this condition, even if not explicitly imposed, it is implied from continuously differentiable.

Finally, all the conditions together ensure that the constitutive relation (2.6) can be reexpressed both as an explicit function of q and  $\phi$  as in (2.7) and (2.8) respectively.<sup>5</sup>

#### 2.2 HP's ideal memristor model

The successful fabrication of HP's memristor is an important milestone in the timeline of memristors. The publication reporting its fabrication reignited the interest of the scientific community on the subject and also provided a simple but elegant ideal memristor model which has become a point of reference in the field [13]. Although this model describes an idealised memristor without detailed consideration for the underlying physical mechanisms, it can still reproduce the fundamental constitutive characteristics of a memristor's behaviour over a range of conditions. Indeed, both experimental i - v measurements [35] and theoretical predictions from more detailed models [116] show close resemblance to the responses of the HP model. Therefore, the HP model provides a simple, yet useful approximation, which is valid over given regimes or when a detailed description is unwarranted. The modelling ability of HP's memristor will be investigated further in Chapter5using experimental measurements from fabricated devices.

Because of its simplicity and its widespread use, this model will be extensively studied and analysed in Chapter4by applying the mathematical framework developed in Chapter3. It is therefore, introduced here together with a simple description of the underlying operation of the device. Additionally, based on the theory presented in the previous sections, it is shown why this model can be classified as an ideal passive memristor.

Having as an illustration Figure 2.4, the actual device consists of a thin-film semiconductor of TiO<sub>2</sub> (Titanium dioxide) with thickness *D* placed between two metal contacts made of Pt (Platinum) to form a metal/oxide/metal structure. The oxide film is divided into two regions: a doped region of thickness *w* with low resistance  $R_{ON}$  due to the high concentration of dopants (positive oxygen ions) and an undoped region with thickness (D - w) and high resistance  $R_{OF F}$ . The total resistance of the film is modelled by the weighted sum of two variable resistors in series with the first one ( $R_{ON}$ ) representing the doped region and the second ( $R_{OF F}$ ) the undoped. The ratio between the two is controlled by the position of the boundary between the doped and undoped regions which determines the value of *w*. Because of the extremely small dimensions of the device, when a voltage is applied a very strong electric field develops. This causes the oxygen vacancies to move towards (Figure 2.4c) or away from (Figure 2.4b) the doped region effectively changing the position of the boundary between the two regions and hence the total resistance of the device [13].

Assuming ohmic electronic conductance and linear ionic drift with average vacancy mobility  $\mu_{\nu}$ , the device is modelled by the following pair of equations [13]:

$$\dot{w} = i(t) \, \frac{\mu_v R_{on}}{D} \tag{2.14}$$

Integrating (2.25a) with respect to *t* yields:

$$w = \mu_v \frac{\mathsf{R}_{ON}}{D} q(t), \tag{2.15}$$

which reveals one of the basic assumptions of the model, namely, that the width of the doped region is proportional to the amount of charge that passes through the device. Models, like HP's, in which the rate of change of the internal state variable is a linear function of the input (i.e.  $z = \kappa u(t)$ ), will be referred to as *linear models*.

A comparison of HP's model with (2.20) shows that it actually complies with the definition of the current-driven memristive system with *w* acting as the internal state variable. However, inserting (2.26) in (2.25b) eliminates the internal state variable *w* and brings (2.25b) in a form complying with the current-driven charge-controlled memristor:

$$v = M(q)i(t) = \left[Roff + (Ron - Roff)\frac{\mu_v R_{on}q}{D^2}\right]i(t) \quad (2.16)$$

This is an example of a 'hidden memristor' case as described in the previous section. Reducing (2.25) in the canonical form of a memristor is not conclusive as to whether the model represents an ideal memristor or not. Because memristors are uniquely defined on the  $q - \phi$  plane, one needs to evaluate the  $q - \phi$  representation of (2.27) first, by applying (2.24) and then verify whether the conditions (2-1.1)-(2-1.4) are satisfied. Applying (2.24) on (2.27) gives the charge-controlled representation of the model:

$$q(\phi) = \left[Ro + \frac{\mu_{\nu}R_{on}}{D^2}(Ron - Roff)\frac{q^2}{2}\right] \quad (2.17)$$

Evaluating its inverse gives the flux-controlled representation:

$$q(\phi) = \frac{-RonD^2 \pm D\sqrt{Ro^2D^2 + 2\mu_v R_{on}(Ron - Roff)\phi}}{\mu_v R_{on}(Ron - Roff)}$$

(2.18)

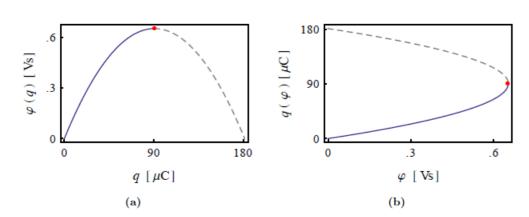

As shown in Figure 2.5a, equation (2.28) satisfies all the conditions for an ideal passive memristor except monotonicity, hence, its inverse (2.29) which is shown in Figure 2.5b is not uniquely defined. However, if the operation of the model is restricted within the strictly increasing region of  $\phi(q)$ , as indicated by the solid line sections of the curves in

Figure 2.5: (a) A plot of the flux with respect to the charge,  $\varphi(q)$ , as given by (2.28) and (b) its inverse,  $q(\varphi)$ , as given by (2.29). It is clear from (a) that (2.28) violates the requirement (2-1.4) for monotonicity, hence its inverse cannot be uniquely defined. In fact, it is a double valued function of  $\varphi$ . Therefore,  $\varphi(q)$  will represent an ideal passive memristor only if the operation of HP's model is limited within its strictly increasing region as indicated by the solid line in (a). This results to a unique inverse, indicated by the solid line in (b). Parameters used:  $i = i_0 \sin(\omega_0 t)$  with  $i_0 = 100\mu$ A and  $\omega_0 = \pi$ ,  $\mathcal{R}_{ON} = 100\Omega$ ,  $\mathcal{R}_{OFF} = 16\mathrm{k}\Omega$ ,  $\mu_v = 10^{-14}\mathrm{ms}^{-1}\mathrm{V}^{-1}$ ,  $D = 10\mathrm{nm}$  and  $w_0/D = 0.1$ .

Figure 2.3, represents an ideal passive memristor. For the parameters reported by HP for their device [13], and by limiting operation such that  $0 \le w \le D$  and  $R_{ON} \le M(q) \le R_{OF}$ *<sub>F</sub>*, the model satisfies all the criteria for an ideal passive memristor. Therefore, the flux-controlled representation (2.29) can be uniquely defined and will be given by the solution with the positive branch of the square root.

### **Chapter 3**

## **Different models of window function**

45

#### 3.1 Unsuitable window functions

The memristor model introduced by HP and discussed in the previous section assumes that the memristance in (2.25b) varies linearly with the internal state variable w which represents the width of the doped region (see Figure2.4). This assumption is not very restrictive since any nonlinearities can still be accounted for by the dynamics of the internal state variable in (2.25a). However, from (2.25a), the original model assumes linear ionic drift, namely, that the position of the boundary changes linearly with the input. In general, the second assumption does not reflect reality. There are clear evidence that the vacancy drift is highly nonlinear especially close to the two boundaries of the device [13,25,77,116,117,124]. This renders the model unsuitable for detailed

modelling of most practical devices.

As discussed in Chapter1, due to the diversity of resistance switching devices found and their extremely small dimensions which make them difficult to study, a universal detailed physical model based on the underlying physical mechanisms is difficult to obtain, especially with no standardised memristor technology in place [75,121,125]. To avoid this problem, the group at HP introduced the so called *window function* approach in which an empirical macroscopic function is used with the aim of modelling the nonlinear ionic drift observed at the boundaries of their fabricated device [13]. The simplicity of this approach motivated several groups to follow the same trend by introducing other window functions offering different and improved properties [7,121–123]. Because the majority of groups working on memristors and their applications have no access to a real device, the window approach provides a convenient alternative description for use in their modelling [121,125,133].

The window functions discussed next comply with the following general properties:<sup>7</sup>

**3.1.1**  $f: [0, 1] \rightarrow [0, 1],$

**3-1.2** f(0) = f(1) = 0,

**3-1.3** single maximum  $f(z_{max}) = 1$ .

These properties essentially describe a strictly concave [134] function for  $z \in [0, 1]$  which is increasing from its first root at z = 0 until the maximum at  $z = z_{max}$  and then decreasing until the second root at z = 1. In practice a window function satisfying these specifications results to z being maximised at  $z = z_{max}$  and minimised as  $z \to 0$  or  $z \to 1$ .

The models also assume that the memristance, M(z), is equal to the weighted sum of two resistances, the maximum ( $R_{OFF}$ ) and the minimum ( $R_{ON}$ ) resistance values to which the device can be configured. The ratio between the two resistances is determined by the value of the internal state variable *z*. Therefore, the effective resistance of the device is a linear function of *z* and is described by:

$$\mathbf{M}(z) = z\mathbf{R}_{\rm ON} + (1-z)\mathbf{R}_{\rm OFF},\tag{3.1}$$

in exactly the same way as it was defined for HP's ideal memristor in (2.15) [13]. By modelling the memristance as in (2.12) the memristive character of the system will be reflected in the dynamics (2.13a) of the state variable z.

The first window function was introduced by the group at HP and it has the following form [13]:

$$f(z) = z(1-z),$$

(3.2)

with z = w/D as in (2.25). This was incorporated as a factor in the state equation of the original model (2.25a), resulting to the modulated dynamics of *w*:

Equation (2.33) was subsequently generalised by Joglekar and Wolf to [7]:

$$f(z;p) = 1 - (2z - 1)^{2p},$$

(3.3)

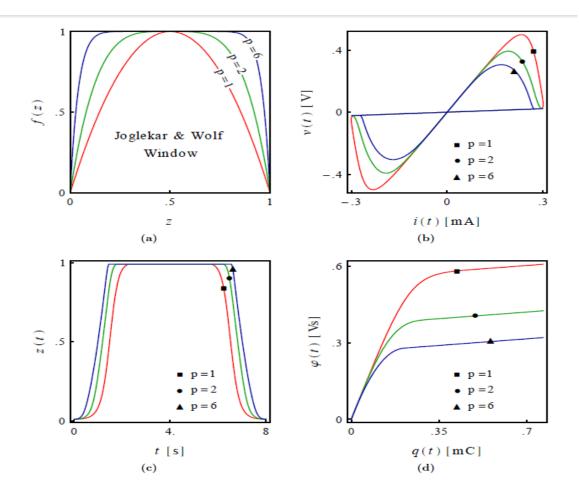

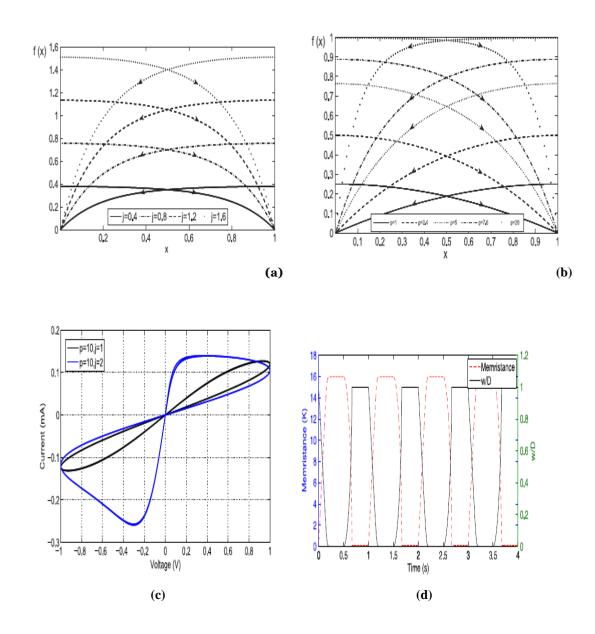

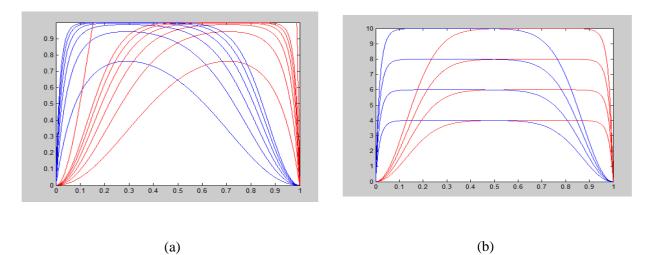

where  $p \in \mathbb{Z}^+$ . Unlike Strukov's *et al* window in (2.33) which assumes nonlinear drift everywhere in the range of  $z \in [0, 1]$ , (2.35) is able to model both the linear drift around the midrange of z and the nonlinear drift close to the boundaries using the control parameter p. This parameter changes the flatness of the curve around its maximum, which occurs at  $z_{max} = 1/2$ . Figure2.6illustrates the behaviour of (2.35) for some representative values of p. It is clear that as p increases,  $f(z; p) \approx 1$  for a larger range of z which corresponds to linear drift. In terms of the model's response, a higher p value represents a device which requires a smaller amount of charge (or flux) to be injected in order to reach saturation

Prodromakis et al suggested a revised version of (2.13) with similar properties [122]:

$$f(x) = 1 - ((x - 0.5)^2 + 0.75)^{2p}$$

(3.4)

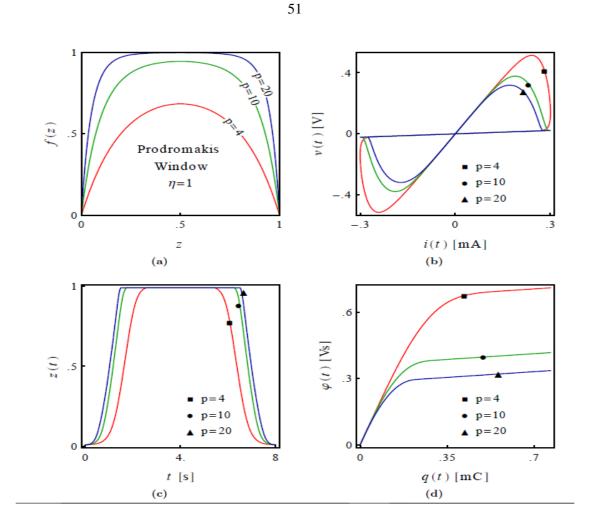

The difference of this window function is that it allows the maximum  $f_{max}$  to take any value between 0 and 1. The value of the maximum, which again occurs at  $z_{max} = 1/2$ , as well as the flatness around it, are controlled by the parameter  $p \in \mathbb{R}^+$ . The parameter  $\eta \in \mathbb{R}^+$  is a scaling factor used to compensate for the situations where  $f_{max}(z_{max})$   $\mathbf{f}=1$ . The behaviour of this window function is illustrated in Figure 2.7.

It is important to note here that the resulting  $q - \phi$  curves for both window functions, (2.35) and (2.36), satisfy the requirements for an ideal passive memristor (2-1.1-2-1.4). The  $q - \phi$  curves of the two windows are shown in Figure 2.6 dand Figure 2.7 drespectively. As an example, AppendixBpresents the detailed steps for obtaining the voltage output and its  $\phi(q)$  function for HP's model using the window in (2.33). This procedure will be discussed in more detail in Chapter 5 through sigmoidal functions.

Finally, the parameters used for generating Figures2.6,2.7and2.8are the following:  $i = i_0 \sin(\omega_0 t)$  with  $i_0 = 0.3$ mA and  $\omega_0 = \pi/4$ ,  $h(i) = \alpha i(t)$  where  $\alpha = \mu_v R_{ON}/D^2$ ,  $\mu_v = 10^{-14}$ ms<sup>-1</sup>V<sup>-1</sup>, D = 10nm,  $R_{ON} = 50\Omega$  and  $R_{OF F} = 2.5$ k $\Omega$ .

#### 3.2 Practical implementation issues

The models resulting by incorporating the above window functions will suffer from two major issues, namely, the *terminal state problem* and the *accumulation* of charge (or flux). The first one arises specifically when using the type of window functions presented here, while the second issue is more general and may appear in any model. Any practical implementation of such models needs to have a strategy for overcoming both of these obstacles [22,121,125,126,133].

The *terminal state problem* stems directly from the specifications (2-2.1)-(2-2.3) imposed on the window functions and in particular (2-2.2). Due to this property, if the initial condition is chosen to be  $z(0) = z_0 = 0$  or 1, then the model will remain at  $z_0$  indefinitely irrespective of any subsequent input applied [22,121]. The consequence of this limitation is that the model cannot have as initial resistance state any of the two

**Figure 3.1:** The behaviour of Joglekar et al window function) under a sinusoidal input current for different values of its control parameter p. In particular, the figure shows the effect of p on (a) the form of the window f(z), (b) its i-v response, (c) the dynamics of the internal state variable z and (d) the resulting form of the '(q) curve. From (a) it is clear that as the value of p increases, f(z) becomes more at around its maximum which occurs at  $z_{max} = 0.5$  and eventually tends to a constant. As shown in (c), assuming the same input, a wider region for which f(z) = 1 causes the device to saturate faster, or equivalently as shown in (d), for a smaller amount of charge. The saturation region is also evident in (b) and corresponds to the linear part of the i - v response.

limiting resistances,  $R_{ON}$  or  $R_{OFF}$ . The model fails because when solving (2.31a) for obtaining *z* the solution involves an integration over the reciprocal of f(z): 1/f(z)dz. The function 1/f(z) is asymptotic at z = 0 or z = 1 rendering the above integral divergent at the two boundaries and hence undefined at these two initial conditions (see Figure2.9b).

Regardless of whether a window function is used or not, an additional issue which needs to be taken into account during the development of a model is the *accumulation* of charge (or flux). The resistance of such devices varies only within a limited range of resistance values bounded by a minimum ( $R_{ON}$ ) and a maximum ( $R_{OFF}$ ) resistance value. When the device reaches any of the two boundary values it switches from the memristive regime to that of a linear resistor until the polarity of the input is reversed. While in saturation, the input signal has no effect on the memristance, hence, the system loses its memristive character and all the properties that come with it (e.g. memory). Therefore, a mechanism must be incorporated in the model which will temporarily 'freeze' the integration over the input until the device returns back to the memristive regime. This mechanism will account for the fact that the device looses its ability to remember the amount of input applied while in saturation [86,87,125].

The window functions presented until now impose a restriction on the range of z such that 0 < z < 1. However, due to the terminal state problem, this restriction is not effective on limiting the charge (or flux) as well. As a result of this 'half measure', when the system is in saturation the memristance changes only by an infinitesimal amount but the model keeps accumulating charge (or flux) [22,121]. In other words, the integral over the input signal does not stop during saturation because z is never exactly equal to 0 or 1 when starting from any initial condition  $0 < z_0 < 1$ . The excess charge (or flux) accumulated after saturation needs to be cancelled when the polarity of the input is reversed although it did not contribute to any change in the memristance. This introduces an unrealistic delay in the response of the system.

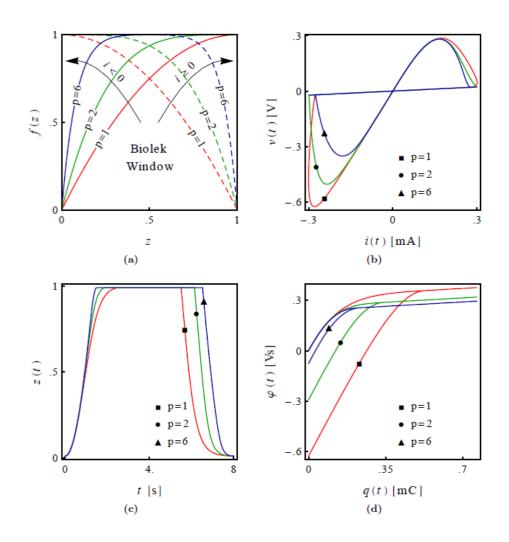

To deal with both of these problems Biolek *et al* dropped the compliance with prop- erty (2-2.2) and introduced the following piecewise window whose form depends on the polarity of the input [121]:

$$f(z, i; p) = 1 - (z - \operatorname{stp}(-i))^{2p}, \qquad (3.5)$$

where stp(i) = 1 for  $i \ge 0$  and 0 otherwise. Its control parameter, *p*, is used to adjust the flatness of the window around the maximum in a similar way to(2.15).