# NEW EFFICIENT AC-DC CONVERTERS AND THEIR APPLICATIONS

by

# Khalid Saifullah (132407) Md. Abdullah-Al-Hysam (132434) Md. Zihad Ul Haque (132445) Sakif Asif (132484)

A Thesis Submitted to the Academic Faculty in Partial Fulfillment of the Requirements for the Degree of

## BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT)

Gazipur, Bangladesh

# NEW EFFICIENT AC-DC CONVERTERS AND THEIR APPLICATIONS

Approved by:

-----

### Dr. Golam Sarowar

Supervisor and Assistant Professor,

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Board Bazar, Gazipur-1704 Bangladesh.

Date: 10-11-2017

## **Table of Contents**

| Li | st of                  | Figures                                               | IV  |  |

|----|------------------------|-------------------------------------------------------|-----|--|

| Li | st of                  | Tables                                                | VI  |  |

| A  | ckno                   | wledgements                                           | VII |  |

| 1  | Abs                    | Abstract                                              |     |  |

| 2  | Introduction           |                                                       | 2   |  |

|    | 2.1                    | FUNDAMENTALS OF POWER ELECTRONICS                     | 2   |  |

|    | 2.2                    | TYPES OF AC-DC CONVERTERS                             |     |  |

| 3  | Related Field Study    |                                                       |     |  |

|    | 3.1                    | BUCK-BOOST CONVERTER                                  |     |  |

|    | 3.2                    | CUK CONVERTER                                         |     |  |

|    | 3.3                    | SEPIC-CUK COMBINATION CONVERTER                       |     |  |

| 4  | Proposed Circuits      |                                                       |     |  |

|    | 4.1                    | PRINCIPLE OF OPERATION                                |     |  |

|    | 4.2                    | VOLTAGE GAIN ANALYSIS                                 |     |  |

|    | 4.3                    | EFFICIENCY ANALYSIS                                   | 53  |  |

|    | 4.4                    | APPROACH TO MODEL A NEW CONVERTER                     | 54  |  |

| 5  | Simulation and Results |                                                       | 55  |  |

|    | 5.1                    | ASSUMPTIONS                                           | 55  |  |

|    | 5.2                    | COMPARATIVE ANALYSIS                                  | 55  |  |

| 6  | Application            |                                                       | 63  |  |

|    | 6.1                    | GRID CONNECTED PHOTOVOLTAIC SYSTEM                    |     |  |

|    | 6.2                    | WORKING PRINCIPLE OF THE WHOLE SYSTEM                 |     |  |

|    | 6.3                    | VARIOUS PARAMETER COMPARISON WITH EXISTING GENERATORS |     |  |

|    | 6.4                    | COST ESTIMATION                                       | 68  |  |

| 7  | Conclusion             |                                                       | 70  |  |

| 8  | Published Papers       |                                                       | 73  |  |

| 9  | Reference              |                                                       | 74  |  |

# LIST OF FIGURES

Fig. 2.1 A general power electronic system Fig. 2.2 Power electronics and related topics Fig. 2.3 Power electronics and electrical energy generation transmission, storage, and distribution Fig. 2.4 Ideal switch Fig. 2.5 4-quadrant switch v-i characteristics switch Fig. 2.6 Diode: a symbol, b i-v characteristics, and c idealized characteristics Fig. 2.7 Thyristor: a symbol, b i-v characteristics, and c idealized characteristics Fig. 2.8 The triac: a symbol, b two-thyristor-representation, c i-v characteristics, and d idealized characteristics Fig. 2.9 The BJT: a symbol, b *i-v* characteristics, and c idealized characteristics Fig. 2.10 The MOSFET: a symbol, b *i-v* characteristics, and c idealized characteristics Fig. 2.11 The IGBT: a symbol, b i-v characteristics, and c idealized characteristics Fig. 2.12 The GTO: a symbol, b *i-v* characteristics, and c idealized characteristics Fig. 2.13 The MCT: a symbol, b *i-v* characteristics, and c idealized characteristics Fig. 2.14 Generalized circuit for DC/DC converter circuits Fig. 2.15 Non-isolated down (buck) DC/DC converter: a circuit and b waveforms Fig. 2.16 Full-bridge non-isolated down (buck) DC/DC converter: a circuit, and b waveforms Fig. 2.17 Non-isolated boost (up) DC/DC converter: a circuit, and b switch implementation Fig. 2.18 The buck-boost (up/down) non-isolated DC/DC converter: a circuit, and b switch implementation Fig. 2.19 Full bridge (FB) DC/AC converter: a circuit, and b waveforms Fig. 2.20 Half-bridge (HB) DC/AC converter (inverter): a circuit, and b waveforms Fig. 2.21 Full-bridge (FB) DC/AC converter with variable AC voltage: a circuit, and b waveforms Fig. 2.22 Active filtering using harmonic elimination: a circuit, and b waveforms Fig. 2.23 Pulse-width modulation (PWM) switching technique: a multiple harmonic elimination, b PWM circuit, c PWM AC output, d PWM generation, and e PWM signal Fig. 2.24 Three-phase AC/DC converter: a circuit, b waveforms, and c connections Fig. 2.25 Six-step inverter and waveforms: a circuit, b switch implementation, and c waveforms Fig. 2.26 Current source inverter (CSI) Fig. 2.27 Classifications of rectifier circuits Fig. 2.28 a General 1-phase rectifier circuit, b 1-phase controlled rectifier, and c Input and output voltage waveforms Fig. 2.29 Examples of uncontrolled rectifiers: a full-bridge (FB), and b waveforms Fig. 2.30 three-phase, 3-pulse rectifier circuit: a circuit and b waveforms Fig. 2.31 6-pulse rectifier circuits: a Y-connected source, and b D-connected source Fig. 2.32 12-pulse rectifier circuits: a high voltage 12-pulse rectifier, and b high current 12- pulse rectifier Fig. 2.33 PWM rectifier: a single-phase, and b three-phase Fig. 2.34 Single-phase PWM rectifiers Fig. 2.35 Implementation of the three-phase VSR Fig. 2.36 Variable voltage fixed frequency (VVFF) AC/ AC converter Fig. 2.37 Cyclo-converter as VVVF AC/AC converters Fig. 2.38 Integral-cycle control for (VVVF) AC/AC converter Fig. 2.39 FVFF to VVVF AC/AC converter through a DC link Fig. 2.40 Implementation of a FVFF to VVVF AC/AC converter through a DC link Fig. 2.41 Generalized matrix converters Fig. 2.42 Examples of converters derived from the matrix converter: a AC/AC, b AC/DC, and c AC/DC and DC/DC Fig. 2.43 Implementation of a fully bidirectional switch Fig. 2.44 Implementation of a three-phase AC/AC converter Fig. 2.45 Multilevel inverter: a generalized multi-level converter, b generalized waveforms, c NPC inverter, d flying capacitor inverter, e H-bridge cascaded inverter, and f NPC line voltage waveform Fig. 2.46 Slow variable controller Fig. 2.47 Voltage control of a boost converter Fig. 2.48 Block scheme for both slow and fast variable control Fig. 2.49 CCM: a hysteresis control, b current peak control, and c average current control

- Fig. 2.49 CCWI. a hysteresis control, b current peak control, and c average curre

- Fig. 2.50 Generalized control strategy applied to power converters

- Fig. 2.51 Voltage current controlled PWM rectifier

- Fig. 2.52 Space-vector control scheme

Fig. 2.53 Two principles of PWM modulators: a variation of the control voltage and saw-tooth carrier with constant slope, and b variation of the carrier amplitude

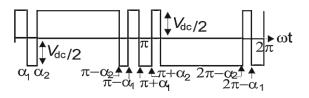

Fig. 2.54 Selective harmonic elimination PWM

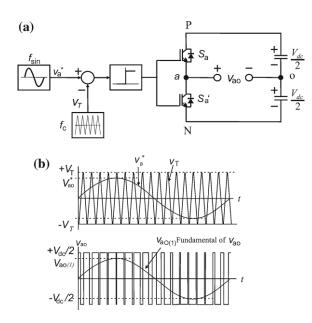

Fig. 2.55 Sinusoidal PWM a bipolar voltage switching for half-bridge inverter, b control signals (*upper*) and pole voltage (*lower*)

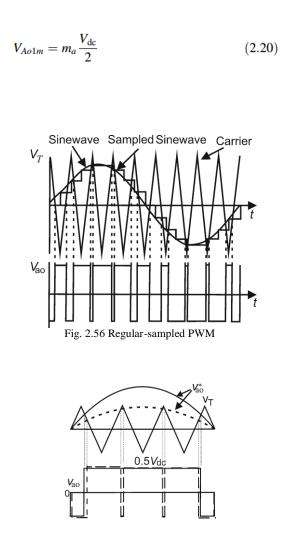

Fig. 2.56 Regular-sampled PWM

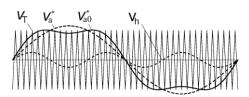

Fig. 2.57 Operation in over modulation region

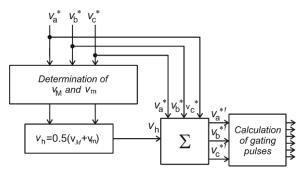

Fig. 2.58 Operation in over modulation region—non-sinusoidal PWM: sinusoidal reference, *vma*, modulating signal generated, *vmao*; and zero-sequence signal *vh* (*middle*) for the THIPWM strategy

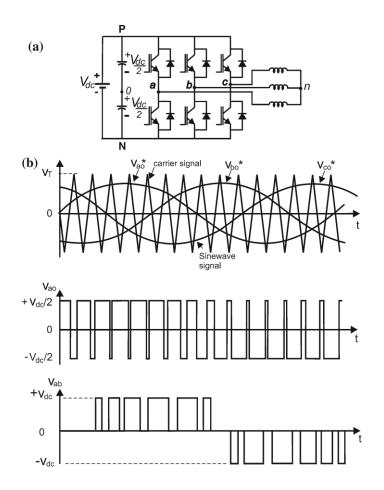

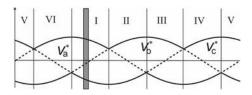

Fig. 2.59 Three-phase sinusoidal PWM: a inverter circuit, b principle, pole voltage, and inverter output voltage Fig. 2.60 Sectors inside one period

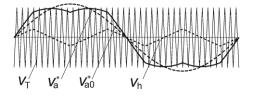

Fig. 2.61 Operation in over modulation region-non-sinusoidal PWM: vma; modulating signal generated,

vmao; and zero-voltage signal vh (middle) generated for Symmetric PWM

Fig. 2.62 Pole voltage pulse width inside a switching interval

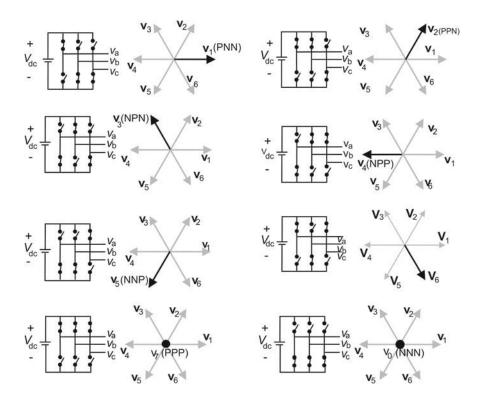

Fig. 2.63 Relation of the inverter switching configurations and the state vectors

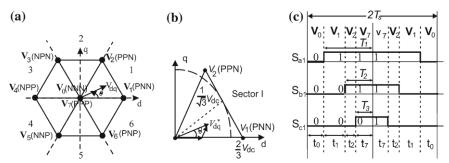

Fig. 2.64 a Space vector diagram and sector definition, b synthesis of the reference state vector in *Sector I* using switching vectors  $\sim V0$ ;  $\sim V1$ ;  $\sim V2$ ; and  $\sim V7$ , and c switching pattern

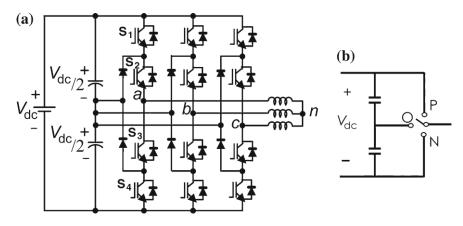

Fig. 2.66 a Three-level NPC inverter topology and b equivalent circuit

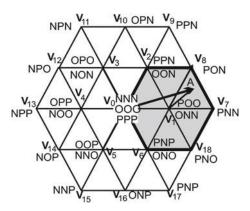

Fig. 2.67 Space vector diagram of a three-level converter

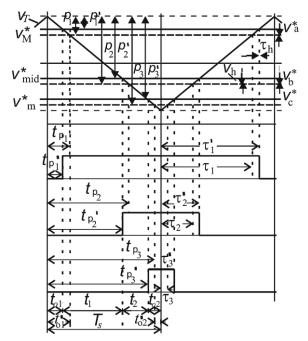

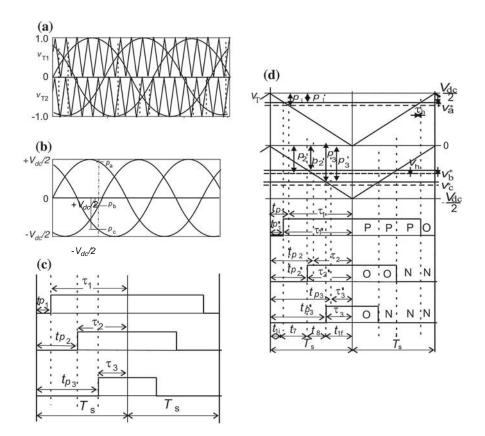

Fig. 2.68 Three-level inverter: a modulation principle (IPD), b definition of pi (i = 1, 2, 3),

c the relation of pi with the pulse delays in the switching interval tpi, and d the switching interval

considering the addition of the zero-sequence signal, vh

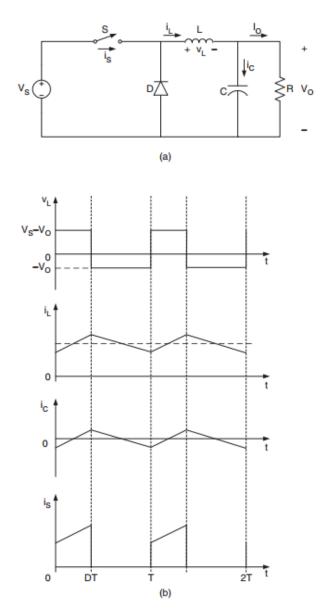

Fig. 2.69: Buck converter: (a) circuit diagram and (b) waveforms.

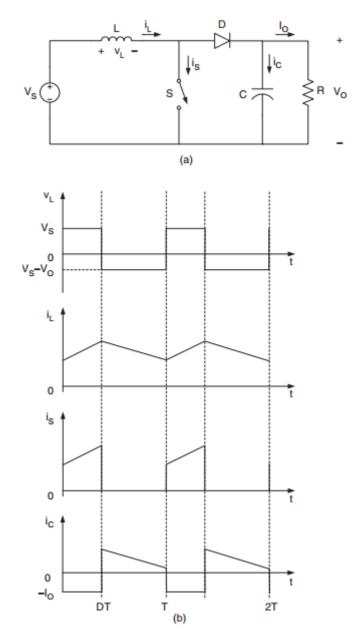

Fig. 2.70: Boost converter: (a) circuit diagram and (b) waveforms.

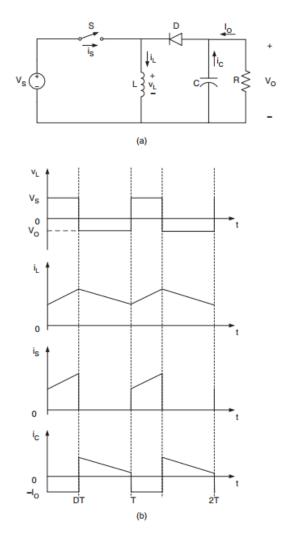

Fig. 2.71 Buck–boost converter: (a) circuit diagram and (b) waveforms.

Fig. 2.72: Cuk converter: (a) circuit diagram and (b) waveforms.

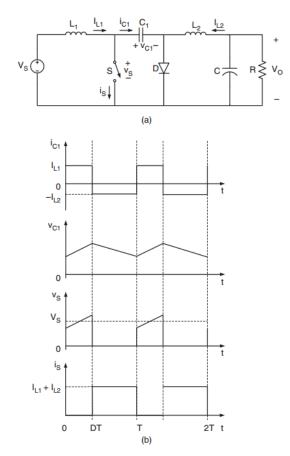

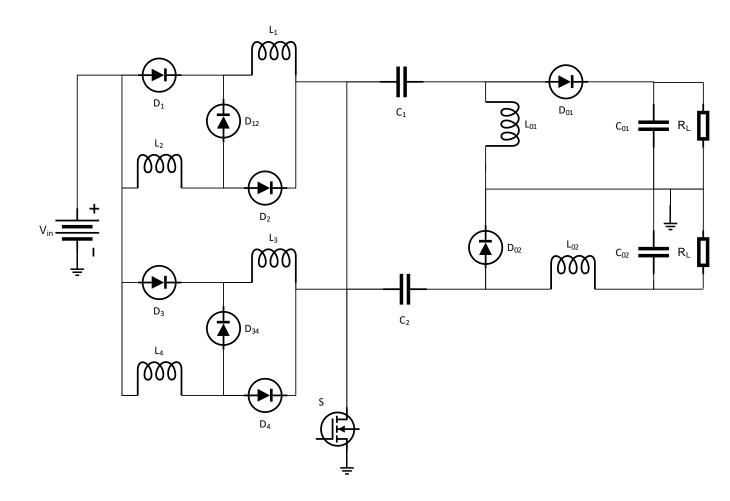

Fig. 4.1: Single Stage Switched Capacitor Network

Fig. 4.2: Proposed Double Stage Switched Capacitor Network

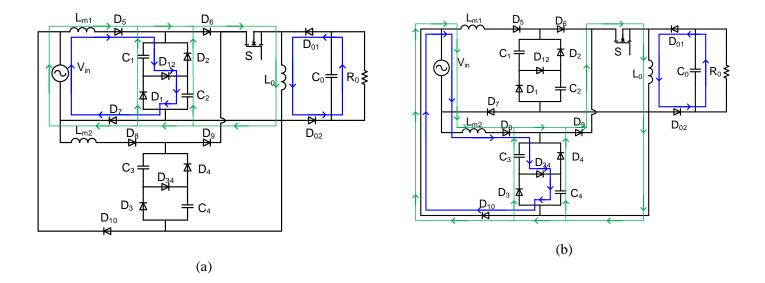

Fig. 4.3: Operation Principles of Double Stage Switched Capacitor Network (a)Positive half cycle (b)Negative half cycle (Ton = Green, Toff = Blue)

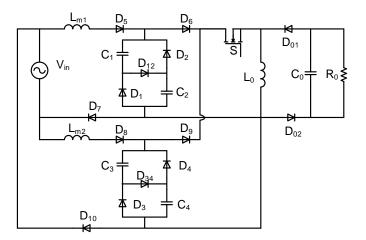

Fig. 4.4: Proposed Topology with (a)Single Switched Capacitor Network (b)Two Switched Capacitor Network

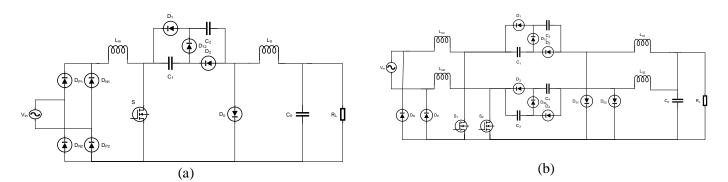

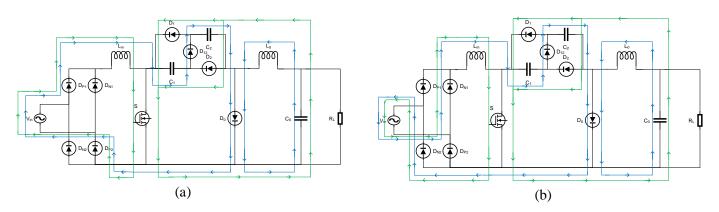

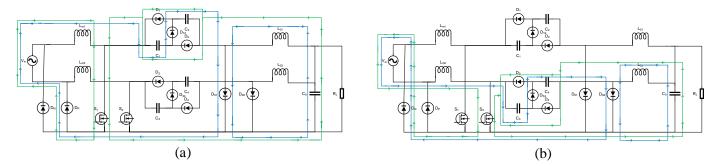

Fig. 4.5: Operation Principles of Single Switched Capacitor Network (a)Positive half cycle (b)Negative half cycle (Ton = Green, Toff = Blue)

Fig. 4.6: Operation Principles of Two Switched Capacitor Network (a)Positive half cycle (b)Negative half cycle (Ton = Green, Toff = Blue)

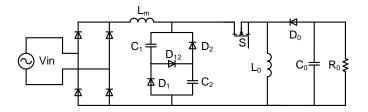

Fig. 4.7: Bipolar DC Link Based on SEPIC-Cuk Combination

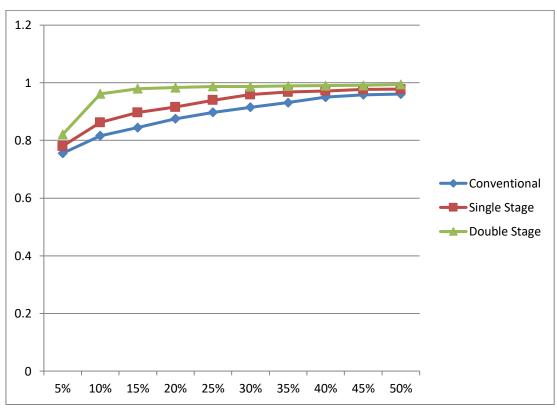

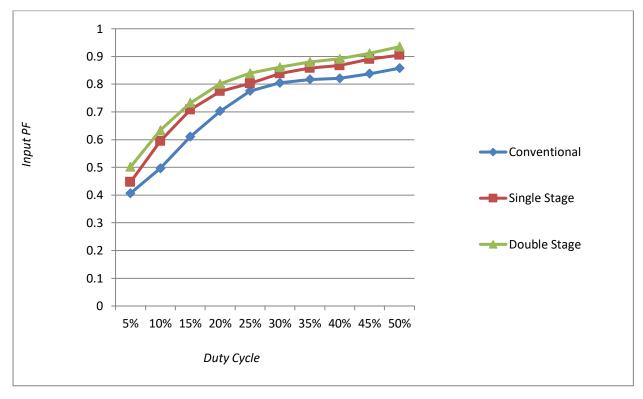

Fig. 5.1: Input PF Comparison of Different Buck-Boost Converters

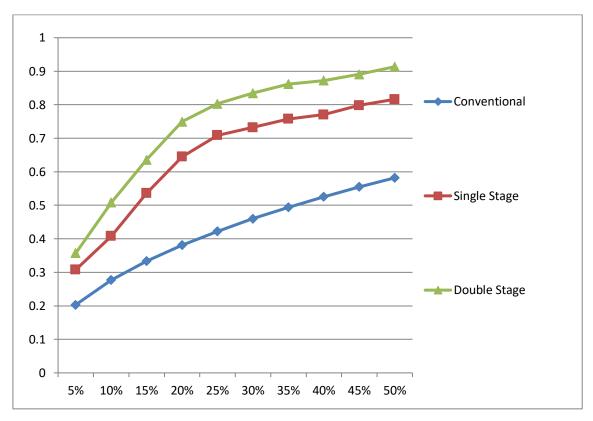

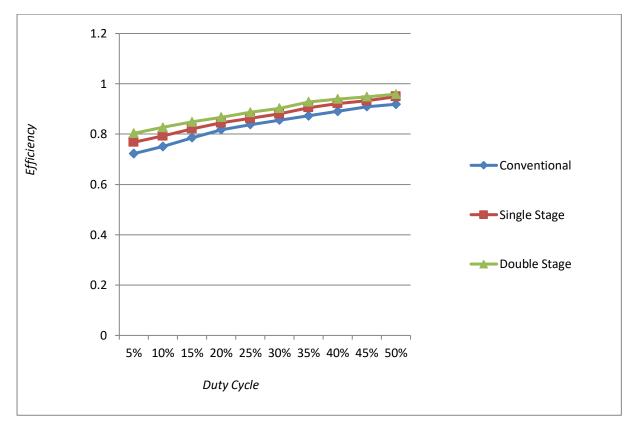

Fig. 5.2: Efficiency Comparison of Different Buck-Boost Converters

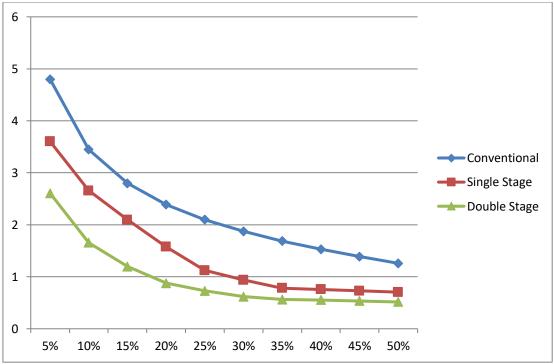

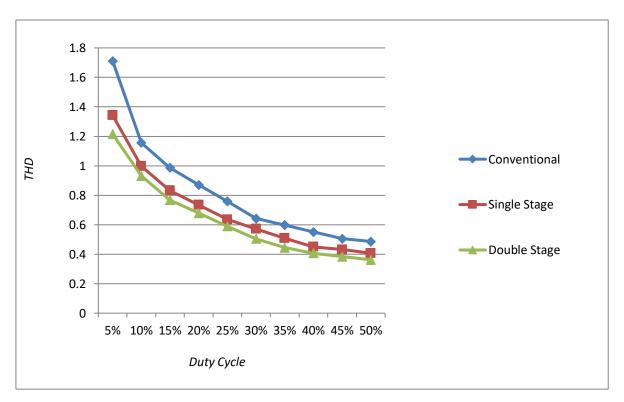

Fig. 5.3: THD of Input Current Comparison of Different Buck-Boost Converters

Fig. 5.4: Input PF Comparison of Different Cuk Converters

Fig. 5.5: Efficiency Comparison of Different Cuk Converters

Fig. 5.6: THD of Input Current Comparison of Different Cuk Converters

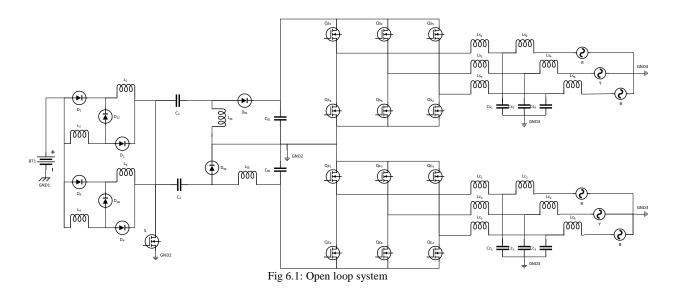

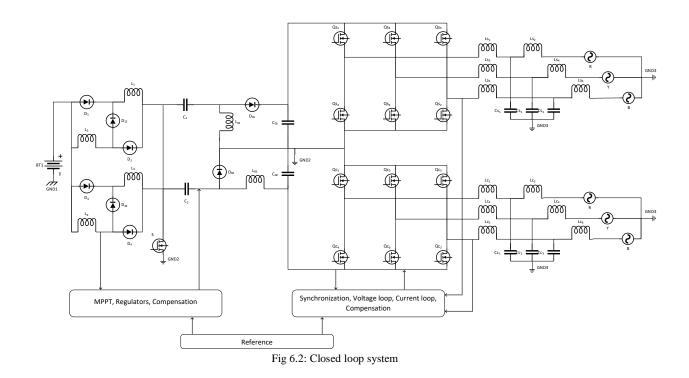

Fig 6.1: Open loop system

Fig 6.2: Closed loop system

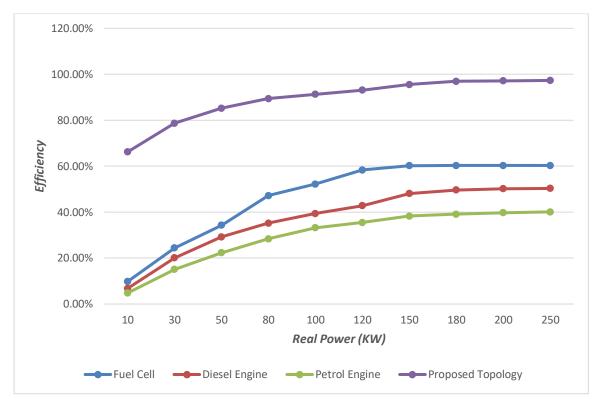

Fig. 6.3: Efficiency comparison of existing generators

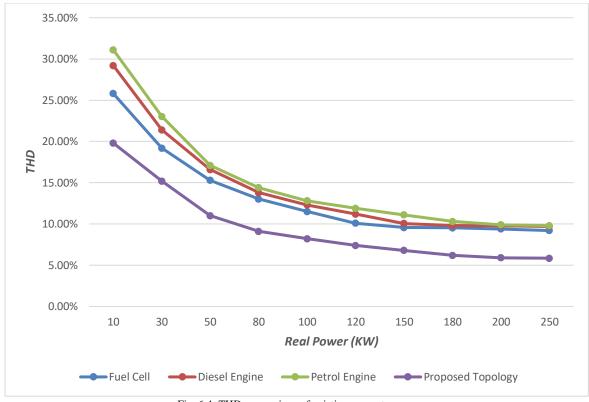

Fig. 6.4: THD comparison of existing generators

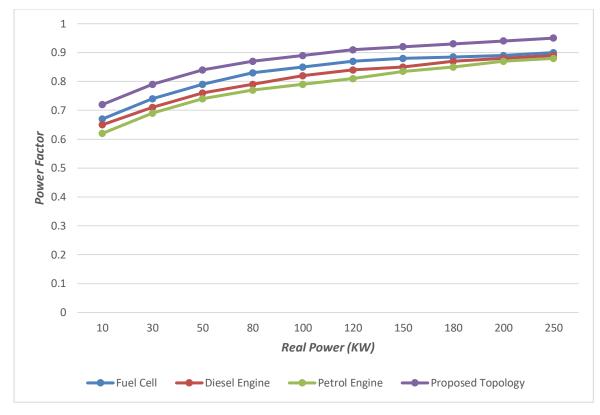

Fig. 6.5: PF comparison of existing generators

# LIST OF TABLES

Table 5.1: Input PF Comparison of Different Buck-Boost Converters

Table 5.2: Efficiency Comparison of Different Buck-Boost Converters

Table 5.3: THD of Input Current Comparison of Different Buck-Boost Converters

Table 5.4: Input PF Comparison of Different Cuk Converters

Table 5.5: Efficiency Comparison of Different Cuk Converters

Table 5.6: THD of Input Current Comparison of Different Cuk Converters

Table 6.1: Efficiency comparison of existing generators

Table 6.2: THD comparison of existing generators

Table 6.3: PF comparison of existing generators

Table 6.4: Cost estimation

Table 6.5: Estimated power supply to various loads

# Acknowledgements

We wish to express our deepest gratitude to our academic and research advisor **Dr. Golam Sarowar**, Assistant professor, Department of EEE, IUT for his continuous guidance, supervision and invaluable suggestions during the entire project work. We also wish to acknowledge and express our appreciation to friends and others who directly or indirectly helped with, worth suggestions and information in completing this project. Finally, we thank the Electrical and Electronic Engineering Department Laboratory personnel for their patient assistance during the period of the project work.

# **Chapter 1**

# Abstract

AC-DC converters are mostly used as power supplies for microelectronic systems, battery chargers, wind energy applications, electric appliances in household and dc motor drives. Switched-capacitor (SC) network based converters can be good solution to the challenges of 21st century having high voltage conversion ratio and low EMI emissions. The application of this type of converters is in microprocessor based systems where the line voltage requires a steep step down to 3V or even less in order to drive integrated circuits (ICs). In this paper, a new high step down bridgeless single switch AC-DC converter with switched capacitor is proposed. The absence of transformer as well as bridge rectifier reduce the components count, size and cost of the converter. Unlike the existing converters, this proposed buck boost converter is able to achieve simple control structure with single switch, high efficiency, low total harmonic distortion (THD) and high input power factor.

Power supplies for microelectronic systems, battery chargers, wind energy applications, electric appliances in the household and dc motor drives require AC-DC converters. The proposed bridgeless Cuk PFC converter in this paper is featured with common ground, transformerless structure, and clear energy delivery process. The absence of bridge rectifiers, transformer and the presence of only two semiconductor switches in the current flowing path during each switching cycle result in less conduction losses and improved thermal management, reducing components count, size and cost of the converter compared to the conventional SEPIC and Cuk PFC converters. Moreover, the presence of two power switches for different half cycles leads to less stress on the power switch. Unlike the existing converters, this proposed bridgeless Cuk PFC converter is able to achieve simple control structure with high efficiency, low total harmonic distortion (THD) and high input power factor.

This letter describes a new application of single-ended primary converter (SEPIC) and Cuk converter for dc bipolar net-work. A dc–dc converter configuration based on a combination of both converters is proposed. In the resulting topology, the switching node is shared by the SEPIC and Cuk converter since they have the same instantaneous duty cycle. The main advantage of this topology is that synchronization of various switches is not required, and control terminal is connected to ground which simplifies the design of the gate drive. On the other hand, this configuration allows the connection of renewable energy sources to microgrids (MG)-type bipolar dc link and to cover the current needs of new distributed generation units with efficient, economical, and easy way. To verify its performance, a prototype was designed. Experimental results show as this combination of two converter topologies with appropriated modulation schemes are adequate to use in dc MG.

# **Chapter 2**

# Introduction

## 2.1 Fundamentals of Power Electronics

This chapter gives a description and overview of power electronic technologies including a description of the fundamental systems that are the building blocks of power electronic systems. Technologies that are described include: power semiconductor switching devices, converter circuits that process energy from one DC level to another DC level, converters that produce variable frequency from DC sources, principles of rectifying AC input voltage in uncontrolled DC output voltage and their extension to controlled rectifiers, converters that convert to AC from DC (inverters) or from AC with fixed or variable output frequency (AC controllers, DC–DC–AC converters, matrix converters, or cyclo- converters). The chapter also covers control of power converters with focus on pulse width modulation (PWM) control techniques.

## 2.1.1 Definition, History, Applications and Trends of Power Electronics

Power electronics (PE) experienced tremendous growth after the introduction of the first solid-state power switch, the silicon controlled rectifier (SCR) in 1957. Today, almost all of the technologies that require control of power control utilize PE technology. This chapter will give the reader an overview on the field of PE including:

- A description of the fundamentals of the power semiconductor switching devices.

- Converter circuits that process energy from one DC level to another DC level.

- Converters that produce variable frequency from DC sources.

- Principles of rectifying AC input voltage in uncontrolled DC output voltage and their extension to controlled rectifiers.

- Converters that convert to AC from DC (inverters) or from AC with fixed or variable output frequency.

- AC controllers.

- DC–DC–AC converters.

- Matrix converters or cyclo-converters.

- Detailed description of pulse width modulations control techniques.

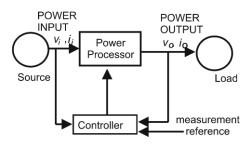

Power electronic circuits are used to control the power conversion from one or more AC or DC sources to one or more AC or DC loads, and sometimes with bidirectional capabilities. In most power electronics systems, this conversion is accomplished with two functional modules called the control stage and the power stage. Figure 2.1 shows the topology for a single source and single load converter application that includes a power processor (the power stage) and a controller (the control stage). The converter, handles the power transfer from the input to output, or vice versa, and is constituted of power semiconductor devices acting as switches, plus passive devices (inductor and capacitor). The controller is responsible for operating the switches according to specific algorithms monitoring physical quantities (usually voltages and currents) measured at the system input and or output.

The modern PE era began in 1957. It was during that year the first commercial thyristor, or Silicon Controlled Rectifier (SCR), was introduced by General Electric Company. The SCR, started replacing the mercury arc rectifiers, invented in 1902, and the later developed thyratron (invented in 1923) and ignitron (invented in 1931), allowed the commercialization of several industrial circuits conceived during the 1920s and 1940s (like the cyclo-converter, the chopper, and the parallel inverter) as well as the Graetz bridge conceived in 1897.

The SCR was the only available power device for more than 25 years after its invention (and still is very useful for extremely high power applications). Since it is very difficult to impose turn-off conditions for SCR's, faster devices, with higher voltage and current capabilities, with better controllability were developed,

Fig. 2.1 A general power electronic system

including the bipolar junction transistor (BJT) invented in 1970. The BJT was used in applications from low to medium power and frequency and now is considered obsolete. The metal oxide semiconductor field effect transistor (MOSFET) was invented in 1978 and is used for power electronic switching applications of low power and high frequencies. The gate turn-off thyristor (GTO), is used in applications from medium to high power and from low to medium frequencies. The insulated gate bipolar transistor (IGBT) developed in 1983 is used in applications from low to medium power and frequency. The integrated gate commutated thyristor (IGCT) invented in 1997 is used in applications from medium to high power and from low to medium frequencies.

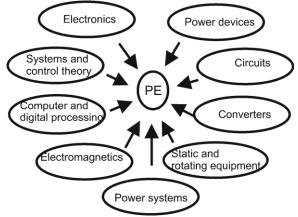

Through the use of this switching technology power electronics systems can operate in the range from few watts up to GW, with frequency range from some 100 Hz up to some 100 kHz, depending on the power handled [1]. The advent of microelectronics and computer control made it possible to apply modern control theory to PE and at same the time made possible very complex circuit functions. Therefore, the area of PE, became interdisciplinary, as indicated in Fig. 2.2. At the high power level, PE deals with static and rotating equipment for generation, transmission, and distribution handling large amount of power. For consumer electronic applications power converters and circuits are important for information processing, employing analog and digital circuits, or microprocessors including microcontrollers, digital signal processors (DSP), and field programmable gate arrays (FPGA). In the area of control, PE deals with stability and response characteristics in systems with feedback loops, based on classical or modern control. With the development of very large system integration (VLSI), ultra large system integration (ULSI), and other sophisticated computer-assisted designs; advanced control systems could be used to develop new power electronic topologies.

The development of devices and equipment able to individually or in combination convert efficiently electric energy from AC to DC, DC to DC, DC to AC, and AC to AC together with the changes that occurred in electrical power engineering has resulted in wide spread of PE in a large spectrum of applications.

Fig. 2.2 Power electronics and related topics

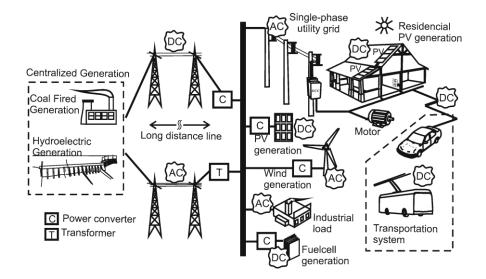

Fig. 2.3 Power electronics and electrical energy generation transmission, storage, and distribution

Figure 2.3 shows how electrical energy generation is distributed for the end-user, showing transmission, distribution, storage, renewable energy sources and users. In fact, nowadays PE is a key technology for all those sub-systems, and has spread in many applications, examples including:

- Residential: heaters, home appliances, electronic lighting, equipment sources;

- Commercial: heaters, fans, elevators Uninterruptible Power Supply (UPS), AC and DC breakers, battery chargers;

- Industrial: pumps, blowers, robots, inductive heaters, welding, machine drive, portable sources;

- Transportation: electrical and hybrid vehicles, battery chargers, railroad electric system;

- Utility systems: high voltage direct current, generators, reactive compensators, interface for photovoltaic, wind, fuel cells systems, Flexible AC Transmission System (FACTS) equipment;

- Aerospace: sources for spacecrafts, satellites, planes;

- · Communication: sources, RF amplifiers, audio-amplifiers.

Power electronics will continue to be an enabling technology to address our future electricity needs. It is expected that new power devices for higher power, higher frequency, and lower losses will continue to be invented. Global energy concerns will provoke a large interest in the increase of the conversion efficiency and more application of PE in power quality, distributed generation, energy conservation, and smart grids. The integration of power and control circuitry into functional modules will result in systems solutions that are highly integrated into packaged products that will be both more reliable and affordable.

## 2.1.2 **Power Semiconductor Devices**

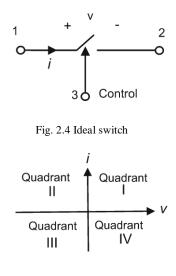

Electronic switches capable of handling high voltage and current operations at high frequency (HF) are the most important devices needed in the design of energy conversion systems that use PE. For the purposes of this discussion we will define the concept of an ideal switch. An ideal power electronic switch can be represented as a three terminals device as shown in Fig. 2.4. The input, the output, and a control terminal that imposes ON/OFF conditions on the switch. A switch is considered "ideal" when it is open, it has zero-current through it and can handle infinite voltage. When the switch is closed it has zero-voltage across it and can carry infinite current. Also, an ideal switch changes condition instantly, which means that it takes zero-time to switch from ON-to-OFF or OFF-to-ON. Additional characteristics of an ideal switch include that it exhibits zero-power dissipation, carries bidirectional current, and can support bidirectional voltage. If we plot the switch current (i) with respect to its voltage (v) we define four quadrants that are often referred to as the v-i plane and are shown in Fig. 2.5. By definition, an ideal switch can operate in all four quadrants.

Practical or real switches do have their limitations in all of the characteristics explained in an ideal switch. For example, when a switch is on, it has some voltage across it, known as the on-voltage and it carries a finite current. During the off stage, it may carry a small current known as the leakage current while supporting a finite voltage. The switching from ON-to-OFF and vice versa does not happen instantaneously. Of course, all actual switching devices take times to switch and we define these characteristics as the delay, rise, storage, and fall times. As a consequence of the above two non-ideal cases, there is voltage and current across the switch at all times, which will result in two types of losses. The first loss occurs during the on and off-states and is defined as the "conduction loss". The second loss is defined as the "switching loss" which occurs just as the switch changes state as either opening or closing. The switch losses result in raising the overall

Fig. 2.5 *4-quadrant* switch *v-i* characteristics

switch temperature. Further, the ON/OFF-state of the power switch must be controlled though an external signal.

## 2.1.3 Classifications of Power Switches

The concept of the ideal switch is important when evaluating circuit topologies. Assumptions of zero-voltage drop, zeroleakage current, and instantaneous transitions make it easier to simulate and model the behavior of various electrical designs. Using the characteristics of an ideal switch, there are three classes of power switches:

- 1. *Uncontrolled switch*: The switch has no control terminal. The state of the switch is determined by the external voltage or current conditions of the circuit in which the switch is connected. A diode is an example of such switch.

- 2. *Semi-controlled switch*: In this case the circuit designer has limited control over the switch. For example, the switch can be turned-on from the control terminal. However, once ON, it cannot be turned-off from the control signal. The switch can be switched off by the operation of the circuit or by an auxiliary circuit that is added to force the switch to turn-off. A thyristor or a SCR is an example of this switch type.

- 3. *Fully controlled switch*: The switch can be turned-on and off via the control terminal. Examples of this switch are the BJT, the MOSFET, the IGBT, the GTO thyristor, and the MOS-controlled thyristor (MCT).

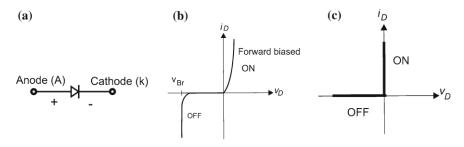

### 2.1.4 Uncontrolled Switches

A diode, also known as rectifier, is an *uncontrolled switch*. It is a two terminal device with a symbol depicted in Fig. 2.6a. The terminals are known as Anode (*A*) and cathode (*K*). In the ideal case, the diode current ( $i_d$ ) is unidirectional and current can only flow from the anode to the cathode. The diode voltage ( $v_d$ ) is measured as being positive from the anode to the cathode.

The *v*-*i* characteristics for a real (non-ideal) diode are shown in Fig. 2.6b. In quadrant I, the diode is in the ON-state, and is known as the forward-biased region. When it is ON the diode carries a positive current while supporting a small voltage. The diode current varies exponentially with the diode voltage. The diode is reversed-biased in quadrant III, which is the OFF-state. When it is OFF, the diode supports a negative voltage and carries a negligible current (leakage current). When the negative voltage exceeds a certain limit, known as the breakdown voltage, the leakage current increases rapidly while the voltage remains at the breaking value, which potentially damages the device. Therefore, operation that exceeds the breakdown voltage must be avoided.

The ideal diode characteristics are shown in Fig. 2.6c. During the ON-state, the diode has zero-voltage across it and carries a positive current. During the OFF- state, the diode carries zero-current and supports a negative voltage.

Fig. 2.6 Diode: a symbol, b i-v characteristics, and c idealized characteristics

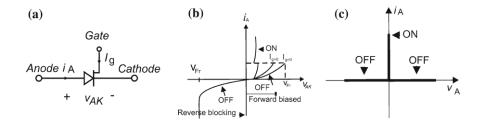

### 2.1.5 Semi-controlled Switches

The thyristor or SCR is a power semiconductor switch whose turn-on can be activated from the control terminal Gate but once it turns ON, the control terminal becomes ineffective and the thyristor behaves similar to a diode. Therefore, the thyristor is considered a *semi-controlled switch*. The name, controlled rectifier, is an indication that a thyristor is a device that can be considered as a diode whose turn-on can be commanded externally. Figure 2.7a shows the circuit symbol for a thyristor. Although there are similarities between the diode and the thyristor circuit symbols, their operation is very different. The thyristor current,  $I_A$ , flows from the anode (A) to the cathode (K) and the voltage  $V_{Ak}$ , across the thyristor is positive when the anode is at higher voltage than the cathode. Figure 2.7b shows the *v*-*i* characteristics of a real or non-ideal thyristor. In quadrant I, in the absence of a gate current, the device is OFF in the forward blocking region and supports a positive voltage. If a gate current is applied, the device switches to the on-state region and the device has a v-i characteristic similar to that of a diode. In quadrant III, the device is OFF, and the region is known as the reverse blocking region. Again, the characteristics are similar to those of a diode. Comparing the switching characteristics of a diode and a thyristor, it appears that when the thyristor is OFF, it can block large positive or negative voltage, which is a fundamental feature that is important in circuit applications, such as AC/AC converters. This can be clearly seen in the ideal characteristics of the thyristor as shown in Fig. 2.7c. In the ON- state, the thyristor has zero-voltage across it and carries a positive current. In the OFF-state, the thyristor can support a positive voltage in the forward blocking region or a negative voltage, similar to a diode, in the reverse blocking region. Therefore, the thyristor can be considered to carry a unidirectional current and supports a bidirectional voltage.

The triac, shown in Fig. 2.8a, is also a semi-controlled switch. A triac can be modeled as two thyristors connected backto-back as shown in Fig. 2.8b. Triacs are considered as bidirectional voltage and bidirectional current devices, as shown by the *v*-*i* characteristics in Fig. 2.8c. The ideal characteristics are in Fig. 2.8d. As a low-cost bidirectional switch, the triac is the primary switch that is used for low power electronic commercial circuits such as light dimmers and control circuits for single-phase motors used in home appliances.

Fig. 2.7 Thyristor: a symbol, b i-v characteristics, and c idealized characteristics

Fig. 2.8 The triac: a symbol, b two-thyristor-representation, c i-v characteristics, and d idealized characteristics

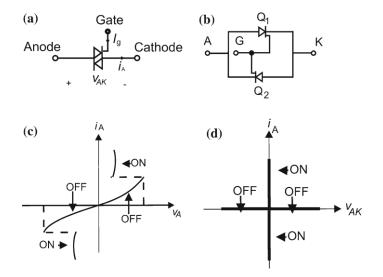

#### 2.1.5.1 Fully Controlled Switches

In a fully controlled switch the ON- and OFF-states can be activated externally through a control terminal. A number of power switches fall into the category of controlled switches; some of them are transistor-based devices and others are thyristor-based devices. A brief description of each device is given in the following sections:

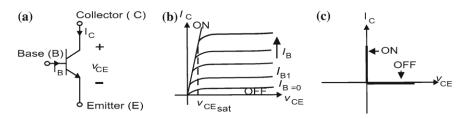

#### 2.1.5.1.1 The Bipolar Junction Transistor

Figure 2.9a shows the circuit symbol for an npn-type BJT. The base (B) is the control terminal, where the power terminals are the collector (C) and the emitter (E). The v-i characteristics of the device are shown in Fig. 2.9b. The device

Fig. 2.9 The BJT: a symbol, b i-v characteristics, and c idealized characteristics

operates in quadrant I and is characterized by the plot of the collector current versus the collector to emitter voltage. The device has three regions two of them where the device operates as a switch and the third is where the device operates as a linear amplifier. The device is OFF in the region below  $i_B 0$  and is ON in the region where  $v_{CE}$  is less than  $v_{CE(Sat)}$ . Neglecting the middle region, the idealized device characteristics as a switch are shown in Fig. 2.9c. During the ON-

state the device carries a collector current IC > 0 with  $V_{CE} = 0$ . In the OFF-state, the device supports positive  $V_{CE} > 0$  with IC = 0. Therefore, the BJT is unidirectional current and voltage device. The BJT has historical importance, but today most of its function are covered by devices like the IGBT.

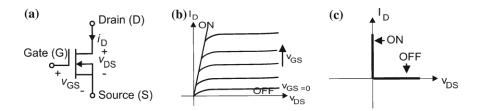

#### 2.1.5.1.2 The Metal Oxide Semiconductor Field Effect Transistor

Figure 2.10a shows the circuit symbol for an n-channel, enhancement mode MOSFET. Similar to the BJT, it has a control terminal known as the gate (*G*) and the power terminals are the drain (*D*) and source (*S*). The device is controlled by supplying a voltage ( $v_{GS}$ ) between the gate and the source. This makes it a voltage- controlled device compared to the BJT, which is a current-controlled device. The real *v*-*i* characteristics of device are shown in Fig. 2.10b. Similar to the BJT, the MOSFET operates within three operating regions. Two of the regions are used when the device is operated as a switch, and the third is when the device is used as an amplifier. To maintain the MOSFET in the off-state,  $v_{GS}$  must be less than a threshold voltage known as  $v_T$ , which is the region below the line marked OFF. And when the device is ON it act as resistance determined by the slope of the line marked ON. The idealized characteristics of a MOSFET switch are shown in Fig. 2.10c. When the device is ON, it has zero  $v_{DS}$  and carriers a current  $I_D > 0$  and when the device is OFF it supports a positive  $v_{DS}$  and has zero drain current ( $I_D = 0$ ).

Fig. 2.10 The MOSFET: a symbol, b i-v characteristics, and c idealized characteristics

Fig. 2.11 The IGBT: a symbol, b i-v characteristics, and c idealized characteristics

Three other MOSFET configurations include: n-channel depletion mode and p-channel enhancement and depletion modes.

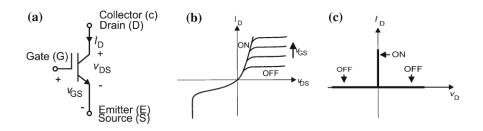

#### 2.1.5.1.3 The Insulated Gate Bipolar Transistor (IGBT)

The IGBT is a hybrid or also known as double mechanism device. Its control port resembles a MOSFET and its output or power port resembles a BJT. Therefore, an IGBT combines the fast switching of a MOSFET and the low power conduction loss of a BJT. Figure 2.11a shows a circuit symbol that is used for an IGBT, which is slightly different from the MOSFET with similar terminal labels. The control terminal is labeled as gate (G) and the power terminals are labeled as collector (C) and emitter (E). The *i*-v characteristics of a real IGBT are shown in Fig. 2.11b, which shows that the device operates in quadrants I and III. The ideal characteristics of the device are shown in Fig. 2.11c. The device can block bidirectional voltage and conduct unidirectional current. An IGBT can change to the ON-state very fast but is slower than a MOSFET device. Discharging the gate capacitance completes control of the IGBT to the OFF-state. IGBT's are typically used for high power switching applications such as motor controls and for medium power PV and wind PE.

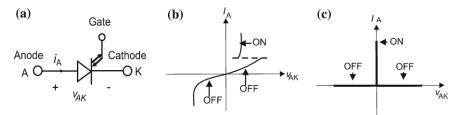

#### 2.1.5.1.4 The Gate Turn-Off Thyristor

The GTO thyristor is a device that operates similar to a normal thyristor except the device physics, design and manufacturing features allow it to be turned-off by a negative gate current which is accomplished through the use of a bipolar transistor. The circuit symbol for a GTO is shown in Fig. 2.12a. The v-i characteristics and the ideal switch characteristics are shown in Fig. 2.12 b, c. Although the device has been in existence since the late 1960s, and it has been successfully used in high power drives, IGBTs have reached price and rating party and are expected to replace GTO's in new power electronic designs.

Fig. 2.12 The GTO: a symbol, b i-v characteristics, and c idealized characteristics

Fig. 2.13 The MCT: a symbol, b *i-v* characteristics, and c idealized characteristics

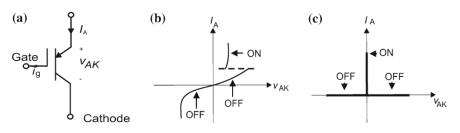

#### 2.1.5.1.5 The MOS-Controlled Thyristor

Similar to the IGBT, the MCT is a hybrid or double mechanism device that was designed to have a control port of a MOSFET and a power port of a thyristor. The circuit symbol for the device is shown in Fig. 2.13a. The real device characteristics and the idealized characteristics are shown in Fig. 2.13b, c. The characteristics are similar to the GTO, except that the gate drive circuitry for the MCT is less complicated than the design for a GTO as the control circuit of the MCT uses a MOSFET instead of a transistor. As a result, the MCT was supposed to have higher switching frequency. Although the MCT was invented at the same time period of the IGBT it never became fully commercially available and at the time of writing this book it is unknown the future market plans.

## 2.1.6 Power Electronic Converter Topologies

Power electronic converters are switch-mode circuits that process power between two electrical systems using power semiconductor switches. The electrical systems can be either DC or AC. Therefore, there are four possible types of converters; namely DC/DC, DC/AC, AC/DC, and AC/AC. The four converter types are described below:

- DC/DC Converter: is also known as "Switching Regulator". The circuit will change the level voltage available from a

DC source such as a battery, solar cell, or a fuel cell to another DC level, either to supply a DC load or to be used as an

intermediate voltage for an adjacent power electronic conversion such as a DC/AC converter. DC/DC converters

coupled together with AC/DC converters enable the use of high voltage DC (HVDC) transmission which has been

adopted in transmission lines throughout the world.

- 2. DC/AC Converter: Also described as "Inverter" is a circuit that converts a DC source into a sinusoidal AC voltage to supply AC loads, control AC motors, or even connect DC devices that are connected to the grid. Similar to a DC/DC converter, the input to an inverter can be a stiff source such as battery, solar cell, or fuel cell or can be from an intermediate DC link that can be supplied from an AC source.

- 3. AC/DC Converter: This type of converter is also known as "Rectifier". Usually the AC input to the circuit is a sinusoidal voltage source that operates at 120 V, 60 Hz or a 230 V, 50 Hz, which are used for power distribution applications. The AC voltage is rectified into a unidirectional DC voltage, which can be used directly to supply power to a DC resistive load or control a DC motor. In some applications the DC voltage is subjected to further conversion using a DC/DC or DC/AC converter. A rectifier is typically used as a front-end circuit in many power system applications. If not applied correctly, rectifiers can cause harmonics and low power factor when they are connected to the power grid.

- 4. AC/AC Converter: This circuit is more complicated than the previous converters because AC conversion requires change of voltage, frequency, and bipolar voltage blocking capabilities, which usually requires complex device topologies. Converters that have the same fundamental input and output frequencies are called "AC controllers". The conversion is from a fixed voltage fixed frequency (FVFF) to a variable voltage fixed frequency (VVFF). Applications include: light dimmers and control of single-phase AC motors that are typically used in home appliances. When both voltage and frequency are changed, the circuits are called "Cyclo-converters", which convert a FVFF to variable voltage variable frequency (VVVF) and when fully controlled switches are used, this class of circuit is called "Matrix Converter". Another way of achieving AC/AC conversion is by using AC/DC and DC/AC through an intermediate DC link. This type of combined converter approach can be complex as the correct control approach must be implemented including simultaneous regulation of the DC link, injection of power with a prescribed power factor and bidirectional control of energy flow.

### 2.1.6.1 DC/DC Converters

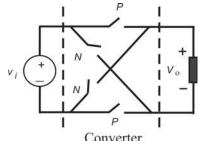

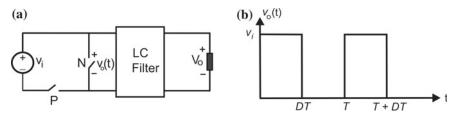

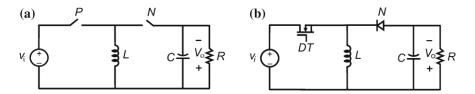

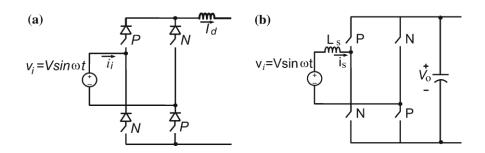

A generalized circuit for a DC/DC converter is depicted in Fig. 2.14 where all possible switches connecting the input to the output are represented. If one P-switch and one N-switch are used, the resulting circuit is shown in Fig. 2.15a. The switches are controlled ON and OFF within a specified period T. The output

Converter Fig. 2.14 Generalized circuit for DC/DC converter circuits

Fig. 2.15 Non-isolated down (buck) DC/DC converter: a circuit and b waveforms

voltage is equal to the input voltage when the P-switch is ON, and is equal to zero when the N-switch is ON. The ratio of the ON-time of switch P switch to the period *T* is defined as the duty ratio or duty-cycle (*D*). The waveform of the output voltage  $v_o(t)$  is shown in Fig. 2.15b. Since  $v_o(t)$  is a pulsating waveform, an LC circuit is used to filter the voltage to a DC. In this case the average  $V_o$  or DC component of the output voltage is given by Eq. (2.1),

$$V_{\text{avg}} = \frac{1}{T} \int_{0}^{DT} V_i = DV_i \tag{2.1}$$

Since D < 1, the DC output voltage of this converter is always less than the input voltage.

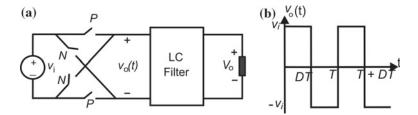

When all the generalized converter switches are used, the resulting circuit is shown in Fig. 2.16. When the P-switches are ON, the output voltage is equal to the input voltage and when the N-switches are ON, the output voltage is equal to the negative of the input voltage. The resulting waveform is shown in Fig. 2.16b. The DC component or the average of the output voltage is given by:

$$V_{\text{avg}} = \frac{1}{T} \left[ \int_{0}^{DT} V_i dt + \int_{DT}^{T} -V_i dt \right] = (2D - 1)V_i$$

(2.2)

Equation (2.2) indicates that the output voltage is less than the input voltage with a changed polarity. For duty-cycle D>0.5 the output has a positive value and for

Fig. 2.16 Full-bridge non-isolated down (buck) DC/DC converter: a circuit, and b waveforms

duty-cycle D < 0.5 the output has a negative value. The LC circuit in the design is used to filter the harmonic components of the output voltage so that the load receives a DC voltage with negligible ripple. Both voltages given by Eqn. (2.1) and (2.2) indicate that output has a lower DC value than the input voltage. Therefore, the converters are referred to as step down or buck converters.

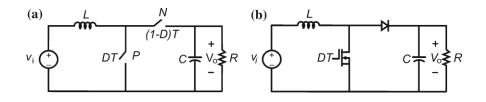

Two other basic DC/DC converters include the boost and buck/boost converters. A boost converter can be defined as when the DC output voltage is higher than the input voltage. This design is also referred to as a step-up converter and a typical design is shown in Fig. 2.17. In this circuit, the switches are inserted between the inductor and the capacitor. If the converter is lossless, the ratio of the output DC voltage to the input DC voltage is given by Eq. (2.3). Since D is less than one, the output voltage is always higher than the input voltage.

$$V_{\rm avg} = \frac{V_i}{D} \tag{2.3}$$

A buck/boost or step-up/down converter is shown in Fig. 2.18. This converter is capable of providing a DC output voltage that can be lower or higher than the input DC voltage. The input/output conversion ratio is given by Eq. (2.4).

$$\frac{V_o}{V_i} = \frac{D}{1 - D} \tag{2.4}$$

When the *D*, is less than 0.5 the converter operates as a buck or step-down converter and when D>0.5 the converter operates as step-up or boost converter. For all basic DC/DC converters discussed so far. The switch is implemented by a controlled switch (transistor) and an uncontrolled switch (diode). When the transistor and the diode are alternately switched, the mode of operation is referred to as

Fig. 2.17 Non-isolated boost (up) DC/DC converter: a circuit, and b switch implementation

Fig. 2.18 The buck-boost (up/down) non-isolated DC/DC converter: a circuit, and b switch implementation

continuous conduction mode (CCM). In this mode, the inductor current never reaches zero and the output voltage-to-input voltage conversion ratio becomes only a function of the duty ratio. If the inductor current is zero for a portion of the cycle, the mode of operation is known as the discontinuous conduction mode (DCM). The converter will operate at DCM when circuit parameters such as inductance is decreased or when the switching frequency is decreased or when the load resistance is increased. Therefore, the output-input conversion ratio is a function of the duty ratio and several of those parameters.

The three basic DC/DC converters discussed so far are referred to as non- isolated converter topologies. Another class of converter is called isolated converters whose utilize a transformer that is placed directly between the input and output and usually have more switches and more filter components than non- isolated converters. Isolated DC/DC converters can be designed to provide multiple output DC voltages. There are some non-isolated converters that use higher order filter such as the Cuk converter, the SEPIC converter and the ZETA converter. For complete types and analysis of non-isolated and isolated converters, please refer to Chaps. 6 and 7 in [1], Chaps. 7 and 10 in [2], Chaps. 4 and 5 in [3] and Chaps. 6 and 7 in [4].

### **2.1.6.2 DC/AC** Converters (Inverters)

Inverters are power electronic circuits that transform DC voltage from sources such as batteries, solar cells or fuel cells (or the output of a rectifier) into AC, for powering motor drives, providing stand-alone AC output, or interconnecting to the AC grid. Inverters can be usually classified according to their AC output as single- phase or three-phase and also as half-and full-bridge converters.

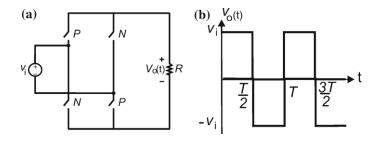

#### 2.1.6.2.1 Single-Phase Inverters

Figure 2.19a represents a generalized DC/AC single-phase inverter. Figure 2.19b shows the resulting AC waveform when the P- and N-switches operate at a D = 0.5. The graph shows that the AC waveform is a square wave D = 0.5. Further, the voltage has no DC component which can also be shown by substituting D = 0.5 in Eq. (2.2). A half-bridge converter can be obtained using two DC sources of equal voltages, one P-Switch and one N-switch as shown in Fig. 2.20. The output is a square wave with a period *T*, which corresponds to an AC fundamental frequency as:

$$f = \frac{1}{T}$$

Hz or  $\omega = 2\pi f = \frac{2\pi}{T}$  rad/s (2.5)

The amplitude of the n<sup>th</sup> sinusoidal voltage can be evaluated by Fourier series of the square wave  $v_o(t)$  as

$$v_{on} = \frac{2}{T} \int_{0}^{T} v_o(t) \sin n\omega_a t dt = \frac{4V_i}{n\pi} \quad \to n = 1, 3, 5, \dots \text{odd}$$

(2.6)

A filter such as a resonant LC-type circuit can be designed to filter most of the harmonics present in the square wave and prevent them from appearing across load. The fundamental voltage available from the square voltage has a fixed amplitude (as obtained by substituting n = 1 in Eq. (2.6). Half-bridge converters have

Fig. 2.19 Full bridge (FB) DC/AC converter: a circuit, and b waveforms

Fig. 2.20 Half-bridge (HB) DC/AC converter (inverter): a circuit, and b waveforms

Fig. 2.21 Full-bridge (FB) DC/AC converter with variable AC voltage: a circuit, and b waveforms

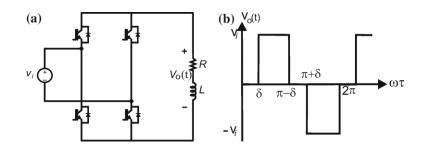

fixed amplitude, but the full-bridge ones (as shown in Fig. 2.21) do not have this limitation.

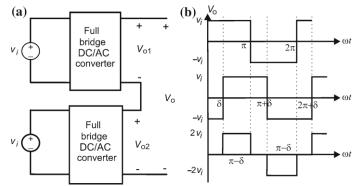

Rather than having the voltage  $v_o$  to have only two levels  $V_{dc}$  or  $-V_{dc}$ , a third level can be used where the voltage  $v_o$  is zero and is called a three-level inverter. The resultant voltage waveform is shown in Fig. 2.21b. The angle *d* is a phase-shift between the two transistor legs and is used to control the amplitude of the sinusoidal n<sup>th</sup> voltage, as demonstrated by Fourier series of  $v_o$ .

$$v_{on} = \frac{4}{T} \int_{0}^{T} v_o(t) \sin n\omega_a t \ d(\omega t) = \frac{4V_i}{n\pi} \cos n\delta \quad \rightarrow n = 1, 3, 5, \dots \text{odd}$$

(2.7)

It can be seen that by varying  $\delta$  from zero to  $\pi$ , the output voltage can be varied from a fixed voltage at  $\delta = 0$  to zero-voltage at  $\delta = \pi$ . This  $\delta$ -control introduces a variable AC voltage and also can eliminate one harmonic voltage as long as Eq. (2.8) is observed.

$$\cos n\delta = 0$$

, which means  $n\delta = \frac{\pi}{2}$  (2.8)

For example, if the third harmonic voltage is chosen to be eliminated then d = p/6. This method of harmonic elimination is known as active filtering contrasted to passive filtering that requires actual filter components. Another method of active filtering is known as harmonic cancellation where harmonics are eliminated by processing waveforms. Figure 2.22shows two converters where both converters are switched at a steady square wave voltage. The output waveforms  $v_{o1}(t)$  and  $v_{o2}(t)$ of the two converters are shown in Fig. 2.22b. It can be seen that each of the two converters produces a fixed two-level square wave voltage. By shifting the control of one converter by angle d, and adding the two voltage the resulting output voltage  $v_o(t)$  is a variable three-level inverter, similar to the one shown in Fig. 2.21. Each of the inverters output contains a third harmonic. However, by adding the two inverters output, the resulting voltage will not have third harmonic voltage if d is chosen to be 30°. Numerous control methods for

Fig. 2.22 Active filtering using harmonic elimination: a circuit, and b waveforms

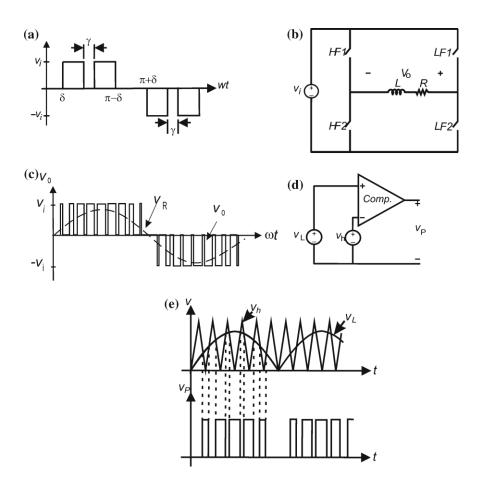

Fig. 2.23 Pulse-width modulation (*PWM*) switching technique: a multiple harmonic elimination, b PWM circuit, c PWM AC output, d PWM generation, and e PWM signal

harmonic elimination and harmonic cancellation have been proposed in the literature. These methods have resulted in two major breakthroughs in active-wave shaping or active filters; namely the method of pulse-width modulation (PWM) and the method of multilevel inverters, which will briefly be discussed later.

The *d*-control method imposes a zero-voltage on the output voltage and if more of the zero-voltage segments are introduced, the harmonic content of the AC voltage can be reduced. For example, if two segments are introduced as shown in Fig. 2.23a, with  $d = 30^{\circ}$  and  $c = 12^{\circ}$ , then it can be shown that both the third and fifth harmonic voltages can be eliminated [1]. Also, if these zero-voltage regions can be introduced at high frequency (HF) with a variable width that is sinusoidally distributed at the fundamental frequency of the AC voltage, the resulting AC voltage will contain only the fundamental AC component and components at the HF of the *d*-control.

Figure 2.23b shows a converter similar to the full-bridge topology where the switches are controlled at either HF or a low frequency (LF). The HF switches operate at a frequency known as the carrier frequency, which is much higher than the fundamental AC frequency. The LF switches are operated at the fundamental frequency, referred to as the modulating frequency. During the positive half cycle of the LF switches, the HF switches are alternating at the constant carrier frequency with different on-times, i.e., a variable duty ratio. The duty ratio can be obtained by comparing a triangular wave signal at the carrier frequency with a sine wave signal at the modulating frequency, as shown in Fig. 2.23c. The resulting output waveform has a constant frequency with a modulated pulse width, so this technique is called PWM. Although no specific harmonic elimination (or cancellation) is introduced, the unwanted frequencies are pushed to higher frequency decades above the fundamental AC frequency and, as a result, the amount of passive filtering that is required can be minimized.

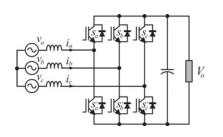

### 2.1.6.3 Three-Phase Inverters

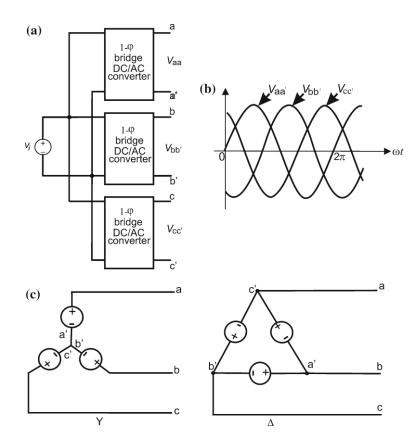

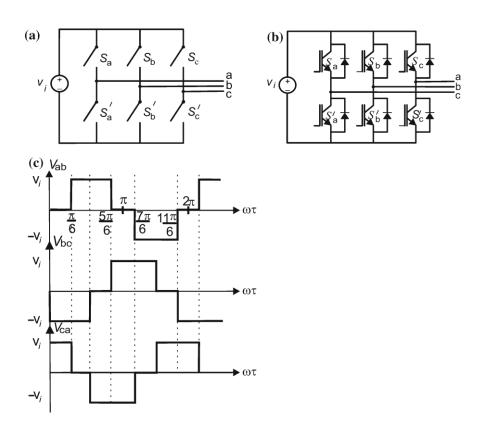

Three-phase DC/AC converters can be constructed using single-phase DC/AC converters (one leg branch). Three single-phase inverters can be connected to a common DC source, as shown in Fig. 2.24a. Their switch controls are shifted by 120°, with resulting output voltages shown in Fig. 2.24b. The three outputs can be connected in *Y* or D as shown in Fig. 2.24c. It can be shown that the number of switches for the three independent single-phase bridge converters can be reduced to six switches rather than twelve and this design is shown in Fig. 2.25a and b. This converter design is the standard circuit topology that is used for conversion of DC to three-phase AC. The AC output depends on the control of the six switches. For example, if the switches are controlled with a phase-shift command of 60°, the resulting waveforms are shown in Fig. 2.25c.

When a DC voltage is the input to a converter, the design is defined as voltage- fed inverter (VFI) or voltage source inverter (VSI). When a DC current is the input to a converter it is defined as either a current-fed inverter (CFI) or current source inverter (CSI) as depicted in Fig. 2.26. The CSI operation constraints are: (1) there must always exist a current path for the current source; (2) the output phases cannot be short-circuited. The DC current is unidirectional, and only two switches conduct at same time providing the path for current circulation. The switch types for this design must be fully controlled in current and bidirectional in voltage. Switches that meet this requirement include: SCR, GTO, and the recently introduced IGBT.

Fig. 2.24 Three-phase AC/DC converter: a circuit, b waveforms, and c connections

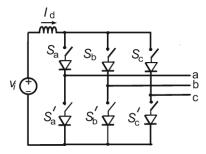

#### 2.1.6.3.1 AC/DC Converters (Rectifiers)

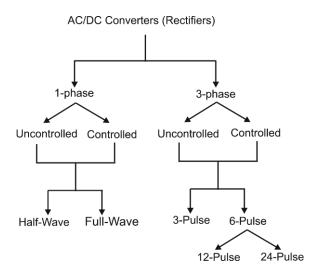

AC/DC converters are called rectifiers circuits, which can be broadly classified based on the type of AC source and the type of semiconductor switch is used as shown in Fig. 2.27. Rectifiers are usually used in either single-phase orthree-phase applications, but multi-phase topologies are possible for high power applications. Switches that are used in rectifier's designs can be either uncontrolled (diode) or controlled devices (thyristor). Single-phase rectifiers can be classified as

either half-wave or full-wave circuits. Three-phase rectifiers are classified based on the number of pulses of the rectified output voltage, i.e., 3-pulse rectifiers, 6-pulse, 12- pulse, or more generally 3 9  $2^n$ -pulse (where n = 0, 1, 2, 3...). The number of pulses is the ratio of the fundamental frequency of the rectifier output to the frequency of the AC input.

Fig. 2.25 Six-step inverter and waveforms: a circuit, b switch implementation, and c waveforms

Fig. 2.26 Current source inverter (CSI)

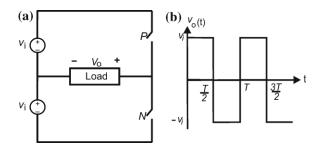

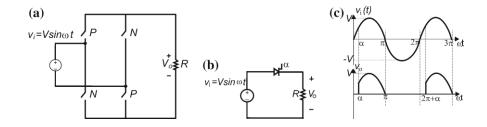

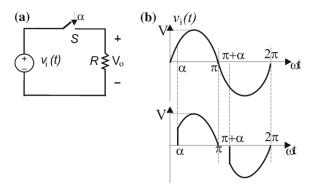

#### 2.1.6.3.1 Single-Phase Rectifiers

A general circuit for a single-phase rectifier is illustrated in Fig. 2.28. Note that this design is the same as the generalized DC/DC converter shown in Fig. 2.14 except that a sinusoidal voltage replaces the input DC source. The basic single- phase rectifier circuits are completed by setting the P- and N-switches to be either permanently closed or open. For example, if all the N-switches are permanently open and the bottom P-switch is permanently closed, the resulting circuit is a half-wave rectifier circuit. If the remaining P-switch is a thyristor, then the resulting circuit is a controlled half-wave rectifier. A depiction of this topology is shown in Fig. 2.28b and resulting waveforms are shown in Fig. 2.28c. In such case, the angle *a* is the thyristor turn-on delay angle, which is measured starting at the zero- crossings of the input voltage source.

Fig. 2.27 Classifications of rectifier circuits

Fig. 2.28 a General 1-phase rectifier circuit, b 1-phase controlled rectifier, and c Input and output voltage waveforms

The output waveform has an average value (the required DC component), which can be calculated using Eq. (2.9) as,

$$V_{\text{avg}} = \frac{1}{T} \int_{0}^{T} v(t) \, \mathrm{d}t = \frac{1}{2\pi} \int_{\alpha}^{\pi} V \sin \omega t \, \mathrm{d}(\omega t) = \frac{V}{2\pi} (1 + \cos \alpha) \tag{2.9}$$

Equation (2.9) shows that the value of the DC voltage can be varied as a is changed. A half-wave uncontrolled rectifier is possible when the remaining P- switch is implemented through the use of a diode; this circuit is the same as in

Fig. 2.29 Examples of uncontrolled rectifiers: a full-bridge (FB), and b waveforms

Fig. 2.28b except the thyristor is replaced by a diode. Since the diode is an uncontrolled switch, a is set to zero and the diode will turn-on at the zero-crossings of the supply voltage. When a = 0 is substituted into Eq. (2.9) then average voltage is given as:

Equation (2.10) shows that the DC voltage is fixed and cannot be changed and as a result this type of rectifier is defined as uncontrolled.

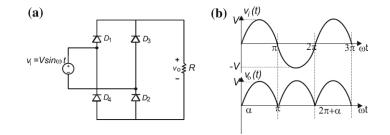

If all the switches of Fig. 2.28a are used, then the resulting circuit is a full-wave rectifier as shown in Fig. 2.29a. When all the switches are diodes, the resulting waveform is illustrated in Fig. 2.29b. The DC voltage in a full-wave rectifier design will be double the one from the half-wave rectifier.

There are circuit topologies, such as one-quadrant, two-quadrant, and four- quadrant, for half- or full-wave types. Some of them are uncontrolled, and others are fully controlled depending on the combination of diodes and thyristors, which are usually classified as semi-controlled or hybrid rectifiers. Some rectifiers use transformers for isolation for further rectification capability [1, 2].

$$V_{\text{avg}} = \frac{1}{2\pi} \int_{0}^{\pi} V \sin \omega t \, \mathrm{d}(\omega t) = \frac{V}{\pi}$$

(2.10)

#### 2.1.6.3.4 Three-Phase (3-U) Rectifiers

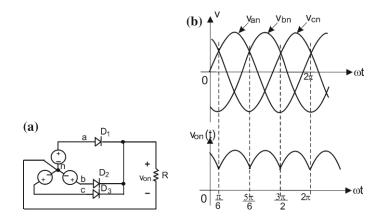

As mentioned in the classification of three-phase rectifiers, the output is defined in terms of the number of pulses per one cycle of the input voltage. The 3-pulse rectifier is a basic three-phase rectifier circuit (connected to a three-phase system), and can be used as building block for most of other three-phase rectifiers. Each of the three-phase input voltages can be determined using Eq. (2.11). The operation of a three-phase 3-pulse rectifier is shown in Fig. 2.30a, b.

$$v_a = V \sin \omega t V$$

$$v_b = V \sin(\omega t - 120^\circ) V$$

$$v_b = V \sin(\omega t + 120^\circ) V$$

(2.11)

Fig. 2.30 three-phase, 3-pulse rectifier circuit: a circuit and b waveforms

In this case the switches are implemented with diodes (uncontrolled rectifier). A diode will turn-on when its voltage is higher than the other two diodes, i.e., the diode connected to the highest of the three voltages will conduct. The resulting output is shown in Fig. 2.30b; notice that the diode conduction starts and ends when two of the three voltages are equal. Also, each diode conducts for an angle of 120°, and the output voltage has 3 pulses, during one cycle of the input. Therefore, the fundamental frequency of the output voltage is three times the frequency of the input voltage. The DC component of the output of each of them can be calculated by the average over its period as:

$$V_{\text{avg}} = \frac{1}{(2\pi/3)} \int_{\frac{\pi}{6}}^{\frac{3\pi}{6}} V \sin \omega t \, d(\omega t) = \frac{3\sqrt{3}V}{2\pi}$$

(2.12)

The DC voltage, given by Eq. (2.12), is higher than the output voltage of a single-phase full-wave rectifier. Of course, the drawback is the need of a three- phase source, which is most common for industrial applications.

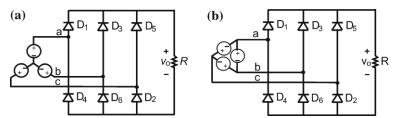

Fig. 2.31 6-pulse rectifier circuits: a Y-connected source, and b D-connected source

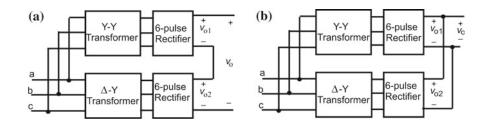

Fig. 2.32 12-pulse rectifier circuits: a high voltage 12-pulse rectifier, and b high current 12- pulse rectifier

If two 3-pulse rectifiers are connected the resulting topology is shown in Fig. 2.31. This circuit is known as a 6-pulse rectifier, and it is the building block for all high power multiple-pulse rectifier circuits.

Two 6-pulse rectifier circuits can be connected through the use of Y-Y and D-Y transformers for building 12-pulse rectifiers. If the two rectifiers are connected in series, the resulting circuit is shown in Fig. 2.32a and is suitable for high voltage, whereas the converter is connected in parallel as shown in Fig. 2.32b, the circuit is suitable for high current.

#### 2.1.6.3.5 Controlled Rectifiers

When diodes are replaced by thyristors, the three-phase rectifier circuit becomes a controlled one, and the delay angle *a* (measured relative to the time where the diodes start to conduct) will control the output voltage. Similar to single-phase rectifiers, there are combinations of switches and transformers that result in higher pulse three-phase rectifiers. For complete understanding on the types and analyses of single-phase and three-phase rectifiers, the reader is referred to Chaps. 4 and 5 of reference [1], Chap. 7 of reference [2], Chaps. 5 and 6 of reference [3], and Chaps. 4 and 5 of reference [4].

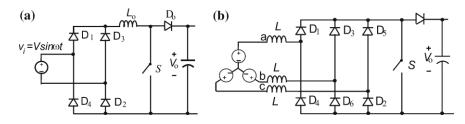

Fig. 2.33 PWM rectifier: a single-phase, and b three-phase

Fig. 2.34 Single-phase PWM rectifiers

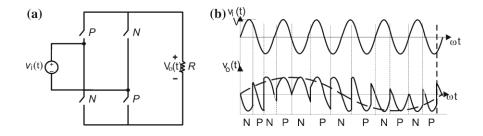

#### 2.1.6.3.6 PWM Rectifiers

PWM rectifiers can be implemented as unidirectional or bidirectional as regarding their power flow capabilities. A basic unidirectional boost version consists of an uncontrolled diode bridge followed by a boost converter as shown in Fig. 2.33a. When the switch is ON the inductor current increases proportionally to the input voltage (which is sinusoidal). When the switch is OFF, the inductor current decreases, and its energy is transferred to the capacitor, repeating such cycle with variable input voltage. The boost converter regulates the capacitor voltage, and also impresses a sinusoidal input current profile, which improves the input power factor. Since this converter can operate in either Continuous Conduction Mode (CCM) or in Discontinuous Conduction Mode (DCM), its control should be designed to be stable and work in both conditions. A three-phase version of the unidirectional boost rectifier is shown in Fig. 2.33b, but the inductors are connected at the AC side.

In order to implement a bidirectional converter fully controlled switches replace the diodes, as shown in Fig. 2.34a. This topology is called a current sourcerectifier (CSR). In this design, the output voltage,  $V_0$ , is smaller than the amplitude of the input voltage, V, as indicated in Eq. (2.13). Therefore, the CSR is also defined as a Buck Rectifier, where the objective is to provide a constant current  $I_d$  at the output.

$$V_0 < \frac{\sqrt{3}}{2}V \tag{2.13}$$

The boost function is possible by connecting the boost converter inductor on the AC side, as shown in Fig. 2.34b. When the AC voltage is positive and the switch  $T_2$  is ON, the inductor current increases proportionally to the AC voltage and when  $T_2$  turns-off the inductor energy is pumped to the capacitor via diodes D1 and D4. Similarly, when the AC voltage is negative T4 is turned-on. When it turns-off the energy flows via diodes D2 and D3. This topology is known as the voltage source rectifier (VSR). In VSR the output voltage,  $V_0$  is greater than the amplitude of the input voltage, V, as indicated in Eq. (2.14).

Fig. 2.35 Implementation of the three-phase VSR

The VSR is also known as Boost Rectifier with objective to provide a constant voltage  $V_0$  at the output. The CSR and the VSR are dual from each other. Figure 2.35 shows the implementation of a three-phase version of the PWM VSR (with IGBTs). The VSR requires a large capacitor across the output, it is inherently bidirectional and can be applied in several applications where the line side converter must be able to deliver energy back to the source, such as in locomotives, cranes, and renewable energy sources connected to the DC link side.

### 2.1.6.4 AC/AC Converters

AC/AC converters are used to interconnect AC sources, for example from single-phase or a three-phase source to single-phase or a three-phase source. In applications that require variable AC such as light dimmers and AC motor drives, energy is converted from a FVFF to a single-phase or three-phase VVFF or VVVF. A very simple AC/AC converter circuit, to regulate the AC power for a resistive load is shown in Fig. 2.36a and the waveform shown in Fig. 2.36b. This circuit is known as AC controller, which converts from single-phase AC FVFF to VVFF single-phase AC. The fundamental frequency of the input and output is the same. By varying the switch turn-on delay angle, *a*, the amplitude of the fundamental voltage is varied. Typical applications of this circuit are light dimmers and single-phase motor drives used in home appliances. The switch implementation is usually a

Fig. 2.36 Variable voltage fixed frequency (VVFF) AC/ AC converter

Fig. 2.37 Cyclo-converter as VVVF AC/AC converters

Fig. 2.38 Integral-cycle control for (VVVF) AC/AC converter

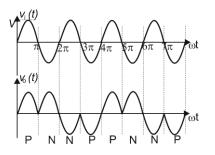

Fig. 2.39 FVFF to VVVF AC/AC converter through a DC link

triac (combination of two SCR's in anti-parallel) controlling the positive half cycle of the AC source with one thyristor and the negative half cycle with the other one. The circuit shown in Fig. 2.37a is a general AC/AC converter, referred to as a cyclo-converter. The switches can be controlled to produce an output voltage with variable amplitude and variable frequency. This is referred to as VVVF output as shown in Fig. 2.37b [1]. The P- and the N-switch are controlled to achieve an output voltage at a frequency lower than the input frequency. Another possible approach for controlling AC/AC converter is known as integral-cycle control, as shown by the waveforms in Fig. 2.38, exemplifying a case where the fundamental frequency of the output is twice the input [2].

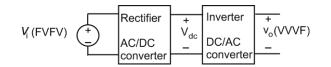

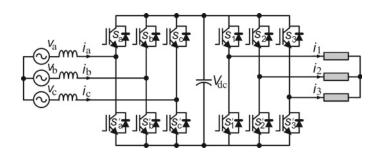

AC/AC conversion can also be obtained by cascading an AC/DC converter with a DC/AC converter, as shown in Fig. 2.39; the approach is known as "DC link conversion" approach. The implementation of this converter with IGBTs is shown in Fig. 2.40. This design allows two-way energy flow and four-quadrant operation and is usually applied to motor drives, electric power generation using asynchronous machines, energy storage systems (such as batteries, UPS, and flywheel energy systems), and the connection of two independent grids. Because a CSR can

Fig. 2.40 Implementation of a FVFF to VVVF AC/AC converter through a DC link

Fig. 2.41 Generalized matrix converters

be modeled as a controllable DC current source, the natural load is a CSI that supports a FVFF to VVVF AC/AC converter through an inductive DC link.

### 2.1.7 Advanced Converter Topologies

Several advanced circuits have been developed and the field of PE is still an emerging and rapidly growing field with new converters. Some of those topologies are application-specific and will be discussed in the next sections.

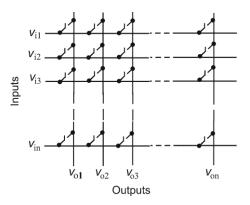

#### 2.1.7.1 The Matrix Converter

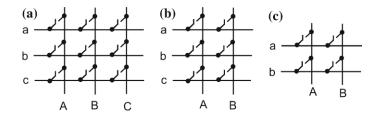

A matrix converter consists of a multi-input multi-output switching matrix that can represent all the switching converters. It can be considered as a fully controlled four-quadrant bidirectional switch, which allows HF operation. Figure 2.41 has an example of a matrix converter with n-inputs and m-outputs. Figure 2.42a shows a specific case where n = m = 3, i.e., a three-phase to three-phase AC/AC

Fig. 2.42 Examples of converters derived from the matrix converter: a AC/AC, b AC/DC, and c AC/DC and DC/DC

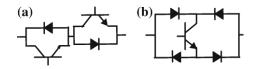

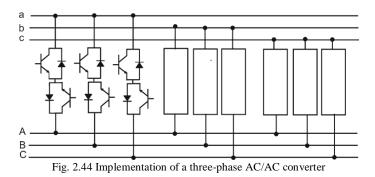

Fig. 2.43 Implementation of a fully bidirectional switch

converter, while Fig. 2.42b shows the case for n = 3 and m = 1, which can be either a three-phase AC/DC converter or a DC to three-phase AC converter. Figure 2.42c shows the converter for n = m = 1 (i.e., any DC/DC converter, single-phase AC/DC converter, or DC to single-phase AC converter).

The bidirectional voltage and current switch can be made of diodes and con- trolled switches as indicated in Figs. 2.43a, b. A three-phase AC to AC converter is shown in Fig. 2.44. Although the matrix converter topology has been around for quite some time, it has gained attention in many applications because of the recent availability of switching power electronic devices and controllers.

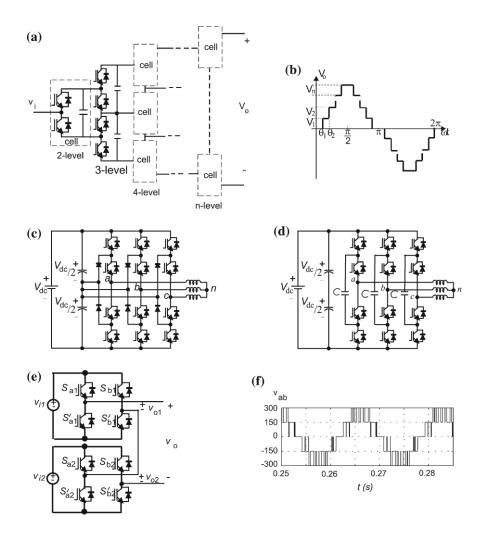

#### 2.1.7.2 Multilevel Inverters

Multilevel inverters are AC/DC converters where a series connection of power electronic devices and split capacitors allow high voltage applications. These inverters are modulated in a way such that the output voltage resembles a staircase

Fig. 2.45 Multilevel inverter: a generalized multi-level converter, b generalized waveforms, c NPC inverter, d flying capacitor inverter, e Hbridge cascaded inverter, and f NPC line voltage waveform

as shown by the generalized multilevel inverter in Fig. 2.45a. A three-level converter consists of series capacitor with a center tap as the neutral where each phase leg of the converter has two pairs of switching devices in series. As the number of levels increase, the synthesized output waveform adds more steps, producing a more refined staircase wave with minimum harmonic distortion, as shown in Fig. 2.45b. Of course, a zero-harmonic distortion of the output wave can be obtained by an infinite number of levels. More levels also mean that series device can provide higher output voltages without any device voltage-sharing problems. Such multiple switches and circuits usually make multilevel inverters more expensive than two-level inverters and are cost-effective only for very specific utility and transmission or distribution power system applications. Different multilevel inverter topologies can be developed from the basic circuit of Fig. 2.45, for example the Diode Clamped (or Neutral-Point Clamped, NPC), and of the Capacitor Clamped or flying capacitor (FC) inverters, as shown in Fig. 2.45c, d, respectively, for three-level inverters. Another popular configuration is the Cascaded H-Bridge, with separate DC sources that is evolved from the two-level inverter, shown in Fig. 2.45e for five-level inverter. All these inverters can also be controlled by PWM techniques [5, 6], of which one example is shown in Fig. 2.45f for the three-level NPC inverter.

## 2.1.8 Control of Power Converters

There are several objectives in the applications of the power converters, such as control of grid voltage, control of current, control of DC link voltage or current, as load or DC connection, control of AC load voltage or current, control of harmonics, control of speed, and so on. The control strategy applied to these cases often deal with the regulation of two variables with different dynamics, one is probably slow and another fast. Examples are: (1) for a rectifier: capacitor voltage (slow) and grid current (fast), (2) for a motor drive: motor speed (slow) and motor current (fast), (3) grid connected inverter: output current (slow) and input voltage (fast).

Fig. 2.46 Slow variable controller

Fig. 2.47 Voltage control of a boost converter

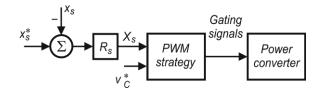

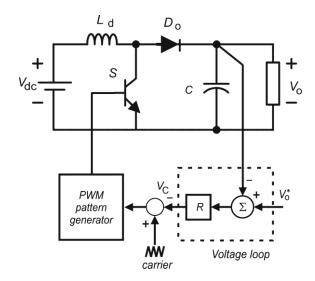

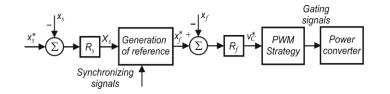

This section will only consider the control of voltages and currents. Figure 2.46 shows a typical PWM control for a slow variable, defined as  $X_s$  is compared with its reference  $X_s^m$ . The resulting error is regulated by the slow variable regulator,  $R_s$ : This regulator has a dynamic performance such as D is directly adjusted so that the slow variable remains regulated. This scheme can be directly applied to DC/DC converters. An example is for a boost DC/DC converter shown in Fig. 2.47, where the objective is to regulate the output voltage,  $V_0$ : For this, the error between the reference and the actual output voltage typically feeds a proportional-integrative (PI) regulator, R. The output of the regulator, the voltage control  $X_s v_c$  is compared to the carrier signal to produce a direct duty ratio PWM control. This type of control can also be employed when only one variable is controlled, such as the voltage in the PWM VSI, and the current in the PWM CSI.

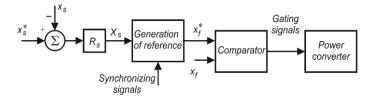

The control scheme can be generalized by using a cascaded strategy, in which any external (slow variable) control defines the reference for an internal (fast variable) control. This kind of control is most often stable since both loops have different dynamics. In order to ensure a desired fast variable profile, the output of regulator  $R_s$  is synchronized with a template signal to define the internal control reference,  $x_f^{\text{m}}$ : As an example, for obtaining near unity power factor operation, the PWM input line current pattern is synchronized with the grid voltage. This can be achieved in two ways: (1) the grid voltage, after filtering, can be used directly as a template for current, or (2) the zero crossing of the grid or the capacitor voltage can be used as a synchronization signal.

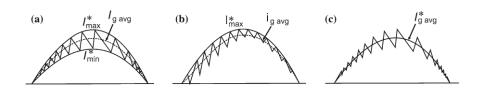

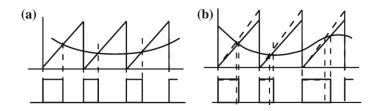

Two schemes for internal control will be now considered: the first one is shown in Fig. 2.48, where  $x_f$  is compared with the internal loop reference,  $x_f^m$ ; in order to generate the gating pulses. Considering only CCM operation, this comparator can:

(1) employ hysteresis (bang-bang) techniques, in which the regulated variable is maintained inside a tolerance band; (2) compare directly  $x_f^{m}$  and  $x_f$ , and (3) compare the integral of  $x_s$  with  $x_f^{m}$ : These three principles are indicated in Fig. 2.49 when the controlled variable is the current and the template is a sinusoidal waveform. In the hysteresis technique shown in Fig. 2.49a the measured current is compared with a tolerance band around the reference. The corresponding switch is turned-on when the current reaches the lower limit of the band, Imm in; and is turned-off when the actual current reaches the upper

limit of the band, Imm ax. The switching frequency varies along the current waveform. Different from the previous technique, case (2),

Fig. 2.48 Block scheme for both slow and fast variable control

Fig. 2.49 CCM: a hysteresis control, b current peak control, and c average current control

Fig. 2.50 Generalized control strategy applied to power converters

Fig. 2.49b, operates with constant switching frequency: the corresponding switch is turned-on by a clock at the beginning of each switching interval and is turned-off when the actual current tries to go beyond the reference. This technique is known as current peak control. In Fig. 2.49c the measured current is integrated so that its average value can be compared with the current reference. For this reason, this approach is known as average current control. For more information on these and other current control schemes the reader is referred to [7-9].

A possible scheme is given in Fig. 2.50 where the control error is regulated by the regulator  $R_{f}$ , whose output furnishes the modulating signal to be applied to the chosen PWM strategy.

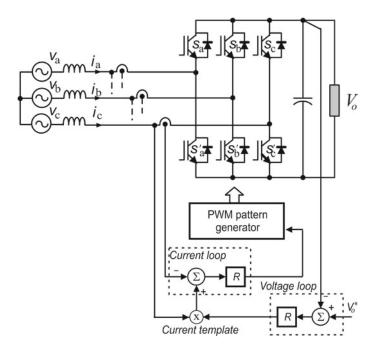

Consider, as an example, the control of the PWM VSR circuit, as shown in Fig. 2.51. In this case, the output voltage and the grid current are the main objectives of the converter control. In the scheme of Fig. 2.51,  $x_s$  is the capacitor

voltage and  $x_f$  is the grid current.

The scheme in Fig. 2.51 includes a fast current controller, a slow DC voltage controller, such as PI, P, Fuzzy or other, and a PWM generator. Since, for power factor control, the input current reference,  $i^m$ ; must be sinusoidal, and the voltage controller output is multiplied by a sinusoidal signal (template signal) with the same frequency and the same phase-shift angle of the mains supply. This template is used to produce the PWM pattern that forces the input currents to follow the desired current template  $I^m$ : This voltage source current controlled PWM rectifier is simpler and more stable than the voltage source voltage controlled PWM rectifier method. Its stability can be ensured by adequate choice of the controller gains [9].

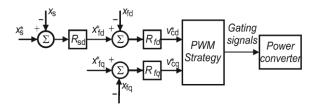

Other control strategies such as the space vector scheme are also used (Fig. 2.52). In this case the voltage controller provides the value of the reference of the *d* component current,  $X_d^m$ ; while the reference of the *q* component current,  $X_q^m$ ; is fixed to zero in order to obtain unitary power factor. These references are compared with the input currents that are represented in *d*-*q* coordinates.

Fig. 2.51 Voltage current controlled PWM rectifier

Fig. 2.52 Space-vector control scheme

Two controllers, typically PI, give the control values  $v_{cd}^{m}$  and  $v_{cq}^{m}$  that generate the PWM pattern which controls the VSR. The inverse transformation dq/abc allows for obtaining the gate drive pulses for the switches.

An important point is that the current controller can be modified by other signals like the signal of balancing capacitor voltages in NPC multilevel converter.

## 2.1.9 Pulse Width Modulation

A PWM pattern is essential in the schemes shown in Figs. 2.46, 2.48, and 2.52. The following sections will present more advanced PWM strategies that are used in control of DC/DC and DC/AC converts. The PWM strategies will be applied to a three-phase PWM VSI and then used for a PWM CSR. It will also be indicated how these strategies can also be applied to three-phase PWM CSIs and PWM VSRs.

Fig. 2.53 Two principles of PWM modulators: a variation of the control voltage and saw-tooth carrier with constant slope, and b variation of the carrier amplitude

### 2.1.10 PWM Techniques for DC/DC Converters

The most popular DC PWM is the voltage-mode control. It is obtained by com- paring a saw-tooth (carrier) with a control voltage (modulating signal). The adjustment of the control voltage allows adjustment of the output pulse width and is shown in Fig. 2.53a. As the control voltage is increased or decreased, the *D* is increased or decreased, causing an increase or decrease in the converter output voltage. For this reason, the voltage-mode control is also called duty-cycle control, which is largely employed to control DC/DC power converters. The pulse-width control can also be obtained by varying the carrier amplitude as shown in Fig. 2.53b. For digital implementation, a digital comparator and the modulating signal are replaced by a sampled signal [8].

### 2.1.11 PWM Techniques for Two-Level Voltage Source Converters

PWM has been the subject of intensive research and is widely employed to control the output voltage of static power converters. A large variety of feed forward and feedback control schemes has been described in the literature [5, 10], such as the Selective Harmonic Elimination PWM, but the most widely used methods of PWM are the sinusoidal pulse-width modulation (SPWM), the non-sinusoidal carrier PWM techniques, the space vector modulation (SVPWM), and the hybrid PWM (HPWM) [11].

Although most of comments in the following will be addressed to the VSIs, PWM rectifiers are very important because of several advantages such as: regulation of input power factor to unity, minimum harmonic distortion of input line currents, near sinusoidal current waveforms, precise regulation of output DC voltage, and bi-directional power flow.