## Design and Analysis of a Single Switch DC-DC Boost Converter Based on Voltage Lift Technique

By

Shabir Ahmad

### MASTER OF SCIENCE

### IN

### ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Board Bazar, Gazipur-1704, Bangladesh.

August 2020

### CERTIFICATE OF APPROVAL

The thesis entitled "**Design and Analysis of a Single Switch DC-DC Boost Converter Based on Voltage Lift Technique**" submitted by Shabir Ahmad, Student No. 1710021016 of the Academic year 2019-20 has been found as satisfactory and accepted as partial fulfillment of the requirement for the Degree of MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING on August 28, 2020.

#### **BOARD OF EXAMINERS:**

Chairman 1. Dr.Golam sarowar (Supervisor) Professor Department of Electrical and Electronic Engineering Islamic University of Technology (IUT)Board Bazar, Gazipur-1704, Bangladesh. 2. Member Dr. Md. Ruhul Amin (Ex-Officio) Professor & Head Department of Electrical and Electronic Engineering Islamic University of Technology (IUT)Board Bazar, Gazipur-1704, Bangladesh. Member 3. Dr. Ashik Ahmed Professor Department of Electrical and Electronic Engineering Islamic University of Technology (IUT)Board Bazar, Gazipur-1704, Bangladesh. 4. Member(External) Dr.Md. Raju Ahmed Professor Department of Electrical and Electronic Engineering Dhaka University of Engineering and Technology (DUET) Gazipur-1707, Bangladesh.

### DECLARATION OF CANDIDATE

It is hereby declared that this thesis report or any part of it has not been submitted elsewhere for the award of any Degree or Diploma.

Dr. Golam SarowarShabir AhmadProfessorStudent No. 1710021016Department of Electrical and Electronic EngineeringAcademic Year: 2019, 2020Islamic University of Technology (IUT)Date: August 28, 2020

# Table of Contents

| CERTIE    | nts<br>ICATE OF APPROVALi                                   |

|-----------|-------------------------------------------------------------|

|           | RATION OF CANDIDATEii                                       |

|           | ablesiii                                                    |

| List of 1 | adiesIII                                                    |

| List of F | iguresiv                                                    |

| Nomencl   | ature viii                                                  |

| Acknowl   | edgmentsix                                                  |

| ABSTRA    | АСТх                                                        |

| CHAPTI    | ER 1 INTRODUCTION AND BACKGROUND1                           |

| 1.1       | Introduction:1                                              |

| 1.2       | Scope of the research work                                  |

| 1.3       | Categories of step-up DC-DC converters                      |

| 1.3.1     | Nonisolated / Isolated                                      |

| 1.3.2     | Unidirectional/Bidirectional                                |

| 1.3.3     | Voltage-Fed/Current-Fed                                     |

| 1.3.4     | Hard Switched/Soft Switched                                 |

| 1.3.5     | NMP/Minimum Phase                                           |

| 1.4       | Statement of problem                                        |

| 1.5       | Thesis Objective7                                           |

| 1.6       | Thesis Organization                                         |

| CHAPTI    | ER 2 PERFORMANCE PARAMETERS OF DC-DC CONVERTER9             |

| 2.1       | Percentage ripple9                                          |

| 2.2       | Effect of parasitics9                                       |

| 2.3       | Converter parameter design9                                 |

| CHAPTI    | ER 3 PROPOSED CONVERTER AND OPERATING PRINCIPLE14           |

| 3         | The proposed converter structure15                          |

| 3.1       | Operation of the proposed high step-up converter in CCM16   |

| 3.1.1     | Voltage and current equations of the inductor <i>L</i> 1:18 |

| 3.1.2     | Voltage and current equations of the inductor <i>L</i> 2:   |

| 3.1.3    | Voltage and current equations of the inductor L3:                                     | 20  |

|----------|---------------------------------------------------------------------------------------|-----|

| 3.1.4    | Voltage equations of the Diodes                                                       | 21  |

| 3.2      | Operation of the proposed high step-up converter in DCM                               | 23  |

| 3.3      | Calculation of critical inductance, rms and efficiency                                | 29  |

| 3.3.1.   | Current equations of the capacitor C4are as follow:                                   | 29  |

| 3.3.2.   | Current equations of Capacitor C1, during $T_{on}$ and $T_{off}$ are given as follow: | 30  |

| 3.3.3.   | Current equations of CapacitorC2, are given as follow:                                | 31  |

| 3.4.     | RMS calculation:                                                                      | 31  |

| 3.5.     | Efficiency analysis:                                                                  | 34  |

| СНАРТЕ   | ER 4 RESULT AND DISCUSSION                                                            | 34  |

| 4.1      | Comparison analysis with recent converters                                            | 36  |

| 4.2      | Simulation and experimental results                                                   |     |

| 4.3      | Simulation and experimental results for CCM                                           |     |

| 4.4      | Simulation and experimental results for DCM                                           | 47  |

| 4.5      | Summary of the comparison results                                                     | 49  |

| СНАРТЕ   | ER 5 CONCLUSION AND FUTURE WORK                                                       | 52  |

| 5.       | Conclusion                                                                            | 53  |

| 5.1      | Summary                                                                               | 53  |

| 5.2      | Research contribution                                                                 |     |

| 5.3      | Recommendation for future work                                                        | 541 |

| Referenc | Ces:                                                                                  | 55  |

# List of Tables

| Table 4.1  | Comparison summary between the proposed converter and other high gain converters        |    |

|------------|-----------------------------------------------------------------------------------------|----|

| Table 4.2. | Switch current comparison between the proposed converter and other high gain converters |    |

| Table 4.3  | Specifications of the proposed converter in CCM                                         |    |

| Table 4.4  | Comparison of simulation and experimental results of the proposed converter in CCM      | 42 |

| Table 4.5  | Specifications of the proposed converter with parasitic elements                        | 42 |

| Table 4.6  | Power loss in conveter components and efficiency                                        | 46 |

| Table 4.7  | Specifications of the proposed converter in DCM                                         | 47 |

| Table 4.8  | Comparison of simulation and experimental results of the proposed converter in DCM.     | 47 |

# List of Figures

| Figure 1.1        | Categorization of step-up dc-dc converters                                                                                                                                                               |    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2        | Isolated and nonisolated dc-dc converter structures; (a) Single-<br>stage (b) floated output and (c) common grounded nonisolated                                                                         | 3  |

| г <sup>.</sup> 10 | dc-dc converters                                                                                                                                                                                         | 4  |

| Figure 1.3        | Unidirectional and bidirectional dc-dc converter structures. (a)<br>Nonisolated Buck and (b) bidirectional boost dc-dc converter, (c)<br>isolated full bridge, and (d) bidirectional DAB dc-dc converter | 4  |

| Figure 1.4        | Current- and voltage-fed converter structures. (a) Current-fed<br>full-bridge structure. (b) Voltage-fed full-bridge structure                                                                           |    |

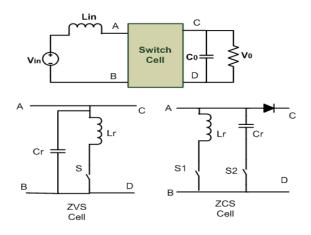

| Figure 1.5        | Various soft switching cells with auxiliary circuits                                                                                                                                                     |    |

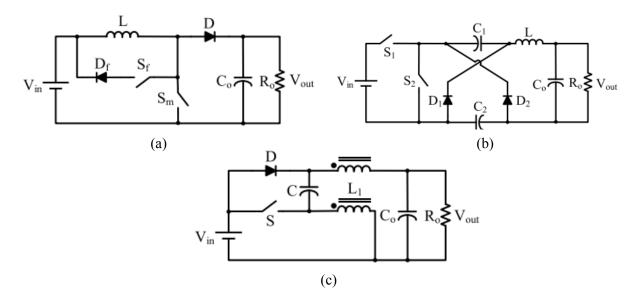

| Figure 1.6        | Different structures of minimum-phase boost converters. (a)<br>Boost converter with single switch, (b) Boost converter with two<br>active switches. (c) Boost converter with magnetic coupling           | 6  |

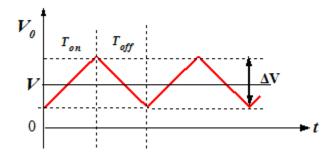

| Figure 2.1        | Output voltage ripple                                                                                                                                                                                    | 9  |

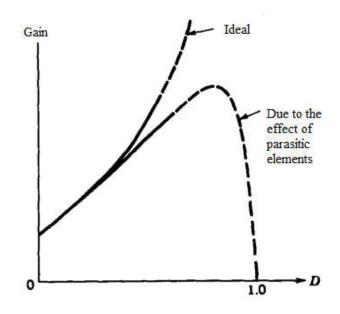

| Figure 2.2        | Effect of the parasitic elements on conversion ratio                                                                                                                                                     |    |

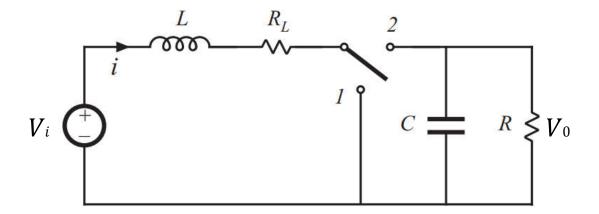

| Figure 2.3        | Conventional boost with inclusion of winding resistance                                                                                                                                                  |    |

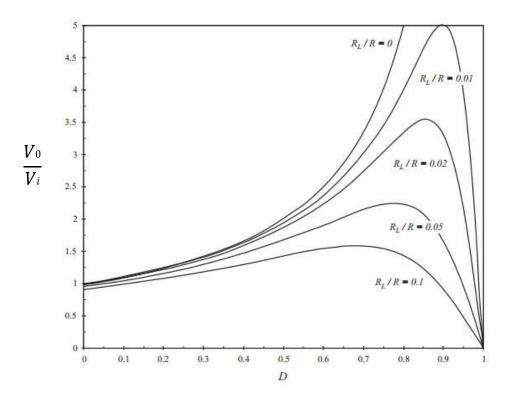

| Figure 2.4        | Effect of RL on voltage gain                                                                                                                                                                             |    |

| Figure 2.5        | Efficiency vs. duty cycle, Conventional boost                                                                                                                                                            | 12 |

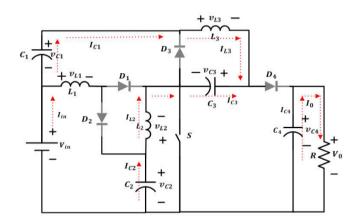

| Figure 3.1        | Structure of the proposed converter                                                                                                                                                                      | 16 |

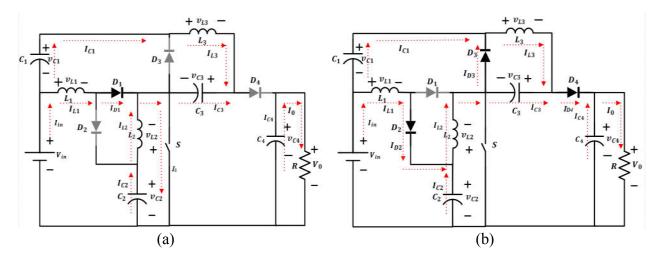

| Figure 3.2        | Proposed converter structure; (a) During on-switching; (c) During Off- switching                                                                                                                         | 16 |

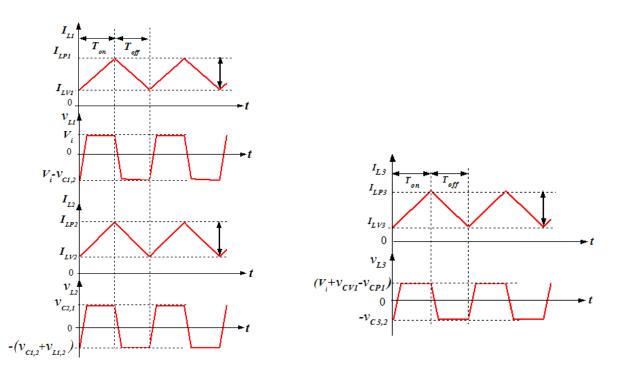

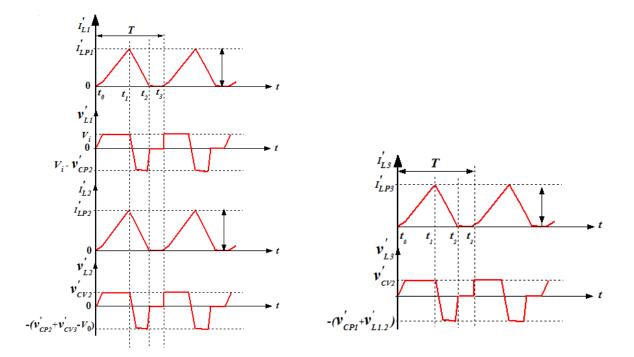

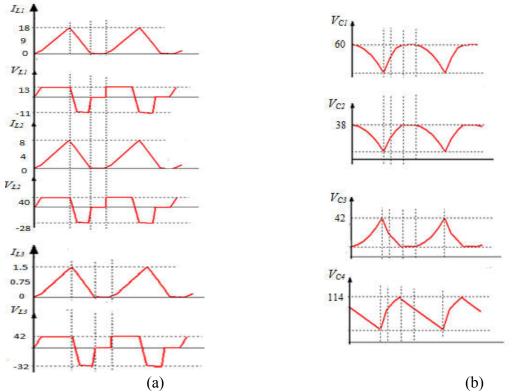

| Figure 3.3        | The current and voltage waveforms in CCM for; Capacitor C1, C2, C3 and C4.                                                                                                                               | 17 |

| Figure 3.4        | The current and voltage waveforms in CCM for; Capacitor C1, C2, C3 and C4                                                                                                                                | 21 |

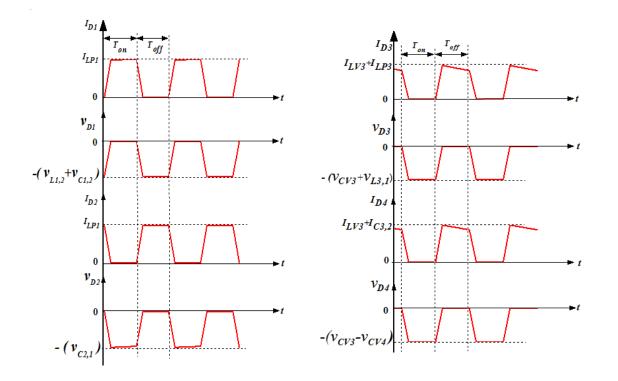

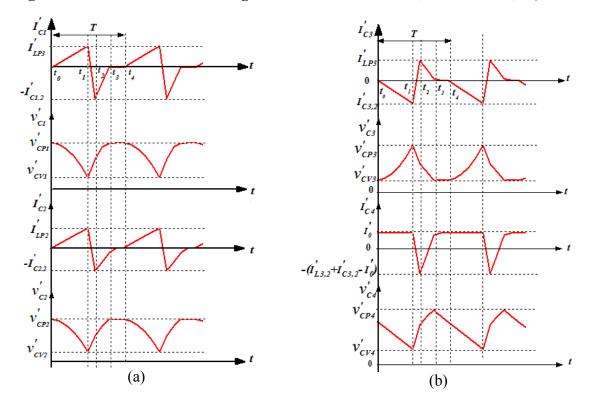

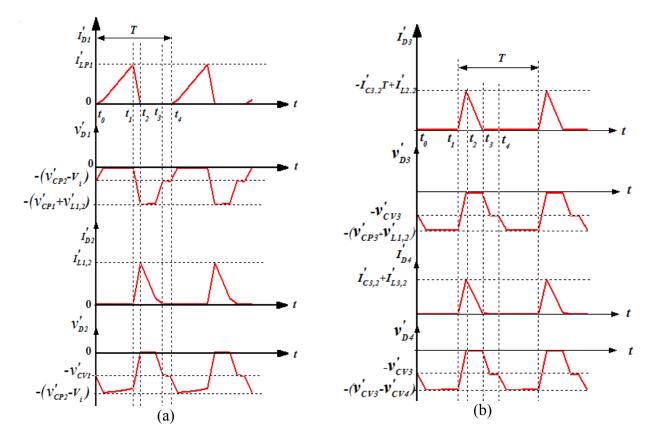

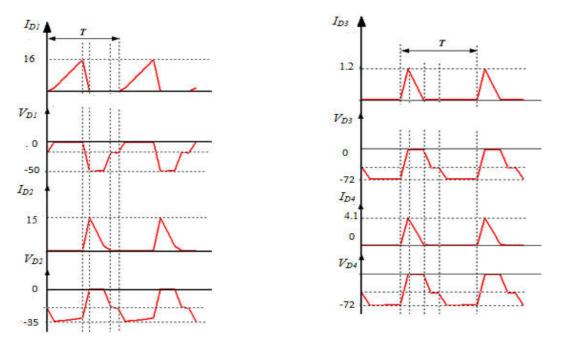

| Figure 3.5        | The current and voltage waveforms in CCM for; Diode D1, D2, D3 and D4                                                                                                                                    | 22 |

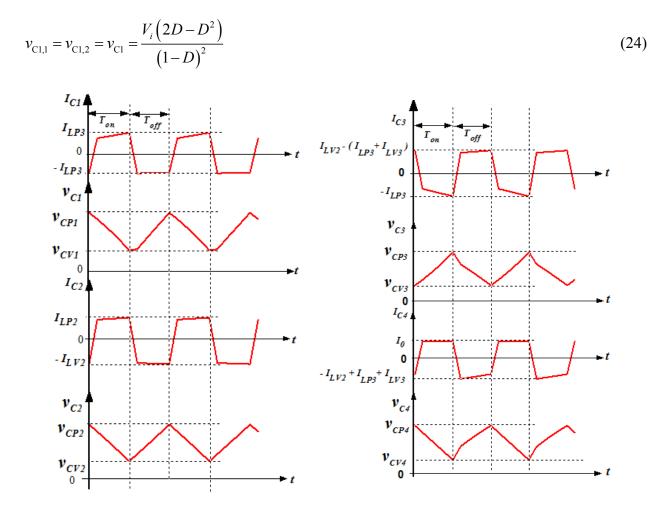

| Figure 3.6        | Proposed converter during discontinuous current time (t2, t3)                                                                                                                                            | 24 |

| Figure 3.7        | The current and voltage waveforms in DCM for; inductors L1, L2 and L3.                                                                                                                                   | 25 |

| Figure 3.8        | Thecurrent and voltage waveforms in DCM for; (a) Capacitors C1, C2; (b) Capacitors C3 and C4                                                                                                             | 25 |

| Figure 3.9        | Thecurrent and voltage waveforms in DCM for ;(a) Diodes D1 and D2 ; (b)DiodesD3 andD4.                                                                                                                   | 27 |

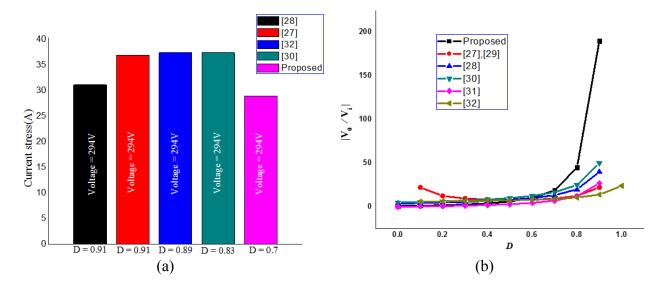

| Figure 4.1        | Comparison between the proposed converter and other converters<br>in terms of (a) Current stress and (b) Voltage gain                                                                                    | 38 |

| Figure 4.2        | Proposed converter Power circuit                                                                                                                                                                         | 40 |

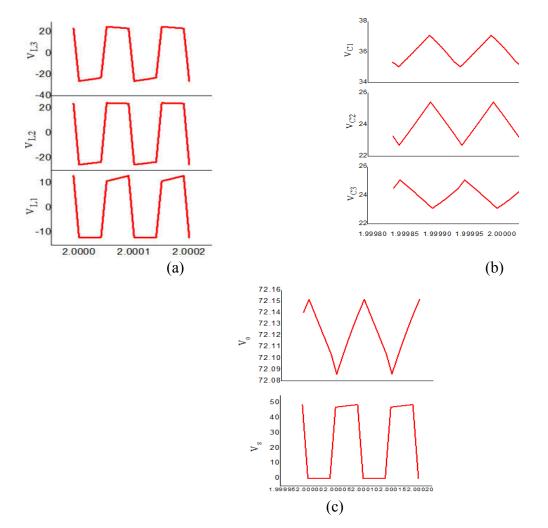

| Figure 4.3        | Voltage waveforms in CCM (simulation) for; (a) inductors; (b) capacitors; (c) switch and outpu                                                                                                           |    |

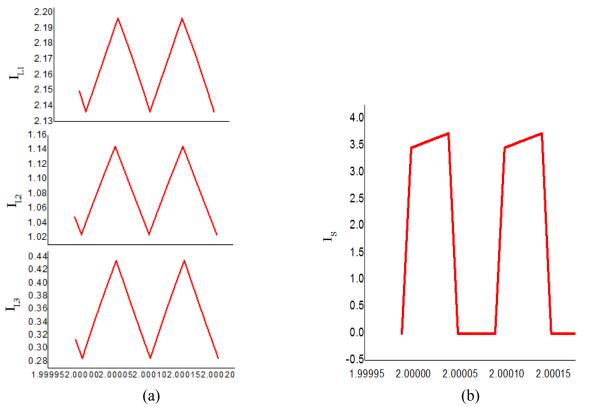

| Figure 4.4        | Current waveforms in CCM (simulation) for; (a) inductors;(b)<br>Switch current                                                                                                                           | 41 |

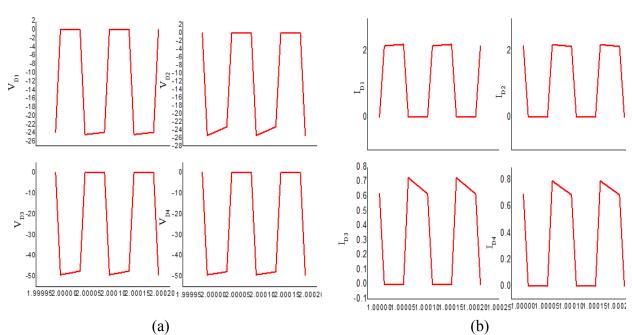

| Figure 4.5        | Simulation waveforms in CCM for; (a) Diode voltages; (b) Diode currents                                                                                                                                  | 41 |

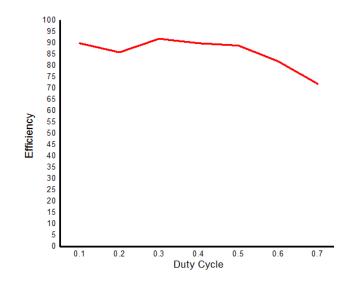

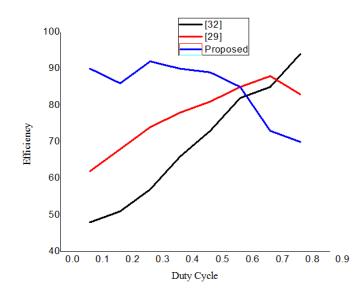

| Figure 4.6        | Efficiency variation with Duty cycle                                                                                                                                                                     | 43 |

| Figure 4.7        | Efficiency variation of the proposed and other recent converters                                                                                                                                         |    |

|             | with duty                                                                                    |    |

|-------------|----------------------------------------------------------------------------------------------|----|

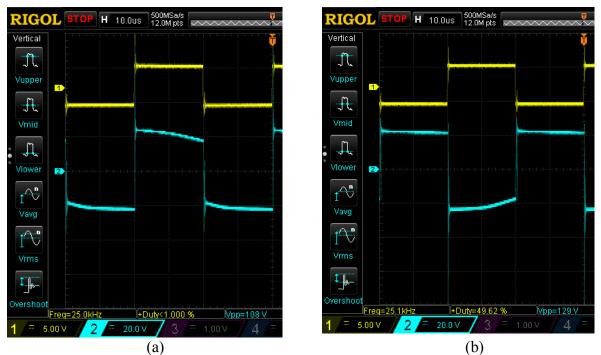

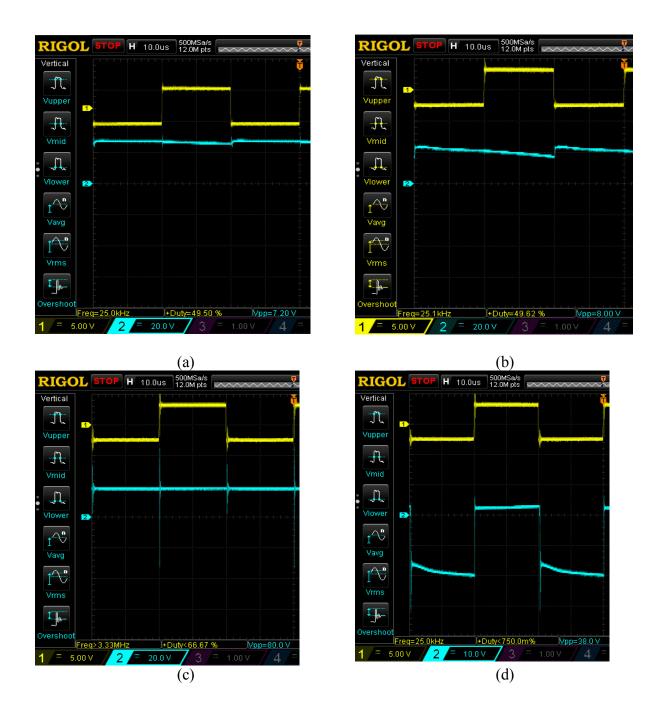

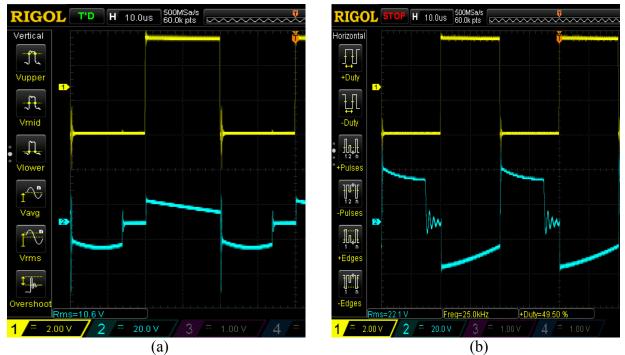

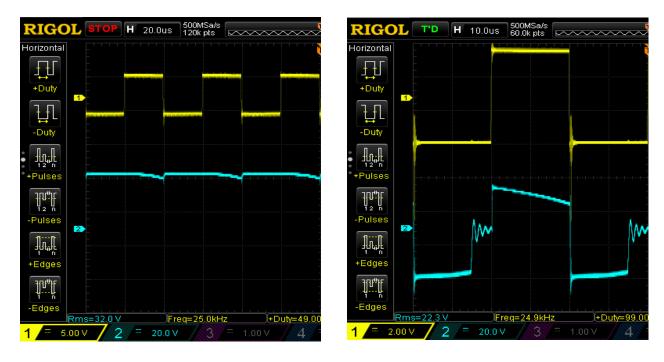

| Figure 4.8  | Experimental waveforms in CCM for; (a) Output Voltage; (b) inductor L1 Current               | 43 |

| Figure 4.9  | Experimental waveforms in CCM for; (a) inductor L2 Voltage;                                  | 44 |

| Figure 4.9  | (b) inductor L3Voltage                                                                       |    |

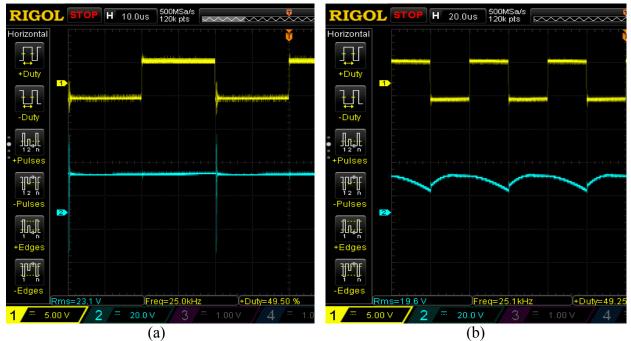

| Figure 4.10 | Experimental waveforms in CCM for; (a) Capacitor C1 Voltage                                  | 45 |

| 11guit 1.10 | (b) Capacitor C2 Voltage; (c)Capacitor C3 Voltage (d) Diode D1                               |    |

|             | Voltage.                                                                                     |    |

| Figure 4.11 | Voltage waveforms (Experimental) in CCM for; (a) Diode D2;                                   | 46 |

| C           | (b) Diode D3; (c)Diode D4; (d) Switch                                                        |    |

| Figure 4.12 | Current and voltage waveforms (simulation) in DCM for; (a) inductors                         | 47 |

|             | L1, L2 and L3; (b) capacitor C1, C2, C3 and C4                                               |    |

| Figure 4.13 | Current and voltage waveforms (simulation) in DCM for Diodes                                 | 48 |

|             | (D1-D4)                                                                                      |    |

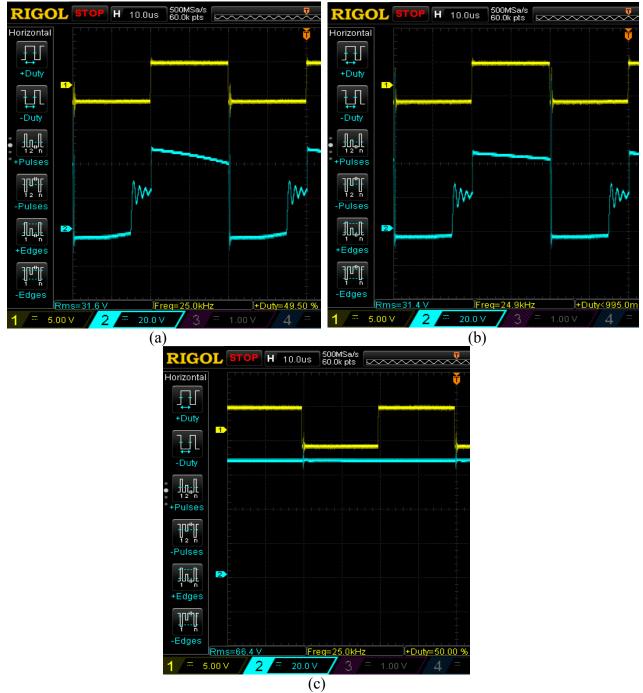

| Figure 4.14 | Voltage waveforms (Experimental) in DCM for; (a) inductor L1;                                | 48 |

|             | (b) inductor L2                                                                              |    |

| Figure 4.15 | Voltage waveforms (Experimental) in DCM for; (a) capacitor C1;                               | 49 |

|             | (b) inductor L3                                                                              | 10 |

| Figure 4.16 | Voltage waveforms (Experimental) in DCM for; (a) capacitor C2;                               | 49 |

| D: 417      | (b) capacitor C3                                                                             | 50 |

| Figure 4.17 | Voltage waveforms (Experimental) in DCM for; (a) Diode D1;                                   | 50 |

| Eigung 4 19 | (b) Diode D2<br>Vialta sa visua forma (Even arim antal) in DCM form (a) Diada D2:            | 51 |

| Figure 4.18 | Voltage waveforms (Experimental) in DCM for; (a) Diode D3;<br>(b) Diada D4; (a) Canagitar C4 | 51 |

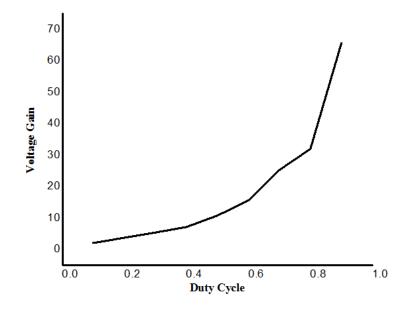

| Figure 4 10 | (b) Diode D4; (c) Capacitor C4<br>Voltage gain vs. duty evels (DCM expertise)                | 51 |

| Figure 4.19 | Voltage gain vs duty cycle (DCM operation)                                                   |    |

### Nomenclature

| $v_{L1,1}$ , $v_{L2,1}$ , $v_{L3,1}$                                                                    | Inductors voltageat time interval $T_{on}$   |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------|

| $v_{L1,2}$ , $v_{L2,2}$ , $v_{L3,2}$                                                                    | Inductors voltageat time interval $T_{off}$  |

| <i>v</i> <sub>C1,1</sub> , <i>v</i> <sub>C2,1</sub> , <i>v</i> <sub>C3,1</sub>                          | Capacitors voltageat time interval $T_{on}$  |

| <i>VC</i> 1,2 , <i>VC</i> 2,2 , <i>VC</i> 3,2                                                           | Capacitors voltageat time interval $T_{off}$ |

| <i>v</i> <sub>D1</sub> , <i>v</i> <sub>D2</sub> , <i>v</i> <sub>D3</sub> , <i>v</i> <sub>D4</sub>       | Diodes voltages at time interval $T_{off}$   |

| <i>v</i> <sub>CV1</sub> , <i>v</i> <sub>CV2</sub> , <i>v</i> <sub>CV3</sub> , <i>v</i> <sub>CV4</sub> , | Capacitors discharge voltages                |

| <i>VCP</i> 1 , <i>VCP</i> 2 , <i>VCP</i> 3, <i>VCP</i> 4,                                               | Capacitors peak-charge voltages              |

| $i_{L1,1}, i_{L2,1}, i_{L3,1}$                                                                          | Inductors currentat time interval $T_{on}$   |

| $i_{L1,2}$ , $i_{L2,2}$ , $i_{L3,2}$                                                                    | Inductors currentat time interval $T_{off}$  |

| $i_{LV1}, i_{LV2}, i_{LV3}$                                                                             | Inductors discharge current                  |

| $i_{LP1}, i_{LP2}, i_{LP3}$                                                                             | Peak inductors current                       |

| $i_{C1,1}, i_{C2,1}, i_{C3,1}, i_{C4,1}$                                                                | Capacitors current at time interval $T_{on}$ |

| $i_{C1,2}$ , $i_{C2,2}$ , $i_{C3,2}$ , $i_{C4,2}$                                                       | Capacitors currentat time interval $T_{off}$ |

| $\Delta i_{L1,} \Delta i_{L2,} \Delta i_{L3}$                                                           | Inductors ripple current                     |

|                                                                                                         |                                              |

|                                                                                                         | The load (a) and source (i) average para     |

$I_0, V_o, I_i, V_i$   $C_{OSS}, Q_{rr}, r_s, t_r, t_f$

$r_D, V_F$

The load (*o*) and source (*i*) average parameters Switch parameters (Output capacitance, reverse recovery charge, series resistance, rise time and fall time). Diode parameters (Diode series resistance and forward voltage drop).

### Acknowledgments

First and foremost, I offer gratitude to the Almighty Allah (SWT) for giving me the capability to do this work with good health.

I want to express my sincere gratitude to my supervisor, Prof. Dr. Golam Sarowar, Department of Electrical and Electronic Engineering (EEE), Islamic university of technology (IUT), for his support and encouragement throughout this work. The valuable discussions with him gave me many vital impulses that contributed considerably to both my scientific and personal development. I am also indebted to all the faculty and staff members of the EEE department, IUT. My sincere thanks to all those who assisted me in connection with this work.

Finally, I am grateful to my family members, particularly my beloved Father, for his continuous support and inspiration.

### ABSTRACT

Renewable energy systems (solar, fuel cells, batteries) are one of the trending research topics due to its ease of availability, sustainability, and environmental friendliness. DC-DC converters impart a crucial role in these renewable energy systems while boosting up the voltages to higher levels. In this thesis, a novel structure of DC-DC boost converter based on voltage lift technique is presented. The extensive analysis is performed for the proposed converter in continuous current mode (CCM) and discontinuous current mode (DCM) along with the voltage and current relations of converter elements and semiconductor devices. Moreover, critical values of inductors are determined to investigate the boundary conditions between CCM and DCM. It was firmly concluded that while considering the lesser number of elements and semiconductor devices for the same input voltage the proposed converter can yield comparatively high voltage gain than the conventional boost dc-dc converters. Root mean square (RMS) values of the voltages and currents for the elements and semiconductors are also calculated along with the converter's efficiency at various duty cycles. Simulation results of the proposed converter are provided in CCM and DCM using PSIM software. Finally, to avail the desired validation of acquired simulation results a laboratory prototype of the proposed converter is tested and comparisons were made with the theoretical analysis.

### CHAPTER 1

### INTRODUCTION AND BACKGROUND

#### **1.1 Introduction**:

Advances in technology and sharp elevation in human living standards have caused significant augmentation in world energy demand over the last decade. To meet this growing energy demand employing the conventional power generation methods (using fossil fuels) induces adverse environmental effects, such as greenhouse effect, air pollution due to emission of SO2 and Nitrogen oxides, etc. [1]. For years, researchers have demonstrated a substantial inclination towards the boundless other alternate energy sources such as fuel cells, wind energy, photovoltaic (PV) systems, and batteries that feature cleanliness and sustainability. However, energy resources such as principally photovoltaic cells and fuel cells yield significantly lower voltage levels (up to 50V). Therefore, step-up converters are greatly encouraged to boost up this low level voltage for various applications [2, 3]. Conventional non-isolated step-up PWM converters such as boost, buck-boost, and SEPIC, etc., possess noticeable features in regards to its simplicity and cost-effectivity. Unfortunately, the gain of these converters is limited due to circuit parameters and operation at high duty cycles to attain high voltage gains, which in results reduces the converter efficiency to a paramount extent. Various voltage-boosting techniques have been elucidated in the literature to achieve augmented gain while operating at low duty ratios and improved efficiency [4, 5, 6].

Major voltage-boosting techniques that can be found in the literature are segregated into five categories, i.e., switched inductor, voltage multiplier, voltage lift (VL), switched capacitor (SC), magnetic coupling, and multistage/-level converters. New power converter topologies with the inclusion of the above voltage-boosting techniques are continuously being proposed and developed to meet the rising demand for power conversion applications [7]. Switched-capacitor can achieve high-voltage conversion gain [8-9]. However, these converters require a number of switches, which increases the complexity of the control strategies and associated driving circuitry. This converter topology also suffers from poor regulation, which results in pulsating input current. A number of voltage multiplier circuits are presented in the literature for high boost applications as they can be implemented easily in any circuit [10, 11]. However, a number of cells required for high gains also multiplies, which results in enhanced power loss, cost, and circuit size. The magnetic coupling-based boosting technique for isolated and non-isolated converters is consistently proposed [12, 13]. Even though, these converters have dominant boost ability; however, they suffer from obvious drawbacks. For instance, leakage inductance must be recycled to avoid large voltage spikes. Furthermore, with the increment of turns ratio converter size also tends to rise. Multilevel DC-DC converters are suitable for high-power high-voltage applications [14, 15]. Despite various noticeable advantages such as high-power density, modularity structure, and reliability, these converters also require a large number of components, high-priced and deteriorated efficiency, due to a higher number of stages.

Eventually, among the aforementioned voltage-boosting techniques, voltage lift (VL) technique is a prestigious, relatively simple and amenable in many converters. This technique has been widely employed in the literature introduced by Luo (VL Luo converters) [16, 17]. VL

technique utilizes fundamental energy storage elements i.e; inductors and capacitors in combination with power semiconductor switches and diodes to boost the input voltage level to higher voltage levels. The energy storage elements transfer the low input energy (in steps) to the output capacitor with a much higher level because of its storage capabilities. High power density, greater efficiency, plain structure and cost-effectiveness, and small output voltage ripple as compared to the other techniques are the crucial features of this technique. Furthermore, absence of additional switches which complicates the control scheme of the converter is a prominent outcome of this technique.

#### **1.2** Scope of the research work

In this thesis, a modified non-isolated structure of a conventional boost converter using a single switch is proposed to achieve a high voltage gain. The proposed converter possesses the capability of achieving high voltage gain at a reasonable duty cycle condition, which makes it more suitable for medium and high voltage applications for instance in DC microgrids, they can be used to interface various low power voltage sources like batteries, photovoltaic (PV) panels and fuel cells into a common DC bus (380V). This common bus is further coupled to the AC grid through a centralized DC/AC inverter. The extensive operation of the proposed converter is also analyzed in both CCM and DCM while the current and voltage equations of each converter element are extracted. In order to determine the operation mode of the converter, critical values of inductors are extracted to distinguish between CCM and DCM. The efficiency of the proposed converter is calculated, and a detailed comparison of efficiency change with the duty cycle is illustrated.

#### **1.3** Types of step-up dc-dc converters

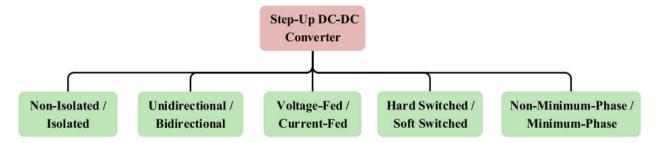

A broad classification of step-up dc-dc converters is illustrated in Figure 1.1. The main features and respective major circuits of each class are explained in the following sections.

Figure 1.1 Categorization of step-up dc-dc converters

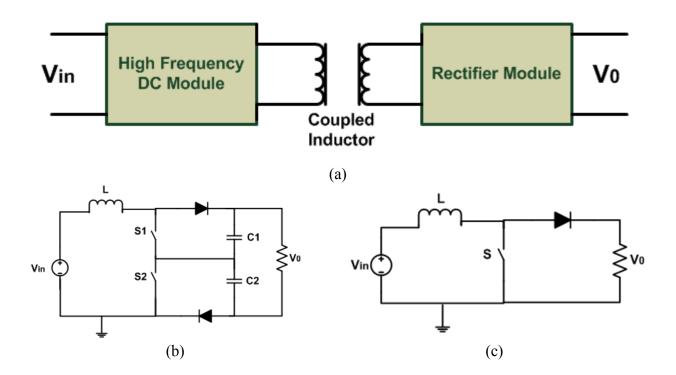

#### 1.3.1 Nonisolated / Isolated

Non-isolated DC-DC converters usually make use of inductors and there is no dielectric separation between the input and the output. Figure. 1.2 (a) illustrates a basic nonisolated PWM boost dc-dc converter which is comprised of three components i.e; a diode, a switch, and an inductor. Figure 1.2(b) shows a general three-level boost converter with floated output. Due to their relatively smaller size, low cost, and lower switching losses and elevated efficiency, significant research has been conducted on the study of nonisolated dc-dc converters. Moreover, nonisolated dc-dc converters does not necessarily require magnetic coupling to be built.

Nonisolated structures with magnetic coupling are used when high voltage gain and efficiency is a major concern.

# Figure 1.2. Various isolated and nonisolated converter circuits; (a) isolated single-stage (b) nonisolated three-level boost converter and (c) nonisolated DC-DC boost converter.

Transformer or coupled inductor is used to achieve electrical isolation between the input and output. Electrical isolation is typically essential for loads which are prone to noise and faults and when security is a major concern. For example in medical, avionics and military applications. Figure. 1.2(c) illustrates the diagram of an isolated coupled inductor based dc-dc converter.

#### 1.3.2 Unidirectional/Bidirectional

Such converters utilize unidirectional semiconductors for exmaple diodes and power MOSFETs, which take into account unidirectional power flow. Examples of some unidirectional dc-dc converters are demonstrated in Figure. 1.3(a). These converters utilizes single-quadrant switches and hence current can not flow in the reverse direction.

Figure 1.3. Unidirectional and bidirectional DC-DC converter structures. (a) Nonisolated Boost and (b) bidirectional boost DC-DC converter, (c) isolated full bridge, and (d) bidirectional DAB DC-DC converter.

Figure. 1.3(b) demonstrates the bi-directional arrangement of a nonisolated dc-dc converter. In these converters two-quadrant switches are employed which allows for bidirectional current flow.

Unidirectional step up converters are appropriate for applications where high output voltage is required and losses due to diodes do not affect the circuit's efficiency. Conversely, bidirectional dc-dc converters are suitable for applications where low output voltage is expected and diodes losses become dominant. Figure. 1.3(c) illustrates diagram of an isolated unidirectional dc-dc converter. The converter consist of inverter stage and then high-frequency transformer next to rectification stage.

The increased demand for applications with bidirectional energy transfer has led to the enlarged usage of bidirectional dc-dc converters. Converters with bidirectional capability are used in railway transportation, renewable energy systems, automotive transportation, aerospace applications, uninterruptable power supplies, elevators and escalators, supercapacitors, batteries, smart grid applications etc. Figure. 1.3(d) demonstrates schematic diagram of an isolated bidirectional dual active bridge (DAB) converter, which is a popular type of isolated bidirectional dc-dc converter.

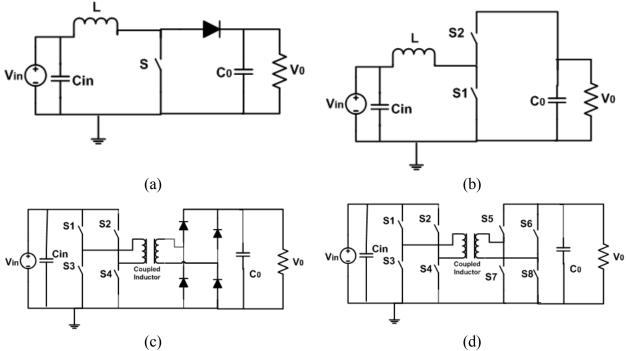

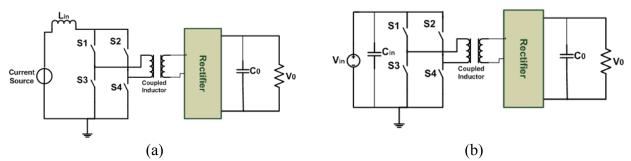

#### 1.3.3 Voltage-Fed/Current-Fed

Based on the input circuitry, DC-DC converters are classified into voltage-fed and current-fed converters. The voltage-fed converter consist of an input filter capacitor ( $C_{in}$ ) and generally

convert the input voltage to a lower output. Voltage-fed full-bridge converter can be utilized for high-power applications. The schematic diagram is demonstrated in Figure. 1.4(a). On the other hand, current-fed DC-DC converters comprises an input inductor and capable to convert the input voltage to a higher output voltage.

Figure 1.4. Current- and voltage-fed converter structures. (a) Current-fed full-bridge structure. (b) Voltage-fed full-bridge structure.

Current-fed converters are suitable for low voltage applications for instance photovoltaics and fuel cells. The input inductor supplies continuous input current, particularly with small ripple.

#### 1.3.4 Hard Switched/Soft Switched

Hard-switched converters suffer from EMI issues due to high dv/dt and di/dt at switching transition. High switching frequency operation is restricted in such converters as switching losses is proportional to frequency. Nevertheless, increasing power density calls for the high-frequency operation of dc-dc converters which lessen the size of the storage components. On the contrary, soft-switched converters can trim down the above drawbacks by utilizing stray inductance and capacitance to attain zero-voltage switching or zero-current switching. During switching transitions voltage and current are zero and hence the converter can operate at relatively high switching frequency, which reduces size and weight of the converter. Figure. 1.5 illustrates a universal switch cell type dc–dc converter.

Figure 1.5. Different soft-switching cells (ZVS and ZCS).

#### **1.3.5** Non-minimum phase (NMP)/Minimum Phase (MP)

NMP converters contains a right half plane (RHP) zero in their transfer function. Designing a Controller for such converters is somehow complex because of the fact that the closed-loop poles are liable to move towards right half plane as the gain increases in conventional controllers which causes destabilization of the system. Therefore, conventional controllers will not serve the purpose of achieving high converter gain . Different techniques can be used to minimize the effect of the RHP zero in step-up converters.

Tristate boost converters eradicate the RHP zero and are used in applications where fast-response boost action is required. A tristate boost converter is illustrated in Figure. 1.6(a). The RHP zero can be entirely removed at the preferred operating point by applying a proper control technique on the converter. Another circuit with no RHP zero is demonstrated in Figure. 1.6(b). Another way to eradicate RHP zero is to use magnetic coupling as shown in Figure. 1.6(c).

Figure 1.6. Different structures of minimum-phase boost converters. (a) Boost converter with single switch, (b) Boost converter with two active switches. (c) Boost converter with magnetic coupling.

#### 1.4 Statement of the Problem

A PWM boost converter is an essential voltage boost circuit with numerous features that make it suitable for a range of applications such as renewable energy systems, fuel cells etc. The extensive applications of high boost converters is due to its low number of elements, simple design implementation, and manufacturing.

A significant research has been conducted in achieving efficient, reliable, small-sized, and lightweight boost converters for diverse power applications. A few of these demands can be merely accomplished by using second-order, third-order, and fourth-order fundamental converters, e.g., Cuk, boost, SEPIC and Zeta converters. Moreover, basic push-pull, flyback, half-, and fullbridge converters are even prevalent and are used in various applications. However, more complicated recent topologies that employ different voltage-boosting techniques are also presented in the literature for instance interleaved, multilevel, or cascaded topologies, or using voltage multiplier cells (VMC) [18]–[22]. However, for applications with the low input voltage but high output voltage, these conventional converters suffer from increased voltage stress on the semiconductor devices and circuit elements. Furthermore, the converter has to operate at extreme duty cycles, which in result, induce significant power loss. Various circuits (combined switched capacitors (SCs) and/or coupled inductors) and techniques are presented to boost the voltage level while operating at low duty cycles. A new hybrid DC-DC converter is presented in [23], different switched capacitors techniques and coupled inductors are merged with a conventional boost converter to achieve high voltage gain. The advantages of this technique are high voltage, low current and voltage stress on elements, and using a single switch. However, the converter has a large number of components, which results in increased cost, losses, and size of the converter. Converter presented in [24] can achieve high voltage gain at low duty cycles, and the structure can be extended to n stages, which further increases the voltage gain of the converter. The voltage stress on the components compared with output voltage is decreased. However, a number of switches are employed, which complicates the control tactics, and hence the cost as separate driving circuitry is required to drive the switches. A new structure by combining coupled inductor and voltage lift technique is presented in [25]. High voltage gain can be achieved by adjusting the turns ratio of the coupled inductor, and stress on semiconductors is low; however, the voltage gain is proportional to the turns ratio of the coupled inductor, which increases the size and causes EMI issues. A new topology of step-up dc-dc converter using voltage lift technique is proposed in [26]. Capacitor-inductor-capacitor (CLC) cells are developed to increase the voltage gain, and the converter can further be extended to N-lift topology to boost up the voltage gain. The converter employs a single switch and has low switching voltage; however, high voltage gain is achieved at the price of utilizing a large number of elements, which degrades converter efficiency and also increases the cost.

#### **1.5** Thesis Objective

The principal objective of this research work is to design and analyze a novel single-switch DC-DC boost converter, capable of achieving high voltage gain with the minimal number of circuit components. However, more specifically, the goals include:

- a. To design a novel single-switch DC-DC Boost coveter with high voltage gain based on voltage lift technique.

- b. To determine the critical value of inductor of the proposed converter for CCM and DCM operation.

- c. To implement a prototype of the proposed converter in the laboratory and analyze the performance.

- d. To compare the performance of the proposed converter with the existing converters.

#### 1.6 Thesis Organization

The writeup for this research work can be organized as follows:

In chapter two, The performance parameters of DC converters are discussed. The effect of parasitic elements on the converter's voltage gain and efficiency is studied extensively. Graphs of efficiency vs. duty cycle and gain vs. duty cycle in the presence of parasitic elements are demonstrated.

In chapter three, the operation of the proposed structure in CCM and DCM is studied in detail. The fundamental waveforms (current and voltage) of the proposed circuit elements is demonstrated, which is performed in PSIM software. Moreover, numerous critical current and voltage relations are also established along with the voltage gain of the converter in CCM operation. Furthermore, Relations of the critical inductance of the inductors are extracted by applying boundary conditions to determine the mode of operation of the proposed converter. Voltage and current RMS values are calculated, and the efficiency of the converter is analyzed in detail.

In chapter four, The comparison analysis between the proposed converter and other recent converters is studied exhaustively. Current stress and voltage gain of the currently proposed converter is compared with some recently proposed converters while considering the least number of components count for the same input voltage. The significant results obtained from Software simulations performed in PSIM and experimental outcomes (both CCM and DCM operations) from laboratory prototype are provided to acutely acquire their validations. Power loss in each converter element is computed, and the converter's efficiency is analyzed at various duty cycles.

In chapter five, the research work presented in this thesis is summarized, and key results are displayed. The possible modification and control strategy of the proposed converter is to be studied in the future.

#### CHAPTER 2

#### PERFORMANCE PARAMETERS OF DC-DC CONVERTER

In this thesis, the analysis of the converter is performed, realizing the inductors current and capacitors voltage ripple to be ignored. The converter components such as a switch, diode, and passive components are considered ideal. Nonidealities or parasitics of practical devices and components may, however, greatly affect some performance parameters of the dc-dc converter such as efficiency, voltage gain, and percentage ripple.

#### 2.1 Percentage Ripple

The actual output voltage consists of a desired dc component voltage, plus a small undesired ac component, as shown in **Figure 2.1**. It is impossible to build a perfect low pass filter that allows the dc component to pass but completely remove the components at the switching frequency and its harmonics. so the low pass filter must allow at least some small amount of high-frequency harmonics generated by the switch to reach the output.

Figure 2.1. Output voltage ripple.

The output voltage switching ripple should be small in any well-designed converter, since the goal is to produce dc output. For example, in a computer power supply having a 3.3 V output, the switching ripple is normally required to be less than a few tens of millivolts, or less than 1% of the dc component. Therefore it is always a good approximation to assume that the magnitude of the switching ripple is much smaller than the dc voltage. This approximation, known as small ripple approximation, greatly simplifies the analysis of the converter and is used in this thesis.

#### **2.2 Effect of Parasitics**

The parasitic elements in the proposed converter are due to the losses associated with the inductors, the capacitors, the switch and the diode. **Figure 2.2** qualitatively shows the effect of these parasitics on the voltage transfer ratio. Unlike the ideal characteristics, in pratice,  $V_0 / V_i$  declines as the duty ratio approaches unity. The parasitic elements have been ignored in the the simplified analysis presented in the succeeding sections; hovever, practically they can not be avoided and their effect is taken into consideration.

Figure 2.2 Effect of the parasitic elements on conversion ratio.

To elaborately explain the effect of the parasitics, taking the example of a conventional boost converter with the inclusion of induction copper loss (resistance of winding), as shown in **Figure 2.3**.

Figure 2.3. Conventional boost with the inclusion of winding resistance.

The final gain equation can be written as follow:

$$\frac{V_0}{V_i} = \frac{1}{D'(1 + R_L / D'^2 R)}$$

(2.1)

Where *D*′ is the off-switching time.

The plot of voltage gain vs. D for various  $R_L$  is shown in **Figure 2.4**. It can be seen that equation (2.1) has two terms. The 1<sup>st</sup> term  $\frac{1}{D'}$  represents ideal conversion ratio excluding  $R_L$ . The 2<sup>nd</sup> term,  $\frac{1}{(1+RL/D'^2R)}$ , represent the effect of the winding resistance. The gain will be approximately equal to ideal conversion ratio $\frac{1}{D'}$  if  $R_L$  is much smaller than the product  $D'^2R$ . If the value of  $R_L$  is considerable then the gain  $\frac{V_0}{V_i}$  will have reduced value compared with the ideal value.

Figure 2.4. Effect of *R<sub>L</sub>* on voltage gain.

When the duty cycle is unity, the inductor series resistance  $R_L$  causes significant change in the  $\frac{V_0}{V_i}$  vs D graph. The gain should approach infinity as D approaches 1 but actually the curve trim

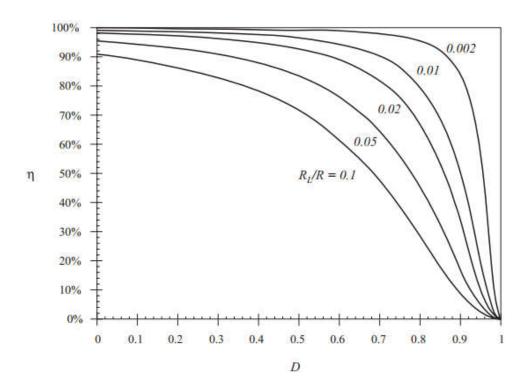

down to zero. The reason is that when duty cycle is unity, the switch is always in on position. There will be no connection between the inductor and the output, so no energy will be transferred to the output, and the output will become zero. The efficiency relation of the converter is written as follow:

$$\eta = \frac{1}{(1 + RL / D'^2 R)}$$

The current in the inductor will tends to rise and its value is limited only by the inductor series resistance  $R_{L}$ . A significant power is lost, while no power is transferred to the load; therefore, we can assume that the converter efficiency tends to zero at unity duty cycle, as illustrated in **Figure 2.5**.

Figure 2.5. Efficiency vs. duty cycle, Conventional boost.

The example discussed here is fairly straightforward, wherein only one loss component is present. Practible converters are considerably more complicated and contain a large number of loss components.

#### 2.3. Converter parameters Design.

Design of inductors and capacitors is based on the permissible voltage and current fluctuation range. The voltage and current stress on elements is also an important design consideration.

The inductor  $L_1$  can be designed based on the fundamental inductor voltage relation:

$$v_{L1,1} = V_i = L_1 \frac{di_{L1,1}}{dt} = L_1 \frac{\Delta i_{L1}}{T_{on}}$$

The value of  $\Delta i_{L_1}$  is restricted by permissible fluctuation limit i.e. x% of  $i_{L_1}$ . Various applications have certain permissible fluctuation range which should not be increased above that range for smooth operation. From above relation Inductor  $L_I$  is calculated as:

$$L_{1} = \frac{V_{i}D}{\%x_{L1}i_{L1}f} = \frac{V_{i}D(1-D)^{2}}{\%xI_{0}(1+D)f}$$

Similarly the value of inductor  $L_2$  can be calculated as:

$$v_{L2,1} = L_2 \frac{di_{L2,1}}{dt} = L_2 \frac{\Delta i_{L2}}{T_{on}} = v_{C2,1} = \frac{V_i}{(1-D)}$$

$$L_2 = \frac{v_{C2}D}{\% x i_{L2}f} = \frac{V_i D}{\% x I_0 (1+D)f}$$

Also, inductor  $L_3$  is calculated as:

$$v_{L3,2} = L_3 \frac{di_{L3,2}}{dt} = L_3 \frac{\Delta i_{L3}}{T_{off}} = v_{C3,2}$$

$$L_3 = \frac{v_{C3}(1-D)}{\% x i_{L3} f} = \frac{V_0 (1-D)^2 - V_i}{(1-D)^{\%} x I_0 f}.$$

By similar aurguments, capacitor  $C_1$  can be calculated from the fundamental current relation:

$$i_{C1,1} = C_1 \frac{dv_{C1,1}}{dt} = C_1 \frac{\Delta v_{C1}}{T_{on}}$$

$$C_1 = \frac{i_{C1,1}D}{\% x v_{C1} f} = \frac{I_0 D (1-D)^2}{\% x V_i (2D - D^2) f}$$

Also capacitor  $C_2$  is calculated as:

$$i_{C2,1} = C_2 \frac{dv_{C2,1}}{dt} = C_2 \frac{\Delta v_{C2}}{T_{on}}$$

$$C_2 = \frac{i_{C2,1}D}{\% x v_{C2} f} = \frac{I_0 D (1+D)}{\% x V_i f}$$

Similarly capacitor  $C_3$  is calculated as follow:

$$i_{C3,1} = C_3 \frac{dv_{C3,1}}{dt} = C_3 \frac{\Delta v_{C3}}{T_{on}}$$

$$C_3 = \frac{i_{C3,1}D}{\% x v_{C3} f} = \frac{I_0 D (1-D)^2}{\% x (V_0 (1-D)^2 - V_i) f}$$

And capacitor  $C_4$  is calculated as:

$$i_{C4,1} = C_4 \frac{dv_{C4,1}}{dt} = C_4 \frac{\Delta v_{C4}}{T_{on}}$$

$$C_4 = \frac{i_{C4,1}D}{\% v_{C4}f} = \frac{I_0 D}{\% v_0 f}$$

### CHAPTER 3

### PROPOSED CONVERTER AND OPERATING PRINCIPLE

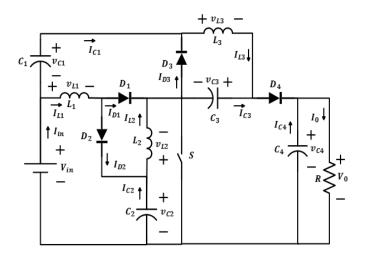

#### 3.0 The proposed Converter structure

The proposed structure elucidated in **Figure 3.1**. Which is encompassed of three inductors, a single switch, four capacitors, and four diodes. The operation of the switch is controlled by a PWM technique with a switching frequency of 25 kHz. To simplify the analysis of the proposed converter, few assumptions are made. i) To eradicate the inconsistent behavior of the converter, the steady-state operation of the converter is considered. ii)The voltage ripple for each capacitor is neglected due to a sufficiently large capacitor value; therefore, the capacitor's voltage in each switching period is identical. iii) The switch and diodes are considered ideal.

The voltage-lift technique has been employed to boost the output voltage. Voltage-lift technique was first introduced by Luo (and the converters are called Luo converters). The voltage-lift technique basically utilizes inductors and capacitors to store the input energy and transfers this energy to the output at higher level. These elements act like electronic charge pump which takes the energy in one step and then releases it in the next step. For instance, in the proposed circuit, inductor  $L_1$  and capacitor  $C_2$  act as primary sources of storing the input energy. This stored energy is then transferred by inductor  $L_2$  and capacitor  $C_1$  and finally the energy is transferred to the output capacitor by the inductor  $L_3$  and capacitor  $C_3$ .

The input voltage is augmented in steps and finally transferred to the output capacitor. During the on-switching period, the input energy is stored in the magnetic field of the inductor  $L_1$ , while inductors  $L_2$  and  $L_3$  are getting the energy from capacitors  $C_1$  and  $C_2$  (energy stored during offswitching). In the next cycle, when the switch is off, inductors  $L_2$  and  $L_3$  transfer the stored energy to the capacitors  $C_2$  and  $C_4$  (output). In this way, the energy is transferred by the storage elements to the output with amplitude greatly enhanced than the input.

Figure 3.1 Structure of the proposed step-up converter.

#### 3.1. Operation of the proposed high step-up converter in CCM.

In this section, the key focus is given to extensively elaborate the CCM operation of the proposed circuit performed in PSIM software. The overview of the various waveforms is presented for capacitors, diodes, switch, and inductors, which incorporates both on-switching and off-switching states. Moreover, various prominent current and voltage relations are also demonstrated availed theoretically. The proposed converter structure during CCM operation is shown in **Figure 3.2**.

Figure 3.2 Proposed converter structure; (a) During on-switching; (b) During Offswitching

During the on switching period, diodes  $D_2$ ,  $D_3$  and  $D_4$  are reverse biased and diode  $D_1$  is forward biased. In this state, supply voltage  $V_i$  is providing energy to the inductor  $L_1$  and hence its current value is linearly increased from its minimum value ( $I_{LV1}$ ) to its peak value ( $I_{LP1}$ ), as illustrated in

**Figure 3.3**. In the meanwhile, Capacitor  $C_2$  is discharged through the inductor  $L_2$  by releasing its stored energy. The voltage of the Capacitor  $C_2$  is dropped to the lowest value  $v_{CV2}$  and inductor  $L_2$  current is raised from the lowest value  $I_{LV2}$  to its highest value  $I_{LP2}$ . Also, the capacitor  $C_1$  is discharged through the inductor  $L_3$  and capacitor  $C_3$ . As a result, capacitor  $C_1$  voltage is dropped to the lowest value  $v_{CV1}$  and current in the inductor  $L_3$  is augmented from its minimum value  $I_{LV3}$  to its maximum value  $I_{LP3}$ , while the voltage of the capacitor  $C_3$  is raised from its minimum value  $v_{CV3}$  to its maximum value  $v_{CP3}$  as shown in **Figure 3.4**. During on-period, the load is isolated from rest of the circuit as  $D_4$  is reverse biased, capacitor  $C_4$  is providing energy to the load and its voltage is dropped from its maximum value  $v_{CP4}$  to the lowest value  $v_{CV4}$ .

During the off-switching period, diodes  $D_2, D_3$  and  $D_4$  are forward biased and diode  $D_1$  is reverse biased. Inductor  $L_1$  is providing energy to Capacitor  $C_2$  by losing its stored energy and capacitor's  $C_2$  voltage is raised from the lowest value  $v_{CV2}$  to maximum value  $v_{CP2}$ , while current in the inductor is dropped to a minimum value  $I_{LV1}$ . Also inductor  $L_2$  is supplying energy to a capacitor  $C_1$  by liberating its stored energy and voltage of  $C_2$  is raised to a peak value of  $v_{CP1}$ thereby the current in the inductor  $L_2$  is dropped to  $I_{LV2}$ . Inductor  $L_3$  and capacitor  $C_3$  both are supplying energy to the capacitor  $C_4$  and load. Current in inductor  $L_3$  is reduced to  $I_{LV3}$  while the voltage of the capacitor  $C_3$  is dropped to  $v_{CV3}$  and voltage of the capacitor  $C_4$  is raised to a peak value of  $v_{CP4}$ . Currents and voltages of all the four diodes in CCM are illustrated in Figure 3.5.

Figure 3.3. The current and voltage waveforms in CCM for; Inductor  $L_{1}$ ,  $L_{2}$  and  $L_{3}$

#### 3.1.1 Voltage and current equations of the inductor $L_1$ :

By applying KVL when the switch is on, inductor  $L_1$  voltage is obtained as:

$$v_{L1,1} = V_i = L_1 \frac{di_{L1,1}}{dt} = \frac{\Delta i_{L1,1}}{T_{on}}$$

(1)

From Eq. (1), the inductor  $L_1$  current is obtained as:

$$i_{L1,1} = \frac{V_i}{L_1} t + I_{LV1}$$

(2)

Inductor current at the end of the on-switching period is given as:

$$i_{L2,1}\Big|_{t=T_{on}} = I_{LP2}$$

(3)

By applying KVL when the switch is turned off, inductor  $L_1$  voltage is obtained as:

$$v_{L1,2} = V_i - v_{C2,2} = L_1 \frac{di_{L1,2}}{dt} = -\frac{\Delta i_{L1}}{T_{off}}$$

(4)

From Eq. (4), the inductor  $L_1$  current is obtained as:

$$i_{L1,2} = -\frac{\left(V_i - v_{C2,2}\right)}{L_1}t + I_{LP1} \quad (5)$$

By using inductor volt-sec balance rule for  $L_1$ , Average capacitor  $C_2$  voltage is obtained as:

$$\int_{0}^{T_{out}} V_{i} dt + \int_{0}^{T_{off}} \left( V_{i} - V_{C2,2} \right) dt = 0$$

$$V_{C2,2} = \frac{V_{i}}{(1 - D)}$$

(6)

Neglecting small ripple of the capacitor  $C_2$  voltage, its average value is given as:

$$v_{C2,1} = v_{C2,2} = v_{C2} = \frac{V_i}{(1-D)}$$

(7)

#### 3.1.2 Voltage and current equations of the inductor $L_2$ :

By applying KVL during the on-switching period, inductor  $L_2$  voltage is obtained as:

$$v_{L2,1} = L_2 \frac{di_{L2,1}}{dt} = v_{C2,1} = \frac{V_i}{(1-D)}$$

(8)

From Eq. (8), the inductor  $L_2$  current is obtained as:

$$i_{L2,1} = \frac{v_{C2,1}}{L_2} t + I_{LV2}$$

(9)

Inductor current at the end of the on-switching period is given as:

$$i_{L2,1}\Big|_{t=T_{on}} = I_{LP2}$$

(10)

By applying KVL in the time interval of  $T_{off}$ , inductor  $L_2$  voltage is obtained as:

$$v_{L2,2} = -(v_{C1,2} + v_{L1,2}) \tag{11}$$

Also,

$$v_{L2,2} = v_{C3,2} + v_{C2,2} - V_0 = L_2 \frac{di_{L2,2}}{dt}$$

(12)

From Eq. (12), the inductor  $L_2$  current is obtained as:

$$i_{L2,2} = -\frac{\left(v_{C3,2} + v_{C2,2} - V_0\right)}{L_2}t + I_{LP2}$$

(13)

By using inductor volt-sec balance rule for  $L_2$ , Average capacitor  $C_3$  voltage can be calculated:

$$\int_{0}^{T_{off}} v_{C2,1} dt + \int_{0}^{T_{off}} \left( v_{C3,2} + v_{C2,2} - V_0 \right) dt = 0$$

$$\frac{V_i}{(1-D)} DT + v_{C3,2} \left( 1-D \right) + \frac{V_i}{(1-D)} (1-D) T - V_0 \left( 1-D \right) T = 0$$

$$v_{C3,2} = V_0 - \frac{V_i}{(1-D)^2}$$

(14)

Neglecting small ripple of the capacitor  $C_2$  voltage, its average value is given as:

$$v_{C3,1} = v_{C3,2} = v_{C3} = V_0 - \frac{V_i}{\left(1 - D\right)^2}$$

(15)

#### 3.1.3 Voltage and current equations of the inductor $L_3$ :

By applying KVL in the time interval of  $T_{on}$ , inductor  $L_3$  voltage is obtained as:

$$v_{\rm L3,1} = L_3 \frac{di_{\rm L3,1}}{dt} = v_{\rm L1,1} + v_{\rm C1,1} - v_{\rm C3,1}$$

(16)

From Eq. (16), the inductor  $L_2$  current is obtained as:

$$i_{L3,1} = \frac{\left(v_{L1,1} + v_{C1,1} - v_{C3,1}\right)}{L_3}t + I_{LV3}$$

(17)

Inductor current at the end of the on-switching period is given as:

$$i_{L3,1}|_{t=T_{on}} = I_{LP3}$$

(18)

By applying KVL in the time interval of  $T_{on}$ , inductor  $L_3$  voltage is obtained as:

$$v_{L3,2} = L_3 \frac{di_{L3,2}}{dt} = -v_{C3,2} \tag{19}$$

From Eq. (19), the inductor  $L_3$  current is obtained as:

$$i_{L3,2} = \frac{V_{C3,2}}{L_3} t + I_{LP3}$$

(20)

Inductor current at the end of the on-switching period is given as:

$$i_{L3,2}|_{t=T_{off}} = I_{LV3}$$

(21)

By using inductor volt-sec balance rule for  $L_3$ , Average capacitor  $C_1$  voltage can be calculated:

$$\int_{0}^{T_{off}} \left( v_{L1,1} + v_{C1,1} - v_{C3,1} \right) dt + \int_{0}^{T_{off}} - \left( v_{C3,2} \right) dt = 0$$

$$V_{i}DT + v_{C1,1}DT - \left[ V_{0} - \frac{V_{i}}{\left( 1 - D \right)^{2}} \right] DT - \left[ V_{0} - \frac{V_{i}}{\left( 1 - D \right)^{2}} \right] (1 - D)T = 0$$

$$v_{C1,1} = \frac{V_{0} \left( 1 - D \right)^{2} - V_{i} - V_{i} \left( 1 - D \right)^{2}}{\left( 1 - D \right)^{2}}$$

(22)

Also, By using the inductor volt-sec balance rule for  $L_2$ We have:

$$\int_{0}^{T_{on}} v_{\text{C2,1}} dt + \int_{0}^{T_{off}} - \left(v_{\text{L1,2}} + v_{\text{C1,2}}\right) dt = 0$$

Solving for  $v_{Cl,2}$ , the following is obtained:

$$v_{\rm C1,2} = \frac{V_{\rm i} \left(2D - D^2\right)}{\left(1 - D\right)^2} \tag{23}$$

Neglecting small ripple of the capacitor  $C_1$  voltage, its average value is given as:

Figure 3.4. The current and voltage waveforms in CCM for; Capacitor  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ .

#### 3.1.4 Voltage equations of the Diodes

When the switch is on, diode  $D_I$  is reverse biased, and all other diodes are forward biased. By applying KVL in the time interval of  $T_{on}$ , Diode  $D_I$  voltage can be obtained as:

$$V_{D1} + V_{C1} + V_{L1,1} = 0$$

$$V_{D1} = -(V_{C1} + V_{L1,1}) \tag{25}$$

By applying KVL in the time interval of  $T_{off}$ , Diode D<sub>2</sub> voltage can be obtained as:

$$V_{in} - V_{L1,1} - V_{D2} - V_{C2} = 0$$

$$V_{D2} = V_{in} - V_{L1,1} - V_{C2}$$

(26)

By applying KVL in the time interval of  $T_{off}$ , Diode D<sub>3</sub> voltage can be obtained as:

$$V_{D3} + V_{L3,2} + V_{C3} = 0$$

$$V_{D3} = -(V_{L3,2} + V_{C3})$$

(27)

By applying KVL in the time interval of  $T_{off}$ , Diode D<sub>3</sub> voltage can be obtained as:

$$V_{D4} + V_{C4} - V_{C3} = 0$$

$$V_{D4} = V_{C3} - V_{C4}$$

(28)

Voltage gain is calculated by using inductor volt-sec balance rule for  $L_3$  and putting values of  $v_{C1,1}$ ,  $v_{C3,1}$  and  $v_{C3,2}$ , we have:

$$\int_{0}^{T_{off}} \left( v_{L1,1} + v_{C1,1} - v_{C3,1} \right) dt + \int_{0}^{T_{off}} - \left( v_{C3,2} \right) dt = 0$$

$$V_{i}DT + \frac{V_{i} \left( 2D - D^{2} \right)}{\left( 1 - D \right)^{2}} DT - \left[ V_{0} - \frac{V_{i}}{D^{2}} \right] DT = 0$$

$$\frac{V_{0}}{V_{i}} = \frac{\left( 1 + D \right)}{\left( 1 - D \right)^{2}}$$

(29)

Considering lossless converter, the current ratio is extracted as:

$$\frac{I_0}{I_i} = \frac{(1-D)^2}{(1+D)}$$

(30)

#### 3.2. Operation of the proposed high step-up converter in DCM

In this section operation of the proposed converter in DCM is extensively analyzed. Various modes of operation are enlightened, and key waveforms are illustrated in DCM operation. The proposed converter has three modes of operation during DCM. The equivalent circuits during DCM operation are shown in **Figures.** 3.2, and 3. The characteristic waveforms during DCM are also demonstrated in **Figures** (3.7-3.9).

#### Mode I.

When the switch is on, i.e., at the time  $(t_0, t_l)$ , diodes  $D_2$ ,  $D_3$  and  $D_4$  are reverse biased and diode  $D_1$  is forward biased, as shown in Fig 3.2. Input voltage  $V_i$  provides energy to the inductor  $L_1$  and its current is increased to the maximum value  $I_{LP1}$  (Figure 3.7). Also, capacitor  $C_2$  is discharged through the inductor  $L_2$  and its voltage is dropped to the lowest value  $v_{CV2}$  (Figure 3.8). This energy is stored by the inductor  $L_2$  and its current is raised from the lowest value  $I_{LV2}$  to its highest value  $I_{LP2}$ . In the meanwhile, capacitor  $C_1$  is supplying energy to the inductor  $L_3$  and capacitor  $C_3$  and current of the inductor  $L_3$  is raised to its maximum value  $I_{LP3}$  while the voltage of the capacitor  $C_3$  reaches to the highest value  $v_{CV1}$ . Since diode  $D_4$  is reverse biased, capacitor  $C_4$  is providing energy to the load and its voltage is dropped to its lowest value  $v_{CV4}$ . Currents and voltages of all the four diodes are illustrated in Figure 3.9.

#### Mode II.

During the off-switching period at a time  $(t_1, t_2)$ , diode  $D_1$  is reverse biased and diodes  $D_2$ ,  $D_3$ and  $D_4$  are forward biased. Inductor  $L_1$  is supplying energy to the capacitor  $C_2$  and the current falls to zero at the end of time interval  $(t_1, t_2)$ , while the voltage of the capacitor  $C_2$  is increased to its maximum value  $v_{CP2}$ . Also, inductor  $L_2$  current falls to zero at the end of time interval  $(t_1, t_2)$ , providing energy to the capacitor  $C_1$  thus its voltage is increased to the highest value  $v_{CP1}$ . During this time, inductor  $L_3$  and capacitor  $C_3$  both are supplying energy to the capacitor  $C_4$  and load and thus the voltage of the capacitor  $C_4$  is reached to a peak value  $v_{CP4}$ . Current in inductor  $L_3$  is reduced to zero while the voltage of the capacitor  $C_3$  is dropped to the lowest value  $v_{CV3}$  at the end of the time interval  $(t_1, t_2)$ .

#### Mode III.

At the time  $(t_2, t_3)$ , all the four diodes are reverse biased, and current in the three inductors is zero, as shown in **Figure 3.6**. Voltage of capacitors  $C_1$  and  $C_2$  is maintained at peak values  $v_{CP1}$  and  $v_{CP2}$  respectively as capacitor's  $C_1$  and  $C_2$  current is zero during this time interval. Also the voltage of the capacitor  $C_3$  remains at the lowest value  $v_{CV3}$  during the time  $(t_2, t_3)$  as a capacitor  $C_3$  current is zero. Capacitor  $C_4$  continues to supply energy to the load by releasing its stored energy. Voltage of capacitor  $C_4$  is reduced to the minimum value  $v_{CV4}$  at the end of the time interval  $(t_2, t_3)$ .

Figure 3.6. Proposed converter during the discontinuous current ( $t_2$ ,  $t_3$ ).

Figure 3.7. The current and voltage waveforms in DCM for; inductors  $L_1$ ,  $L_2$ , and  $L_3$ .

Figure 3.8. The current and voltage waveforms in DCM for; (a) Capacitors  $C_1$ ,  $C_2$ ; (b) Capacitors  $C_3$  and  $C_4$ .

At t = DT, Inductor  $L_2$  voltage is given as:

$$v'_{L2,1} = v'_{C2,1} = L_2 \frac{di'_{L2,1}}{dt} = L_2 \frac{\Delta i'_{L2}}{\Delta t}$$

(34)

At t = D'T, Inductor  $L_2$  voltage is given as:

$$v'_{L2,2} = \left(v'_{C3,2} + v'_{C2,2} - V'_{0}\right) = L_{2} \frac{di'_{L2,2}}{dt} = -L_{2} \frac{\Delta i'_{L2}}{\Delta t}$$

(35)

By using inductor volt-sec balance rule for  $L_2$  and solving for average capacitor  $C_3$  voltage, we have:

$$\int_{0}^{DT} v'_{C2,1} dt + \int_{0}^{DT} \left( v'_{C3,2} + v'_{C2,2} - V'_{0} \right) dt = 0$$

$$\frac{V_{i} \left( D + D' \right)}{D'} T + \frac{V_{i} \left( D + D' \right)}{D'} D' T + v'_{C3,2} D' T - V_{0} D' T = 0$$

$$v'_{C3,2} = V_{0} - \frac{V_{i} \left( D + D' \right)^{2}}{\left( D' \right)^{2}}$$

(36)

Figure 3.9. The current and voltage waveforms in DCM for ;(a) Diodes  $D_1$  and  $D_2$ ; (b)Diodes  $D_3$  and  $D_4$ .

By using inductor volt-sec balance rule for  $L_2$  and solving for average capacitor  $C_3$  voltage, the following has resulted:

$$\int_{0}^{DT} v'_{C2,1} dt + \int_{0}^{DT} \left( v'_{C3,2} + v'_{C2,2} - V'_{0} \right) dt = 0$$

$$\frac{V_{i} \left( D + D' \right)}{D'} T + \frac{V_{i} \left( D + D' \right)}{D'} D' T + v'_{C3,2} D' T - V_{0} D' T = 0$$

$$v'_{C3,2} = V_{0} - \frac{V_{i} \left( D + D' \right)^{2}}{\left( D' \right)^{2}}$$

(37)

At t = DT, Inductor  $L_3$  voltage is given as:

$$v'_{L3,1} = v'_{L1,1} + v'_{C1,1} - v'_{C3,1} = L_3 \frac{di'_{L3,1}}{dt} = L_3 \frac{\Delta i'_{L3}}{\Delta t}$$

(38)

At t = D'T, Inductor  $L_3$  voltage is given as:

$$v'_{L3,2} = -v'_{C3,2} = L_3 \frac{di'_{L3,1}}{dt} = -L_3 \frac{\Delta i'_{L3}}{\Delta t}$$

(39)

By using inductor volt-sec balance rule for  $L_3$  and solving for average capacitor  $C_1$  voltage, the following has resulted:

$$\int_{0}^{DT} v'_{C2,1} dt + \int_{0}^{DT} - \left(v'_{L1,2} + v'_{C1,2}\right) dt = 0$$

$$v'_{C1,2} = \frac{V_i \left(D + D'\right) D + DD'}{\left(D'\right)^2}$$

(40)

At t = D''T, Voltage of Inductors $L_1$ ,  $L_2$ , and  $L_3$  is zero as the current is zero during D''T.

Where the time intervals DT, D'T and D''T are  $\frac{t_0 - t_1}{T}$ ,  $\frac{t_1 - t_2}{T} = \frac{t_1 - t_3}{T}$  and  $\frac{t_2 - t_3}{T} = \frac{t_3 - t_4}{T}$ , respectively.

Voltage gain can be calculated by using inductor volt-sec balance rule for  $L_3$  and by putting values of  $v'_{C1,1}$ ,  $v'_{L1,1}$ ,  $v'_{C3,1}$  and  $v'_{C3,2}$ , we have:

$$\int_{0}^{DT} \left( v'_{L1,1} + v'_{C1,1} - v'_{C3,1} \right) dt + \int_{0}^{DT} - \left( v'_{C3,2} \right) dt = 0$$

$$V_{i}DT + \frac{V_{i} \left( D + D' \right) D + DD'}{\left( D' \right)^{2}} DT - V_{0}DT - V_{0}D'T + \frac{V_{i} \left( D + D' \right)^{2}}{\left( D' \right)^{2}} DT + \frac{V_{i} \left( D + D' \right)^{2}}{\left( D' \right)^{2}} D'T = 0$$

$$V_{i} \left[ D + \frac{\left( D + D' \right) \left( D \right)^{2} + D' \left( D \right)^{2}}{\left( D' \right)^{2}} + \frac{\left( D + D' \right)^{3}}{\left( D' \right)^{2}} \right] = V_{0} \left( D + D' \right)$$

$$\frac{V_{0}}{V_{i}} = \frac{\left( D + D' \right)^{2} + D^{2} + DD'}{D'^{2}}$$

(41)

#### 3.3. Calculation of critical inductance, rms of elements current, and efficiency

The critical inductance of inductors is of great importance as it determines the boundary between CCM and DCM. At boundary conditions, the inductors current just reaches zero, and this occurs at a critical value of inductor(s). In the proposed structure, three inductors are used; therefore, three critical values for  $L_1$  ( $L_{C1}$ ),  $L_2$  ( $L_{C2}$ ), and  $L_3$  ( $L_{C3}$ ) will be calculated. In order to find the critical values, the following equation has to be fulfilled.

$$I_{LV1} + I_{LV2} + I_{LV3} = 0 ag{42}$$

Where  $I_{LVI}$ ,  $I_{LV2}$ , and  $I_{LV3}$  are the minimum values of the three inductors.

#### **3.3.1.** Current equations of the capacitor $C_4$ are as follow:

$$I_{C4,1} = -I_0 (43)$$

$$I_{C4,2} = I_{L3,2} + I_{C3,2} - I_0 \tag{44}$$

By using charge balance rule for capacitor  $C_4$ , we have:

$$\int_{0}^{T_{off}} (I_{C4,1})dt + \int_{0}^{T_{off}} (I_{C4,2})dt = 0$$

$$\int_{0}^{T_{off}} -(I_{0})dt + \int_{0}^{T_{off}} (I_{L3,2})dt + \int_{0}^{T_{off}} (I_{C3,2})dt + \int_{0}^{T_{off}} -(I_{0})dt = 0$$

$$-(I_{0})DT + \frac{v_{C3,2}}{2L_{3}}t^{2}|_{t=T_{off}} + I_{LP3}(1-D)T + \int_{0}^{T_{off}} (I_{C3,2})dt - I_{0}(1-D)T = 0$$

(45)

By applying boundary conditions (i.e.,  $I_{LV3} = 0$ ) to above Eq. and solving for integral of  $I_{C3,2}$ , we have:

$$\int_{0}^{T_{off}} (I_{C3,2}) dt = I_0 T - \frac{T^2}{2L_3} \left( V_0 \left( 1 - D \right)^2 - V_i \right) - I_{LV3}$$

(46)

By using charge balance rule for capacitor  $C_3$  and applying boundary conditions, the value  $L_3$  is calculated as:

$$\int_{0}^{T_{on}} (I_{C3,1}) dt + \int_{0}^{T_{off}} (I_{C3,2}) dt = 0$$

$$-\frac{\left(v_{L1,1}+v_{C1,1}-v_{C3,1}\right)}{2L_{3}}D^{2}T^{2}-I_{LV3}DT+I_{0}T-\frac{T^{2}}{2L_{3}}\left(V_{0}\left(1-D\right)^{2}-V_{i}\right)-I_{LV3}=0$$

$$-\frac{D^{2}T^{2}}{2L_{3}}\left[V_{i}-\frac{V_{0}\left(1-D\right)^{2}-V_{i}}{\left(1-D\right)^{2}}+\frac{V_{i}\left(2D-D^{2}\right)}{\left(1-D\right)^{2}}\right]-I_{LV3}DT+I_{0}T-\frac{T^{2}}{2L_{3}}\left(V_{0}\left(1-D\right)^{2}-V_{i}\right)-I_{LV3}=0$$

$$-\frac{D^{2}T^{2}}{2L_{3}}\left[\frac{2V_{i}-V_{0}\left(1-D\right)^{2}}{\left(1-D\right)^{2}}\right]-I_{LV3}DT+I_{0}T-\frac{T^{2}}{2L_{3}}\left(V_{0}\left(1-D\right)^{2}-V_{i}\right)-I_{LV3}=0$$

$$-\frac{T^{2}}{2L_{3}}\left[\frac{2V_{i}-V_{0}\left(1-D\right)^{2}}{\left(1-D\right)^{2}}D^{2}+\left(V_{0}\left(1-D\right)^{2}-V_{i}\right)\right]-I_{LV3}DT+I_{0}T-I_{LV3}=0$$

$$-\frac{T^{2}}{2L_{3}}\left[\frac{V_{i}\left(D^{2}+2D-1\right)-V_{0}\left(1-D\right)^{2}D^{2}+V_{0}\left(1-D\right)^{4}}{\left(1-D\right)^{2}}\right]-I_{LV3}DT+I_{0}T-I_{LV3}=0$$

$$L_{3} = \frac{1}{2I_{0}f} \left[ \frac{V_{i} \left( D^{2} + 2D - 1 \right) - V_{0} \left( 1 - D \right)^{2} D^{2} + V_{0} \left( 1 - D \right)^{4}}{\left( 1 - D \right)^{2}} \right]$$

(47)

# **3.3.2.** Current equations of Capacitor $C_1$ , during on and off states of the switch are given as follow:

$$I_{C1,1} = I_{L3,1} \tag{48}$$

$$I_{C1,2} = I_{L3,2} + I_{C3,2} - I_{L2,2}$$

(49)

By using charge balance rule for capacitor  $C_1$ , we have:

$$\int_{0}^{T_{off}} (I_{L3,1})dt + \int_{0}^{T_{off}} (I_{C3,2})dt + \int_{0}^{T_{off}} (I_{L3,2})dt - \int_{0}^{T_{off}} (I_{L2,2})dt = 0$$

$$\frac{1}{2L_{3}} \frac{(v_{L1,1} + v_{C1,1} - v_{C3,1})}{L_{3}} D^{2}T^{2}I_{LV3}DT + I_{0}T - \frac{T^{2}}{2L_{3}} (V_{0}(1-D)^{2} - V_{i}) - I_{LV3} + \frac{T^{2}}{2L_{3}} (V_{0}(1-D)^{2} - V_{i}) + I_{LP3}(1-D)T + -I_{LP2}(1-D)T = 0$$

$$\frac{D^2 T^2}{2L_3} \left[ \frac{2V_i - V_0 (1 - D)^2}{(1 - D)^2} \right] + I_{LV3} DT + I_0 T + I_{LP3} (1 - D) T - I_{LV3} - \frac{T^2 V_i D}{2L_3} - I_{LP2} (1 - D) T = 0 (50)$$

By applying boundary conditions to above Eq. and solving for L<sub>2</sub>, yields

$$L_{2} = \frac{1}{\left[\frac{D}{V_{i}L_{3}}\left\{\frac{2V_{i}-V_{0}\left(1-D\right)^{2}}{\left(1-D\right)^{2}D^{2}}\right\} + \frac{2I_{0}f}{DV_{i}}\right]}$$

(51)

### **3.3.3.** Current equations of Capacitor $C_2$ , are given as follow: $I_{C2,1} = I_{L2,1}$

$$I_{C2,2} = I_{L3,2} - I_{L1,2} \tag{53}$$

(52)

By using charge balance rule for capacitor  $C_2$ , we have:

$$\int_{0}^{T_{off}} (I_{L2,1})dt + \int_{0}^{T_{off}} (I_{L2,2})dt - \int_{0}^{T_{off}} (I_{L1,2})dt = 0$$

$$\frac{V_{i}}{(1-D)2L_{2}}D^{2}T^{2} + I_{LV2}DT + \frac{1}{2L_{2}} \Big[ V_{i} - v_{C2,2} + v_{C1,2} \Big] (1-D)^{2}T^{2} + I_{LP2} (1-D)T + \frac{1}{2L_{1}} \Big[ V_{i} - v_{C2,2} \Big] (1-D)^{2}T^{2} - I_{LP1} (1-D)T = 0$$

$$\frac{V_{i}}{(1-D)2L_{2}}D^{2}T^{2} + \frac{T^{2}V_{i}D}{2L_{2}} - \frac{T^{2}V_{i}D}{2L_{1}} (1-D) + I_{LV2}DT + I_{LP2} (1-D)T - I_{LP1} (1-D)T = 0$$

(54)

By applying boundary conditions to the above equation and solving for  $L_1$ , yields

$$L_{1} = L_{2} \left( 1 - D \right)^{2} \tag{55}$$

Therefore, the converter operates in CCM when  $L_1 > L_{C1}$ ,  $L_2 > L_{C2}$ , and  $L_3 > L_{C3}$  while operates in DCM when  $L_1 < L_{C1}$ ,  $L_2 < L_{C2}$  and  $L_3 < L_{C3}$ . At boundary conditions, i.e., when  $L_1 = L_{C1}$ ,  $L_2 = L_{C2}$  and  $L_3 = L_{C3}$  the converter operates at the edge of between CCM and DCM.

#### 3.4. RMS calculation:

For RMS calculation, to simplify the analysis inductor's current and capacitor's voltage ripple is ignored. Average inductor  $L_1$  current can be calculated as:

$$I_{i} = I_{L1,1} = I_{L1,2} = I_{L1} = \frac{I_{0}(1+D)}{(1-D)^{2}}$$

(56)

Average inductor  $L_2$  current can be calculated as:

$$\int_{0}^{T_{off}} (I_{L2,1})dt + \int_{0}^{T_{off}} (I_{L2,2})dt - \int_{0}^{T_{off}} (I_{L1,2})dt = 0$$

$$I_{L2,1}DT + I_{L2,2}(1-D)T - I_{L1,2}(1-D)T = 0$$

$$I_{L2,1} = I_{L2,2} = I_{L2} = I_i(1-D)$$

(57)

Average Capacitorr $C_3$  current at  $t=T_{off}$  can be calculated as:

$$\int_{0}^{T_{off}} (I_{L3,1})dt + \int_{0}^{T_{off}} (I_{C3,2})dt + \int_{0}^{T_{off}} (I_{L3,2})dt - \int_{0}^{T_{off}} (I_{L2,2})dt = 0$$

$$I_{L3,1}DT + \int_{0}^{T_{off}} (I_{C3,2})dt + I_{L3,2}(1-D)T - I_{L2,2}(1-D)T = 0$$

$$\int_{0}^{T_{off}} (I_{C3,2})dt = I_{L2,2}(1-D)T - I_{L3}T$$

$$\int_{0}^{T_{off}} (I_{C3,2})dt = I_{i}(1-D)^{2}T - I_{L3}T$$

$$I_{C3,2} = I_{L2,2} - \frac{I_{L3}}{(1-D)}$$

(59)

Capacitor C<sub>3</sub> current at  $_{t=T_{on}}$  can be written as:

$$I_{C3,1} = -I_{L3,1} = -I_{L3,2} = -I_{L3} = -I_{0}$$

(60)

Average inductor  $L_{3}$  current can be calculated as:

$$\int_{0}^{T_{off}} -(I_{0})dt + \int_{0}^{T_{off}} (I_{L3,2})dt + \int_{0}^{T_{off}} (I_{C3,2})dt + \int_{0}^{T_{off}} -(I_{0})dt = 0$$

$$I_{L3} (1-D) + I_{i} (1-D)^{2} - I_{L3} = I_{0}$$

$$I_{L3} = I_{0}$$

(61)

Capacitor  $C_1$  current at  $t=T_{on}$  can be written as:

$$I_{C1,1} = I_{L3,1} = I_{L3,2} = I_{L3} = I_0$$

(62)

Capacitor C<sub>1</sub> current at  $t=T_{off}$  can be calculated as:

$$I_{C1,2} = I_{L3,2} + I_{C3,2} - I_{L2,2}$$

$$= I_0 D$$

(63)

$$I_{C1,2} = -\frac{I_0 D}{(1 - D)} \tag{64}$$

Capacitor  $C_4$  current at  $t=T_{off}$  can be calculated as:

$$\int_{0}^{T_{off}} (I_{C4,1}) dt + \int_{0}^{T_{off}} (I_{C4,2}) dt = 0$$

$$I_{C4,2} = \frac{I_0 D}{(1-D)}$$

(65)

Capacitor  $C_2$  current at  $_{t=T_{on}}$  can be written as:

$$I_{C2,1} = I_{L2} = I_i \left( 1 - D \right) = \frac{I_0 \left( 1 + D \right)}{\left( 1 - D \right)}$$

(66)

Capacitor  $C_2$  current at  $t=T_{off}$  can be calculated as:

$$I_{C2,2} = I_{L2,2} - I_{L1,2} = I_i (1 - D) - I_i$$

$$I_{C2,2} = -\frac{I_0 (1 + D)D}{(1 - D)^2}$$

(67)

Diodes  $D_1$  and  $D_2$  currents are given as:

$$I_{D1} = I_{D2} = I_i = \frac{I_0 \left(1 + D\right)}{\left(1 - D\right)^2}$$

(68)

Average Diode  $D_1$  current is given as:

$$I_{D1,avg} = I_i = \frac{I_0 (1+D)}{(1-D)^2} D$$

(69)

Average Diode  $D_2$  current is given as:

$$I_{D2,avg} = \frac{I_0 (1+D)}{(1-D)^2} (1-D)$$

(70)

Diode  $D_3$  and  $D_4$  currents are given as:

$$I_{D3} = I_{L2,2} - I_{C3,2} = \frac{I_0}{(1-D)}$$

(71)

$$I_{D4} = I_{L3,2} + I_{C3,2} = \frac{I_0}{(1-D)}$$

(72)

Average Diode  $D_3$  and  $D_4$  currents are given as:  $I_{D3,avg} = I_{D4,avg} = I_0$

Diode's RMS values are calculated as:

$$I_{D1,rms} = \sqrt{\frac{1}{T} \int_{0}^{T_{on}} \left(\frac{I_0(1+D)}{(1-D)^2}\right)^2} dt = \frac{I_0(1+D)}{(1-D)^2} \sqrt{D}$$

(74)

(73)

$$I_{D2,rms} = \sqrt{\frac{1}{T} \int_{0}^{T_{on}} \left(\frac{I_0(1+D)}{(1-D)^2}\right)^2 dt} = \frac{I_0(1+D)}{(1-D)^2} \sqrt{(1-D)}$$

(75)

$$I_{D3,rms} = I_{D4,rms} = \sqrt{\frac{1}{T} \int_{0}^{T_{off}} \left(\frac{I_0}{(1-D)}\right)^2} dt = \frac{I_0}{\sqrt{(1-D)}}$$

(76)

Capacitor's RMS values are calculated as:

$$I_{C1,rms} = \sqrt{\frac{1}{T} \left[ \int_{0}^{T_{on}} \left( -I_{0} \right)^{2} dt + \int_{0}^{T_{off}} \left( \frac{I_{0}D}{(1-D)} \right)^{2} dt \right]} = I_{0} \sqrt{\frac{D}{(1-D)}}$$

(77)

$$I_{C2,rms} = \sqrt{\frac{1}{T} \left[ \int_{0}^{T_{op}} \left( \frac{I_0 \left( 1+D \right) D}{\left( 1-D \right)} \right)^2 dt} + \int_{0}^{T_{off}} \left( \frac{-I_0 \left( 1+D \right) D}{\left( 1-D \right)^2} \right)^2 dt} \right] = \frac{I_0 \left( 1+D \right)}{\left( 1-D \right)^2} \sqrt{D \left( 1-D \right)}$$

(78)

$$I_{C3,rms} = \sqrt{\frac{1}{T} \left[ \int_{0}^{T_{on}} \left( -I_{0} \right)^{2} dt + \int_{0}^{T_{off}} \left( \frac{I_{0}D}{(1-D)} \right)^{2} dt \right]} = I_{0} \sqrt{\frac{D}{(1-D)}}$$

(79)

$$I_{C4,rms} = \sqrt{\frac{1}{T}} \left[ \int_{0}^{T_{on}} \left( -I_{0} \right)^{2} dt + \int_{0}^{T_{off}} \left( \frac{I_{0}D}{(1-D)} \right)^{2} dt \right] = I_{0} \sqrt{\frac{D}{(1-D)}}$$

(80)

#### 3.5. Efficiency analysis:

For efficiency analysis, parasitic resistances of inductors, capacitors, diodes, and switches are taken into consideration. The parasitic on-state resistance of Mosfet is represented by  $r_s$ . Parasitic resistances of inductors and capacitors are represented by  $(r_{L1}, r_{L2}, r_{L3})$  and  $(r_{C1}, r_{C2}, r_{C3})$ , respectively. Forward voltage and parasitic resistances of diodes is represented by  $V_F$  and  $(r_{D1}, r_{D2}, r_{D3}, r_{D4})$ , respectively.

Losses due to inductors are calculated as:

$$P_{L,loss} = I_{L1}^{2} r_{L1} + I_{L2}^{2} r_{L2} + I_{L3}^{2} r_{L3}$$

(81)

Losses due to capacitors are calculated as:

$$P_{C,loss} = I_{C1,rms}^{2} r_{C1} + I_{C2,rms}^{2} r_{C3} + I_{C3,rms}^{2} r_{C3} + I_{C4,rms}^{2} r_{C4}$$

(82)

Losses due to diodes are calculated as:

$$P_{D1,loss} = I_{D1,rms}^{2} r_{D1} + V_F I_{D1,avg}$$

(83)

$$P_{D2,loss} = I_{D2,rms}^{2} r_{D2} + V_F I_{D2,avg}$$

(84)

$$P_{D3,loss} = I_{D3,rms}^{2} r_{D3} + V_F I_{D3,avg}$$

(85)

$$P_{D4,loss} = I_{D4,rms}^{2} r_{D4} + V_{F} I_{D4,avg}$$

(86)

$$P_{D,loss} = P_{D1,loss} + P_{D2,loss} + P_{D3,loss} + P_{D4,loss}$$

(87)

Switch current is obtained as:

$$I_{S} = I_{L1} + I_{L2} = \frac{I_{0}(1+D)}{(1-D)^{2}} + \frac{I_{0}(1+D)}{(1-D)} = \frac{I_{0}(1+D)(2-D)}{(1-D)^{2}}$$

(88)

The RMS switch current is given as:

$$I_{s,rms} = \sqrt{\frac{1}{T} \int_{0}^{T_{out}} \left(\frac{I_0(1+D)}{(1-D)^2}\right)^2 dt} = \frac{I_0(1+D)(2-D)}{(1-D)^2} \sqrt{D}$$

(89)

The average switch current is given as:

$$I_{S,avg} = \frac{I_0 (1+D)(2-D)}{(1-D)^2} D$$

(90)

Switch voltage is obtained as:

$$V_{S} = v_{L1,2} + v_{C1,2} + v_{C2,2} = V_{i} - v_{C2,1} + v_{C1,2} + v_{C2,2}$$

$$V_{i} = (2D_{i} - D_{i}^{2})$$

(91)

$$V_{S} = V_{i} + \frac{V_{i}(2D - D^{2})}{(1 - D)^{2}} = \frac{V_{i}}{(1 - D)^{2}}$$

(92)

Switch conduction loss is earned as:

$$P_{S,loss} = I_{S,rms}^2 r_S \tag{93}$$

Switching loss is calculated as: 1(t + t)

$$P_{Switch} = \frac{1}{2} \frac{(t_r + t_f)}{T} I_{S,avg} V_S + \frac{1}{2} \frac{C_{oss}}{T} V_S^2$$

(94)

$$P_{Loss} = P_{L,loss} + P_{C,loss} + P_{D,loss} + P_{S,loss} + P_{Switch}$$

$$\tag{95}$$

Output power is given as:

$$P_{out} = I_0^2 R \tag{96}$$

$$\eta\% = \frac{P_{out}}{P_{out} + P_{Loss}} \times 100$$

(97)

## CHAPTER 4 RESULTS AND DISCUSSION

#### 4.1 Comparison Analysis with recent converters