## Development of Nonlinear Optimization Techniques Based PID Controller for SEPIC Converter

by

Mirza Muntasir Nishat

A thesis submitted to the board of examiners in partial fulfilment of the requirements for the degree of

### Master of Science in Electrical and Electronic Engineering

Department of Electrical and Electronic Engineering

Islamic University of Technology (IUT) The Organization of Islamic Cooperation (OIC) Board Bazar, Gazipur-1704, Bangladesh

August 2019

### **CERTIFICATE OF APPROVAL**

The thesis titled "Development of Nonlinear Optimization Techniques Based PID Controller for SEPIC Converter" submitted by Mirza Muntasir Nishat bearing Student No. 161021009 of Academic Year 2016-2017 has been found as satisfactory and accepted as partial fulfilment of the requirement for the degree of Master of Science in Electrical and Electronic Engineering on 5<sup>th</sup> August, 2019.

#### **Board of Examiners**

Dr. Md. Ashraful Hoque Professor Department of EEE, IUT, Board Bazar, Gazipur-1704 Chairman (Supervisor)

05/08/2019

Dr. Md. Ruhul Amin Professor and Head Department of EEE, IUT, Board Bazar, Gazipur-1704

Member (Ex - officio)

Mul 5.8.19

Dr. Ashik Ahmed Associate Professor Department of EEE, IUT, Board Bazar, Gazipur-1704

ABATA

Dr. Md. Monirul Kabir Professor Department of EEE, DUET, Gazipur

Member (External)

Member

### **DECLARATION OF CANDIDATE**

It is hereby declared that this thesis or any part of it has not been submitted elsewhere for the award of any degree or diploma.

(Signature of the Supervisor) **Dr. Md. Ashraful Hoque** Professor Department of EEE Islamic University of Technology Board Bazar, Gazipur-1704 Bangladesh

(Signature of Candidate) Mirza Muntasir Nishat Student ID: 161021009 Academic Year: 2016-2017

## **DEDICATION**

I would like to dedicate this thesis to my family who supported me through both good and tough times. They always give me the motivation to move forward in my life.

## **ACKNOLEDGMENTS**

First, I thank Allah from the bottom of my heart as He enabled me and strengthen me to conduct this research properly and complete my thesis. Foremost, I am highly grateful to my respected supervisor, *Prof. Dr. Md. Ashraful Hoque*, Professor, Department of EEE, IUT for his guidance and support for this thesis. Without his bolstering influence as well as buttress to move on, I would not be intrigued, let alone to work in this area of science. He truly inspires me to be a genuine scientist and conduct research in a proper constructive way.

I am ever grateful to *Mr. Fahim Faisal* for his sincere effort in this research work. He sacrificed his valuable time for continuously guiding and motivating me for completing the thesis. He is currently working as a Lecturer in the department of EEE, IUT. I genuinely believe this thesis would not be completed without his mentoring and continuous rigorous support. He not only gave motivation in times of stress but also made me follow very well-constructed steps to complete my thesis.

I would like to express my heartfelt gratitude to *Prof. Dr. Ruhul Amin*, Head, Dept. of EEE, IUT; *Assoc. Prof. Dr. Ashik Ahmed*, Dept. of EEE, IUT and *Prof. Dr. Md. Monirul Kabir*, Dept. of EEE, DUET for serving in my committee and imparting their valuable knowledge to complete this thesis work.

I would like to thank all the faculty members of EEE Dept., IUT for their continuous support and encouragement. They provided a friendly environment for me to learn and grow.

Finally, my deepest of gratitude goes to my family who always listened to my sufferings and enchanted me with their delightful words. Last but not the least I would like to thank my friends who always supported me through this journey.

### **ABSTRACT**

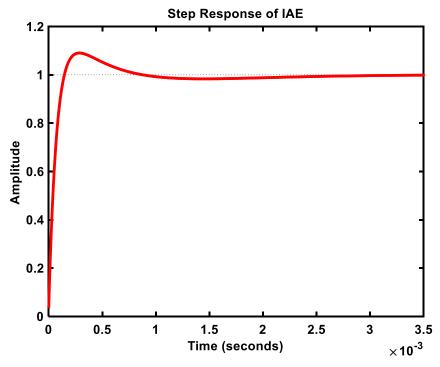

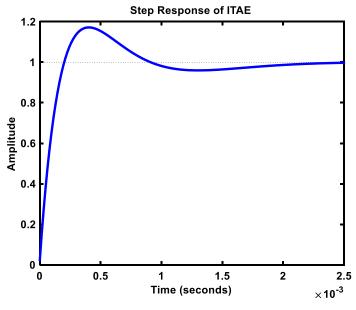

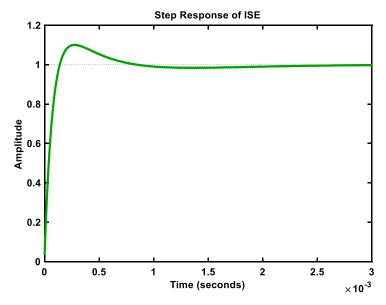

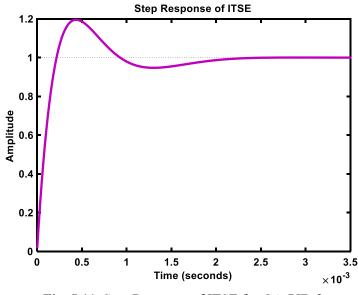

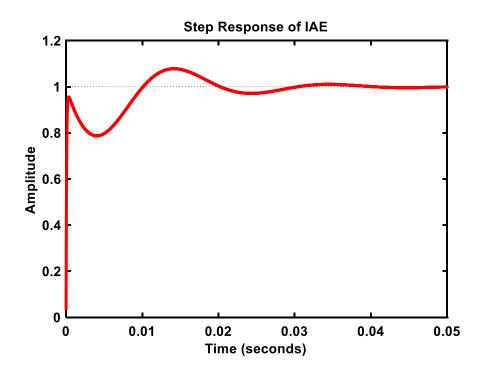

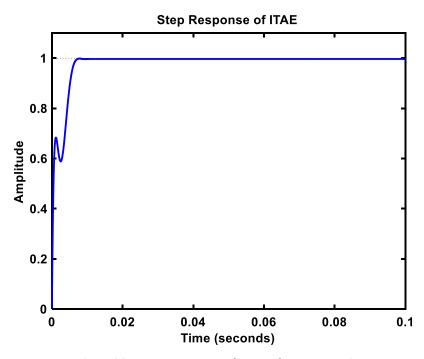

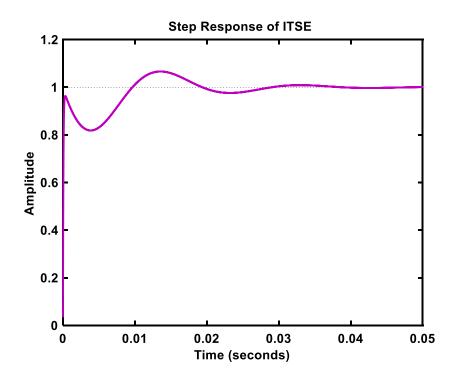

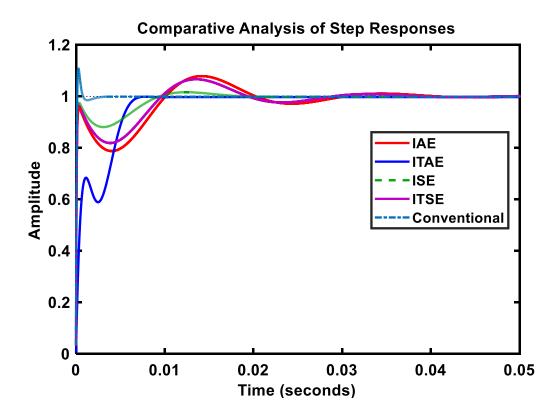

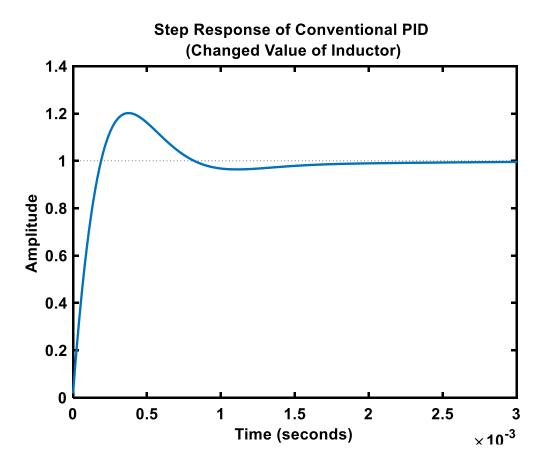

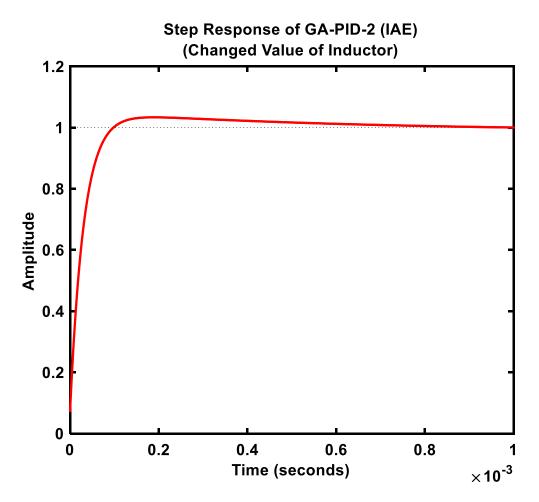

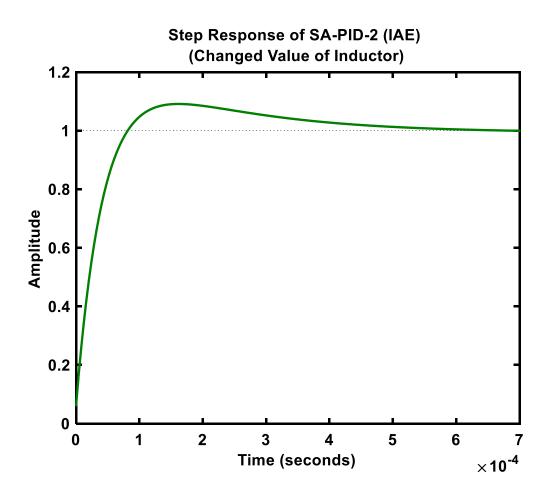

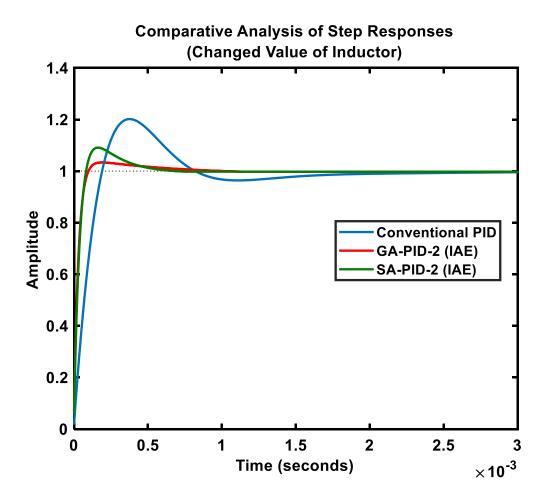

This thesis presents an investigation on closed loop stability of SEPIC (Single-Ended Primary Inductor Converter) converter by employing an optimized PID controller where the parameters are tuned by Genetic Algorithm (GA) and Simulated Annealing (SA) algorithm. Genetic Algorithm is a stochastic algorithm inspired by natural evolution and is extensively used as an optimization technique in power electronics in recent years. SA refers to an optimization technique, based on the principles of thermodynamics where the analogy of cooling of metal and freezing into a minimum energy level is utilized. Here, State Space Average method is deployed to model and obtain the transfer function of the converter based system. Hence, GA and SA based PID controller is studied and implemented in the system so that the stability of the converter can be evaluated and compared with the conventional PID controller. Different fitness functions (IAE, ITAE, ISE, ITSE) and performance parameters like percentage of overshoot, rise time, settling time and peak amplitude are taken into account to investigate the stability of the system. The step responses of the closed loop system are obtained through rigorous simulation in MATLAB. It is observed that, GA-PID-2 (IAE) is the most optimized controller among the entire GA based PID controllers as the overshoot is the lowest (3.43%) and peak amplitude is 1.03. Moreover, rise time (0.000102s) and settling time (0.00418s) are also in acceptable limit. However, GA-PID-2 (ISE) shows quick rise (0.000102s) and settling time (0.000676s) but the overshoot of ISE is 11.3% which is much greater than IAE of GA-PID-2. Meanwhile, SA-PID-2 (IAE) is the most optimized controller among all other SA based controllers where the value of overshoot is 2.2% and peak amplitude is 1.01. For Rise time and settling time, the values for SA-PID-2 (IAE) are 0.000665s and 0.000104s respectively which are in acceptable limit. Though SA-PID-3 (IAE) shows quick rise time (0.000118s), the overshoot is high (22.2%). Therefore, SA-PID-2 (IAE) is selected as the most optimized and suitable controller for SEPIC converter. For changed value of inductor, the simulation is done for GA-PID-2 (for IAE) and SA-PID-2 (for IAE), it is observed that less overshoot is obtained than conventional PID controller (overshoot 17.3%). For GA-PID-2, the overshoot is 3.36% and for SA-PID-2 the value is 9.12%. So, it is evident that, nonlinear optimization technique based PID controller is providing more optimized result in case of any change in the value of inductor of the circuit than conventional PID controller. However, GA is more suitable option than SA in terms of designing the controller for less overshoot. Therefore, GA-PID-2 (IAE) is the most optimized controller for SEPIC converter in this investigative study.

# TABLE OF CONTENTS

### Page No.

| Certificate of Approval | i     |

|-------------------------|-------|

| Declaration             | ii    |

| Dedication              | iii   |

| Acknowledgements        | iv    |

| Abstract                | V     |

| Table of Contents       | vi    |

| List of Tables          | xi    |

| List of Figures         | xiii  |

| List of Acronyms        | xviii |

| CHAPTER-1 | INTRODUCTION AND BACKGROUND STUDY | 1 |

|-----------|-----------------------------------|---|

| 1.1       | Introduction                      | 1 |

| 1.2       | Literature Review                 | 2 |

| 1.3       | Statement of the Problem          | 5 |

| 1.4       | Thesis Objectives                 | 5 |

| 1.5       | Thesis Organization               | 6 |

| CHAPTER-2 | 2 ]      | DC-DC (     | CONVERTERS             | 7  |

|-----------|----------|-------------|------------------------|----|

| 2.1       | Working  | g Principle | e of a DC-DC Converter | 8  |

| 2.2       | Analysis | s of conve  | rter waveforms         | 10 |

| 2.3       | Converte | er circuit  | topologies             | 14 |

|           | 2.3.1.   | Non-isol    | ated Converters        | 14 |

|           |          | 2.3.1.1     | Buck converter         | 14 |

|           |          | 2.3.1.2     | Boost converter        | 15 |

|           |          | 2.3.1.3     | Buck-boost converter   | 16 |

|           |          | 2.3.1.4     | Cuk converter          | 17 |

|           |          | 2.3.1.5     | SEPIC converter        | 18 |

| CHAPTER-3 | <b>STUDY OF DC-DC SEPIC CONVERTER</b>    | 19 |

|-----------|------------------------------------------|----|

| 3.1       | Conventional SEPIC Converter             | 20 |

| 3.2       | State Space Modelling                    | 21 |

| 3.3       | Design of DC-DC SPEIC Converter          | 27 |

| 3.4       | Gain Equation of SEPIC Converter         | 28 |

| 3.5       | Response of Average Model                | 30 |

| 3.6       | Closed Loop Analysis with PID controller | 32 |

|           |                                          |    |

### CHAPTER-4 IMPLEMENTATION OF NONLINEAR OPTIMIZATION 35 TECHNIQUE BASED PID CONTROLLER FOR SEPIC CONVERTER

| 4.1 | Overview | w of Nonlinear optimization Technique  | 35 |

|-----|----------|----------------------------------------|----|

| 4.2 | Introduc | tion to Genetic Algorithm              | 35 |

|     | 4.2.1    | What is Genetic Algorithm              | 36 |

|     | 4.2.2    | Characteristics of Genetic Algorithm   | 36 |

|     | 4.2.3    | Population Size                        | 37 |

|     | 4.2.4    | Reproduction                           | 37 |

|     | 4.2.5    | Crossover                              | 38 |

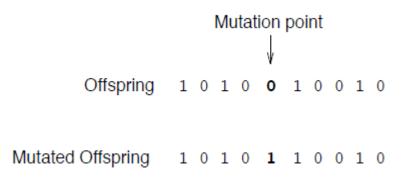

|     | 4.2.6    | Mutation                               | 41 |

|     | 4.2.7    | Elitism                                | 41 |

|     | 4.2.8    | Convergence                            | 42 |

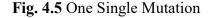

|     | 4.2.9    | Flowchart of Genetic Algorithm         | 42 |

|     | 4.2.10   | Objective Function of Fitness Function | 44 |

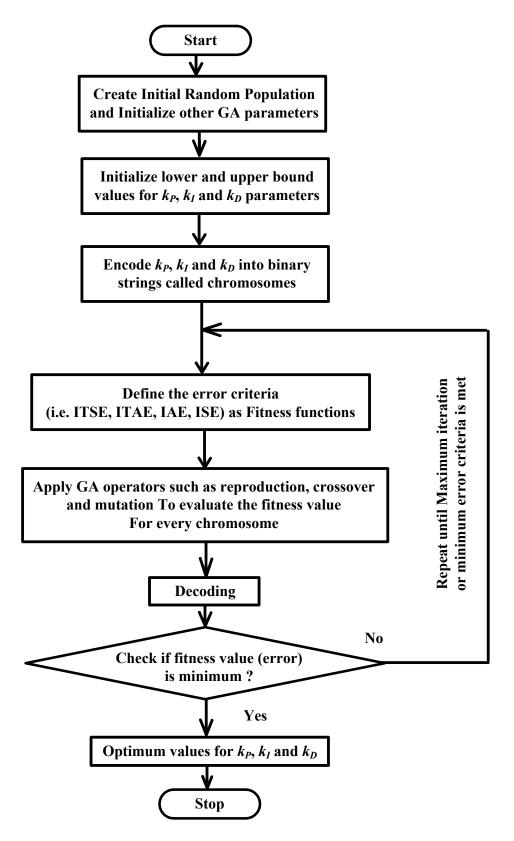

|     | 4.2.11   | Design of GA based PID Controller      | 45 |

|     | 4.2.12   | Comparison with other techniques       | 45 |

|     | 4.2.13   | Summary                                | 47 |

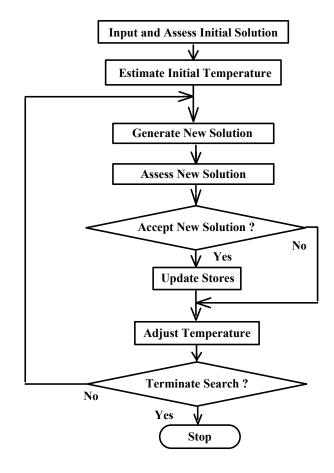

| 4.3 | Simulate | ed Annealing Algorithm                 | 48 |

|     | 4.3.1    | Overview of SA                         | 48 |

|     | 4.3.2    | Methodology                            | 49 |

| 4.3.3 | Strengths and Weaknesses                       |    |  |  |

|-------|------------------------------------------------|----|--|--|

| 4.3.4 | Comparison with other methods                  | 51 |  |  |

| 4.3.5 | Suitability                                    | 53 |  |  |

| 4.3.6 | Practical Implementation                       | 53 |  |  |

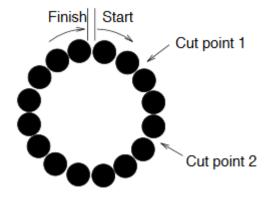

|       | 4.3.6.1 Solution Representation and Generation | 53 |  |  |

|       | 4.3.6.2 Solution Evaluation                    | 55 |  |  |

|       | 4.3.6.3 Annealing Schedule                     | 56 |  |  |

| 4.3.7 | Design of SA based PID Controller              | 58 |  |  |

| 4.3.8 | Summary                                        | 59 |  |  |

| CHAPTER | 5        | SIMULAT    | ION RESULTS AND PERFORMANCE ANALYSIS | 60 |

|---------|----------|------------|--------------------------------------|----|

| 5.1     | Performa | ance Parai | meters                               | 60 |

| 5.2     | Open loo | op and Clo | osed Loop Responses                  | 61 |

| 5.3     | GA base  | d PID Co   | ntroller                             | 64 |

|         | 5.3.1    | GA-PID-    | -1                                   | 64 |

|         |          | 5.3.1.1    | GA-PID-1 Simulation Results          | 65 |

|         | 5.3.2    | GA-PID-    | -2                                   | 68 |

|         |          | 5.3.2.1    | GA-PID-2 Simulation Results          | 69 |

|         | 5.3.3    | GA-PID-    | -3                                   | 72 |

|         |          | 5.3.3.1    | GA-PID-3 Simulation Results          | 73 |

| 5.4     | Graphica | al Analysi | s of GA based PID Controller         | 76 |

| 5.5     | SA based PID Controller                                 |     |

|---------|---------------------------------------------------------|-----|

|         | 5.5.1 SA-PID-1                                          | 80  |

|         | 5.5.1.1 SA-PID-1 Simulation Results                     | 80  |

|         | 5.5.2 SA-PID-2                                          | 85  |

|         | 5.5.2.1 SA-PID-2 Simulation Results                     | 86  |

|         | 5.5.3 SA-PID-3                                          | 90  |

|         | 5.5.3.1 SA-PID-3 Simulation Results                     | 90  |

| 5.6     | Graphical Analysis of SA based PID Controller           | 95  |

| 5.7     | Transfer Function and Pole-Zero Mapping                 | 97  |

|         | 5.7.1 GA based Controller                               | 98  |

|         | 5.7.2 SA based Controller                               | 103 |

| 5.8     | Overall Comparative Analysis                            | 108 |

| 5.9     | Effect of Parameter Change on Performance of controller | 109 |

|         |                                                         |     |

| СНАРТЕР | R-6 CONCLUSION                                          | 113 |

| 6.1     | Synopsis                                                | 113 |

#### REFERENCES

6.2

Future Work

115

114

## **LIST OF TABLES**

| No.  | Title                                                                | Page No. |

|------|----------------------------------------------------------------------|----------|

| 3.1  | Parameters used for SEPIC Converter                                  | 28       |

| 3.2  | Different Response for different controllers                         | 33       |

| 3.3  | Effect of PID controller on SEPIC Converter                          | 34       |

| 5.1  | SEPIC Converter Parameters                                           | 61       |

| 5.2  | Performance Analysis for both open loop and close loop block diagram | 63       |

| 5.3  | Parameters of Genetic Algorithm for GA-PID-1                         | 64       |

| 5.4  | Gain Values for GA-PID-1                                             | 65       |

| 5.5  | Evaluation of Performance Parameters for GA-PID-1                    | 68       |

| 5.6  | Parameters of Genetic Algorithm for GA-PID-2                         | 68       |

| 5.7  | Gain Values for GA-PID-2                                             | 69       |

| 5.8  | Evaluation of Performance Parameters for GA-PID-2                    | 72       |

| 5.9  | Parameters of Genetic Algorithm for GA-PID-3                         | 72       |

| 5.10 | Gain Values for GA-PID-3                                             | 73       |

| 5.11 | Evaluation of Performance Parameters for GA-PID-3                    | 76       |

| 5.12 | Parameters of Simulated Annealing Algorithm for SA-PID-1             | 80       |

| 5.13 | Gain Values for SA-PID-1                                             | 80       |

| 5.14 | Evaluation of Performance Parameters for SA-PID-1                    | 85       |

| No.  | Title                                                                   | Page No. |

|------|-------------------------------------------------------------------------|----------|

| 5.15 | Parameters of Simulated Annealing Algorithm for SA-PID-2                | 85       |

| 5.16 | Gain Values for SA-PID-2                                                | 86       |

| 5.17 | Evaluation of Performance Parameters for SA-PID-2                       | 89       |

| 5.18 | Parameters of Simulated Annealing Algorithm for SA-PID-3                | 90       |

| 5.19 | Gain Values for SA-PID-3                                                | 90       |

| 5.20 | Evaluation of Performance Parameters for SA-PID-3                       | 94       |

| 5.21 | Transfer Functions for all GA based PID controllers                     | 98       |

| 5.22 | Values of pole and zero for all GA based PID controllers                | 102      |

| 5.23 | Transfer Functions for all SA based PID controllers                     | 103      |

| 5.24 | Values of pole and zero for all SA based PID controllers                | 107      |

| 5.25 | Evaluation of Performance Parameters for GA and SA based PID controller | 108      |

## **LIST OF FIGURES**

| No.  | Title                                                                                                                                                                                                                     | Page No. |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1  | The buck converter consists of a switch network that<br>reduces the dc component of voltage, and a low pass<br>filter that removes the high-frequency switching<br>harmonics: (a) schematic, (b) switch voltage waveform. | 8        |

| 2.2  | Buck converter dc output voltage $V_0$ vs. duty cycle D                                                                                                                                                                   | 9        |

| 2.3  | A non-ideal boost converter: (a) schematic, (b) inductor voltage and capacitor current waveforms                                                                                                                          | 11       |

| 2.4  | Output voltage vs. duty cycle, for the non-ideal boost converter of Fig. 2.3                                                                                                                                              | 12       |

| 2.5  | Efficiency vs. duty cycle, for the non-ideal boost converter of Fig. 2.3                                                                                                                                                  | 13       |

| 2.6  | Buck converter                                                                                                                                                                                                            | 14       |

| 2.7  | Voltage gain versus duty cycle of buck converter                                                                                                                                                                          | 15       |

| 2.8  | Boost converter                                                                                                                                                                                                           | 15       |

| 2.9  | Voltage gain versus duty cycle of boost converter                                                                                                                                                                         | 15       |

| 2.10 | Buck-boost converter                                                                                                                                                                                                      | 16       |

| 2.11 | Voltage gain versus duty cycle of buck-boost converter                                                                                                                                                                    | 16       |

| 2.12 | Cuk converter                                                                                                                                                                                                             | 17       |

| 2.13 | Voltage gain versus duty cycle of cuk converter                                                                                                                                                                           | 17       |

| 2.14 | SEPIC converter                                                                                                                                                                                                           | 18       |

| 2.15 | Voltage gain versus duty cycle of SEPIC converter                                                                                                                                                                         | 18       |

| No.  | Title                                                                                      | Page No. |

|------|--------------------------------------------------------------------------------------------|----------|

| 3.1  | Conventional SEPIC Converter                                                               | 20       |

| 3.2  | Modes of operation of the conventional SEPIC converter<br>(a) Switch ON and (b) Switch OFF | 21       |

| 3.3  | SEPIC Converter                                                                            | 21       |

| 3.4  | Modes of operation for the SEPIC converter (a) case A and (b) case B                       | 22       |

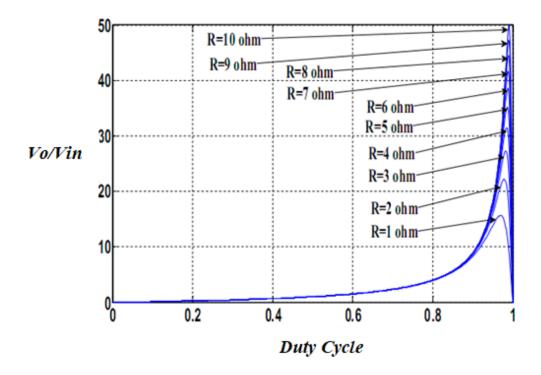

| 3.5  | Voltage Gain vs. duty cycle with variable load                                             | 29       |

| 3.6  | Voltage gain vs. duty cycle with variable load                                             | 30       |

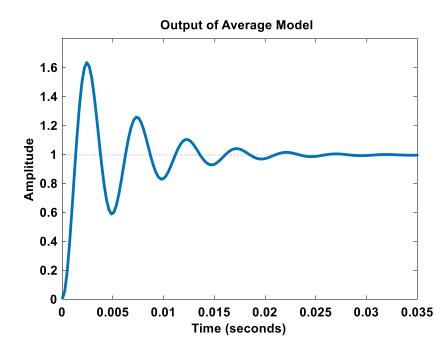

| 3.7  | Voltage amplitude Vs. Time for output of average model                                     | 31       |

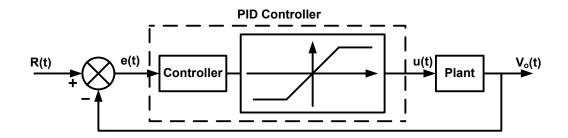

| 3.8  | Typical PID controller structure                                                           | 32       |

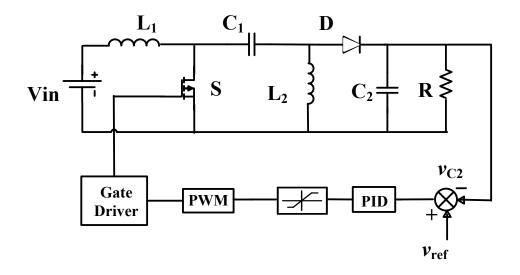

| 3.9  | Proposed SEPIC Converter with PID Controller                                               | 33       |

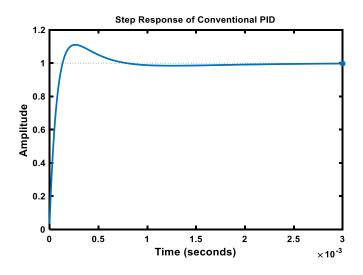

| 3.10 | Step Response of Conventional PID Controller                                               | 34       |

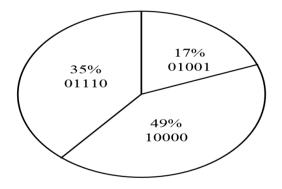

| 4.1  | Depiction of roulette wheel selection                                                      | 38       |

| 4.2  | Single Point Crossover                                                                     | 39       |

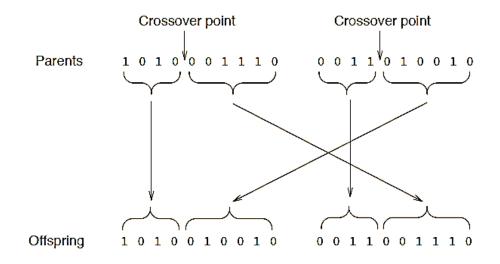

| 4.3  | Multi Point Crossover                                                                      | 40       |

| 4.4  | Uniform Crossover                                                                          | 40       |

| 4.5  | One Single Mutation                                                                        | 41       |

| 4.6  | Flow Chart of Genetic Algorithm                                                            | 43       |

| 4.7  | Basic Block Diagram of Genetic Algorithm (GA) based PID Controller                         | 45       |

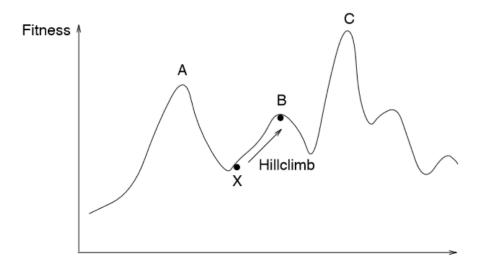

| 4.8  | The Hill climbing Problem                                                                  | 46       |

| 4.9  | Flow Chart of Simulated Annealing (SA) algorithm                                           | 48       |

| No.  | Title                                               | Page No. |

|------|-----------------------------------------------------|----------|

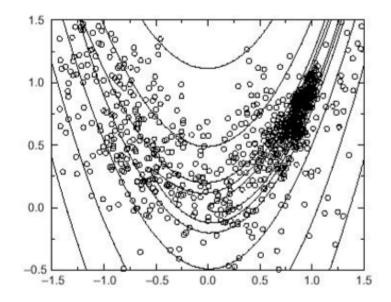

| 4.10 | Progress of search pattern for Rosenbrock function  | 49       |

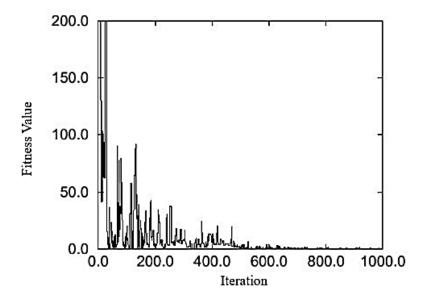

| 4.11 | Objective function reduction                        | 50       |

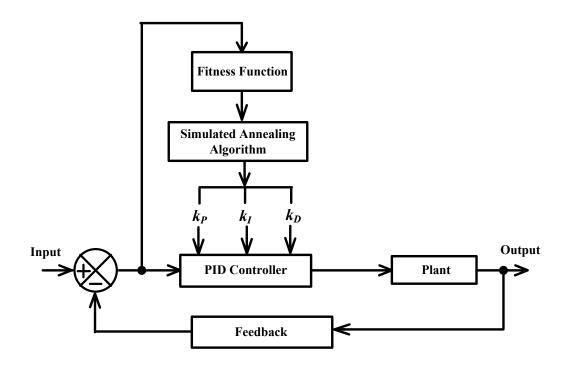

| 4.12 | Basic Block Diagram of SA based PID Controller      | 59       |

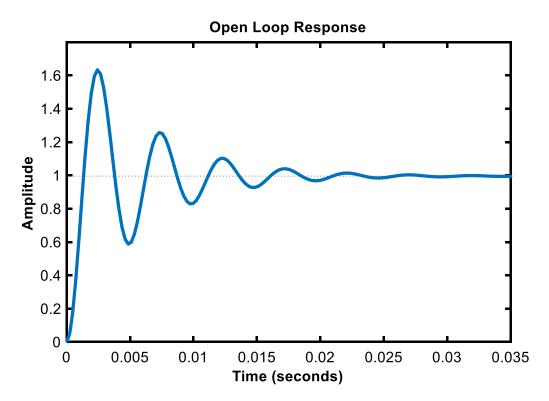

| 5.1  | Voltage amplitude Vs. Time for output of open loop  | 62       |

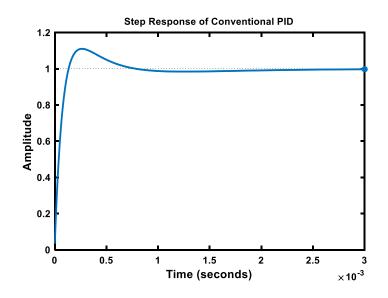

| 5.2  | Step Response of Conventional PID Controller        | 63       |

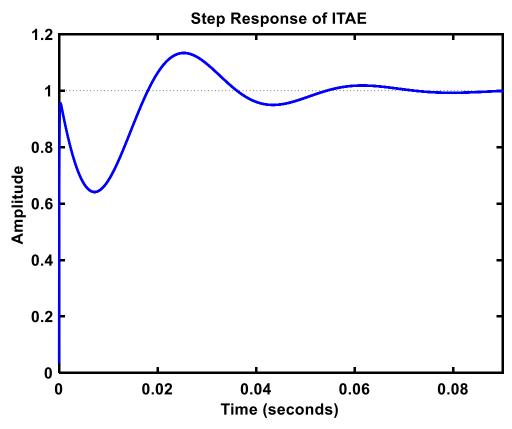

| 5.3  | Step Response of IAE for GA-PID-1                   | 65       |

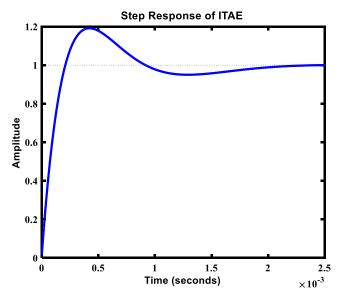

| 5.4  | Step Response of ITAE for GA-PID-1                  | 66       |

| 5.5  | Step Response of ISE for GA-PID-1                   | 66       |

| 5.6  | Step Response of ITSE for GA-PID-1                  | 67       |

| 5.7  | Comparative Analysis of step responses for GA-PID-1 | 67       |

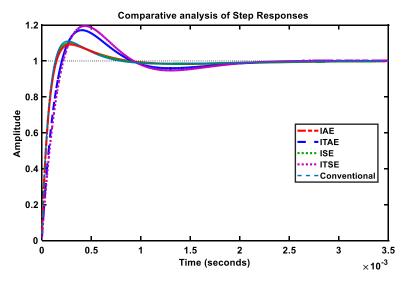

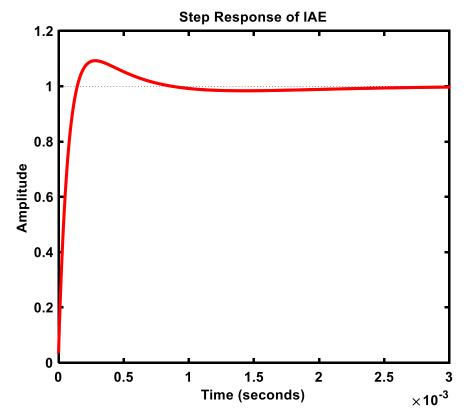

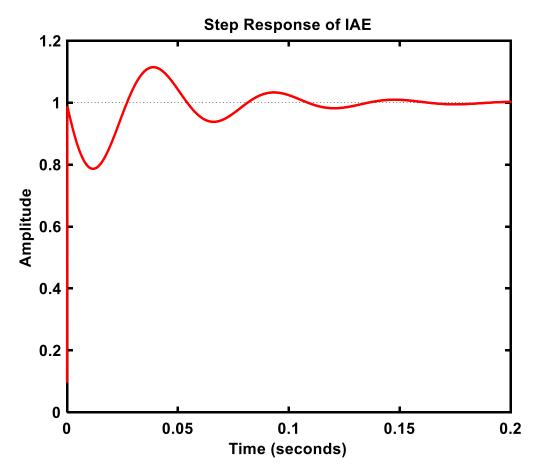

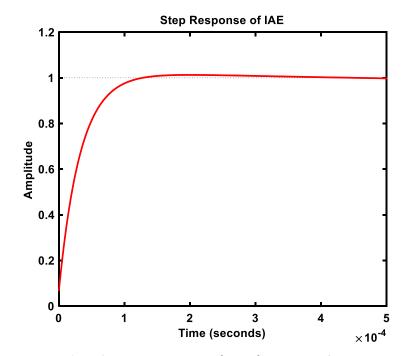

| 5.8  | Step Response of IAE for GA-PID-2                   | 69       |

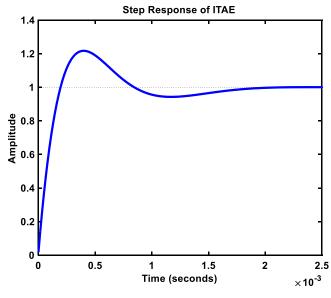

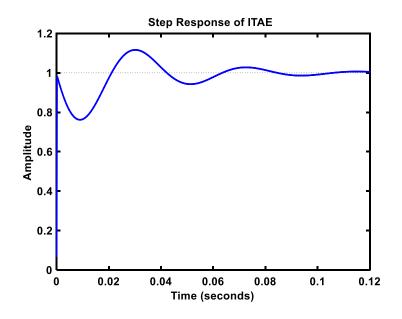

| 5.9  | Step Response of ITAE for GA-PID-2                  | 70       |

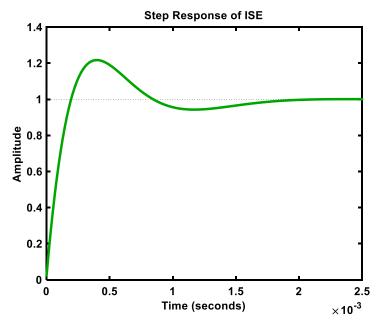

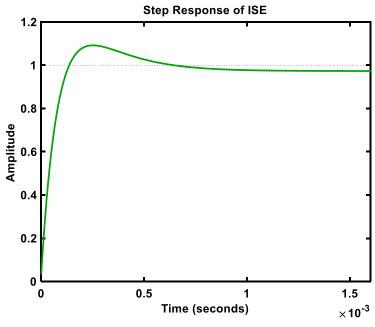

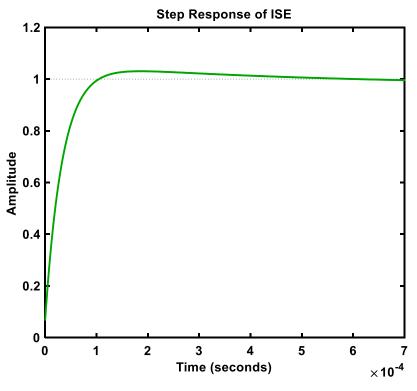

| 5.10 | Step Response of ISE for GA-PID-2                   | 70       |

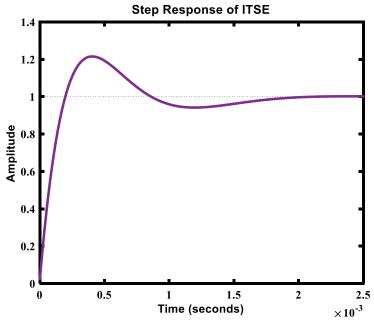

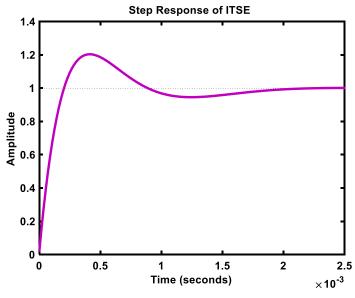

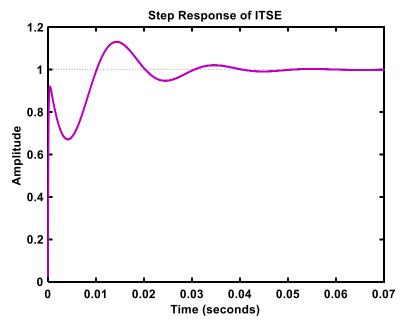

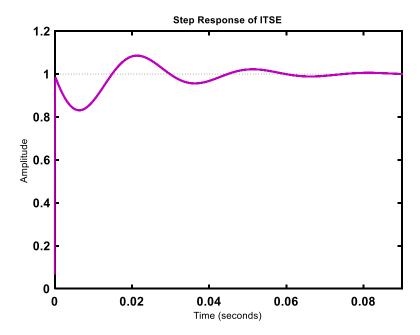

| 5.11 | Step Response of ITSE for GA-PID-2                  | 71       |

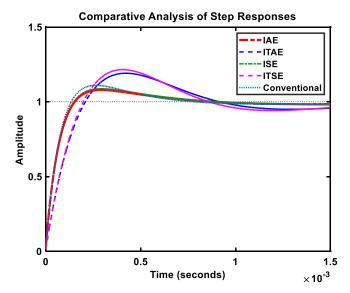

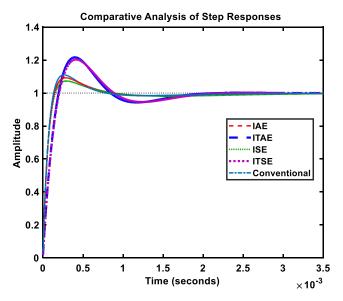

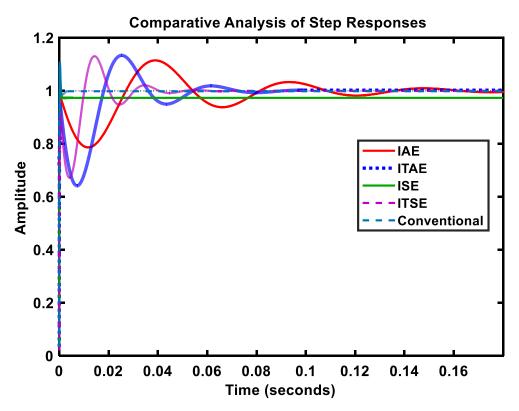

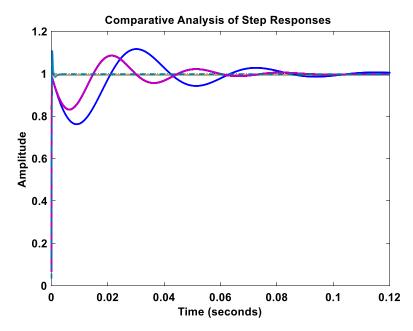

| 5.12 | Comparative Analysis of step responses for GA-PID-2 | 71       |

| 5.13 | Step Response of IAE for GA-PID-3                   | 73       |

| 5.14 | Step Response of ITAE for GA-PID-3                  | 74       |

| 5.15 | Step Response of ISE for GA-PID-3                   | 74       |

| 5.16 | Step Response of ITSE for GA-PID-3                  | 75       |

| No.  | Title                                                                                  | Page No. |

|------|----------------------------------------------------------------------------------------|----------|

| 5.17 | Comparative Analysis of step responses for GA-PID-3                                    | 75       |

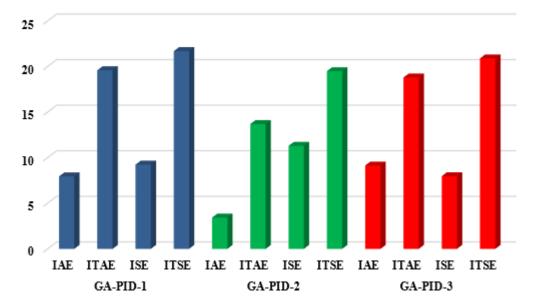

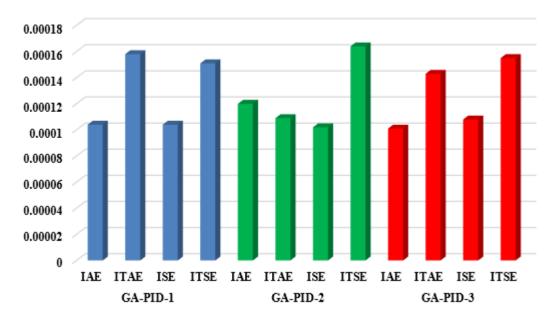

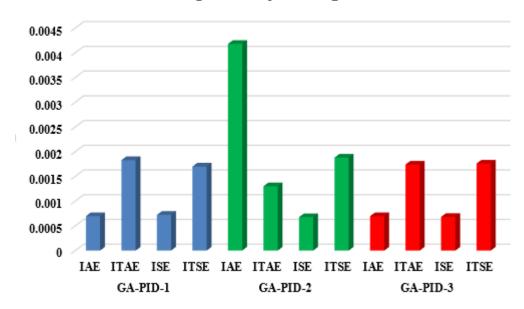

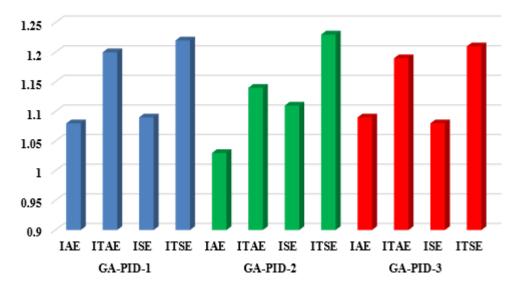

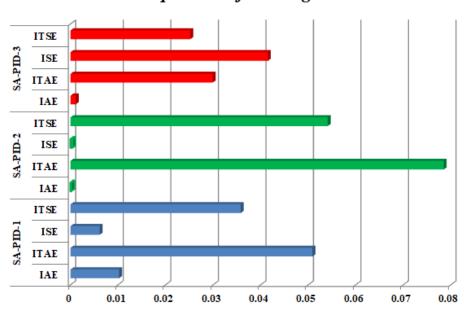

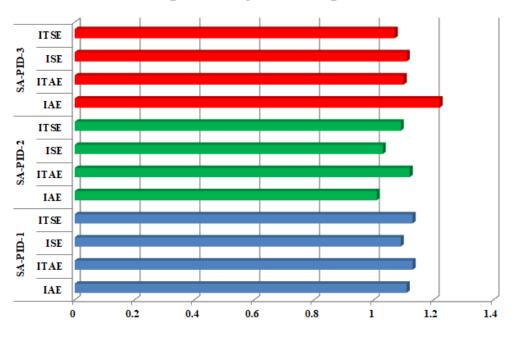

| 5.18 | Comparative Analysis of percentage of overshoot (%OS) for all GA based PID controllers | 77       |

| 5.19 | Comparative Analysis of rise time (Tr) for all GA based PID controllers                | 77       |

| 5.20 | Comparative Analysis of settling time (Ts) for all GA based PID controllers            | 78       |

| 5.21 | Comparative Analysis of peak amplitude for all GA based PID controllers                | 79       |

| 5.22 | Step Response of IAE for SA-PID-1                                                      | 81       |

| 5.23 | Step Response of ITAE for SA-PID-1                                                     | 82       |

| 5.24 | Step Response of ISE for SA-PID-1                                                      | 83       |

| 5.25 | Step Response of ITSE for SA-PID-1                                                     | 83       |

| 5.26 | Comparative Analysis of step responses for SA-PID-1                                    | 84       |

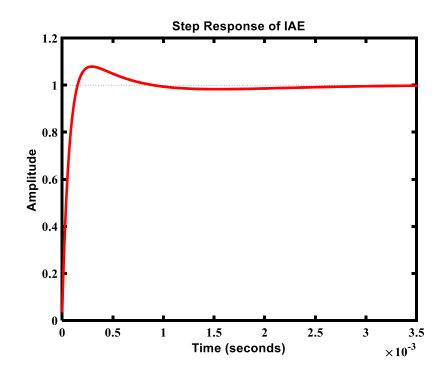

| 5.27 | Step Response of IAE for SA-PID-2                                                      | 86       |

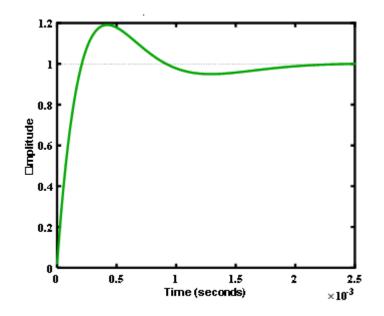

| 5.28 | Step Response of ITAE for SA-PID-2                                                     | 87       |

| 5.29 | Step Response of ISE for SA-PID-2                                                      | 88       |

| 5.30 | Step Response of ITSE for SA-PID-2                                                     | 88       |

| 5.31 | Comparative Analysis of step responses for SA-PID-2                                    | 89       |

| 5.32 | Step Response of IAE for SA-PID-3                                                      | 91       |

| 5.33 | Step Response of ITAE for SA-PID-3                                                     | 91       |

| 5.34 | Step Response of ISE for SA-PID-3                                                      | 92       |

| 5.35 | Step Response of ITSE for SA-PID-3                                                     | 93       |

| No.  | Title                                                                                                                                            | Page No. |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.36 | Comparative Analysis of step responses for SA-PID-3                                                                                              | 94       |

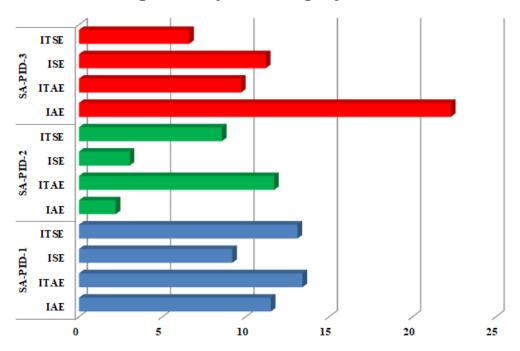

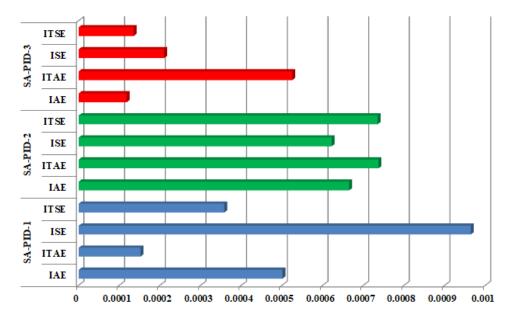

| 5.37 | Comparative Analysis of percentage of overshoot (%OS) for all SA based PID controllers                                                           | 95       |

| 5.38 | Comparative Analysis of rise time (Tr) for all SA based PID controllers                                                                          | 96       |

| 5.39 | Comparative Analysis of settling time (Ts) for all SA based PID controllers                                                                      | 96       |

| 5.40 | Comparative Analysis of peak amplitude for all SA based PID controllers                                                                          | 97       |

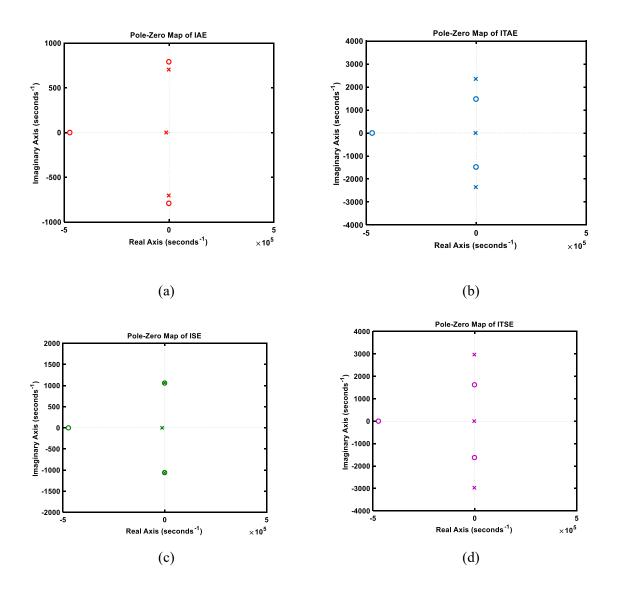

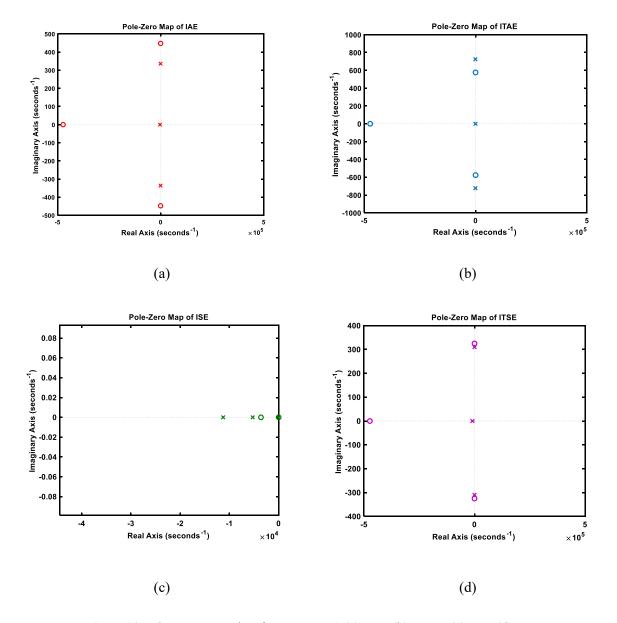

| 5.41 | Pole Zero Mapping for (a) IAE (b) ITAE (c) ISE (d) ITSE of GA-PID-1                                                                              | 99       |

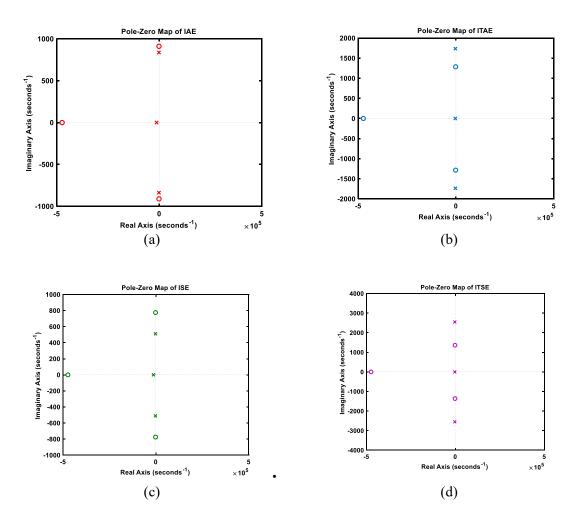

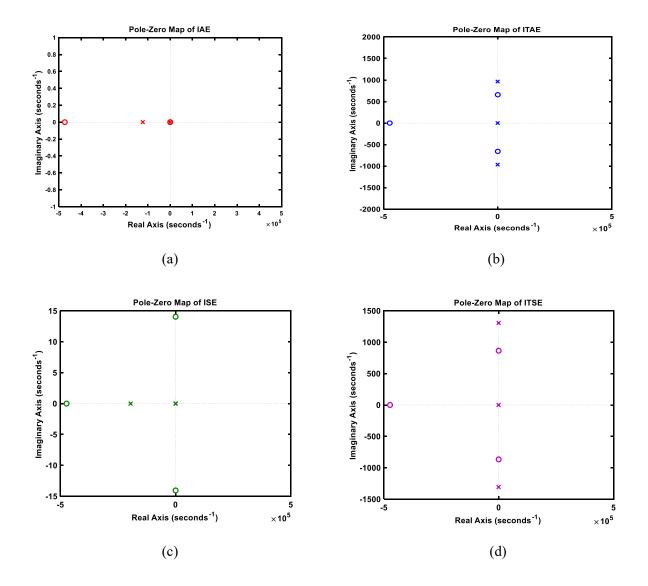

| 5.42 | Pole Zero Mapping for (a) IAE (b) ITAE (c) ISE (d) ITSE of GA-PID-2                                                                              | 100      |

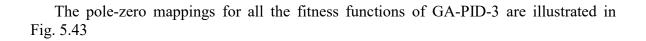

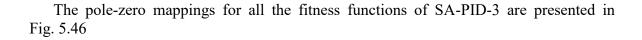

| 5.43 | Pole Zero Mapping for (a) IAE (b) ITAE (c) ISE (d) ITSE of GA-PID-3                                                                              | 101      |

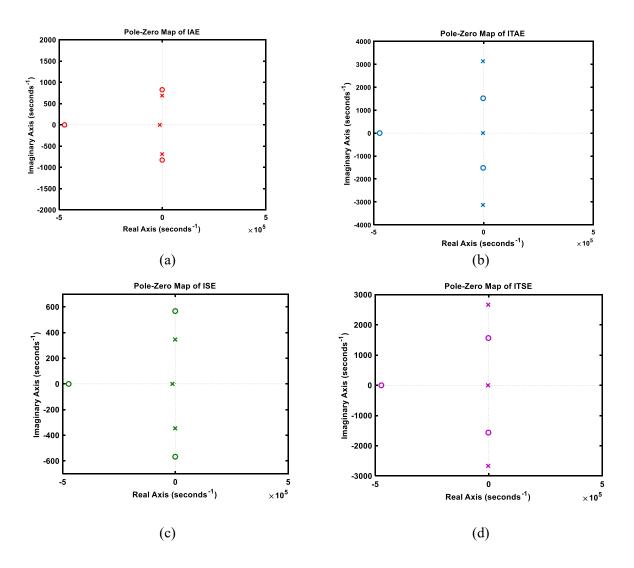

| 5.44 | Pole Zero Mapping for SA-PID-1 (a) IAE (b) ITAE (c) ISE (d) ITSE                                                                                 | 104      |

| 5.45 | Pole Zero Mapping for SA-PID-2 (a) IAE (b) ITAE (c) ISE (d) ITSE                                                                                 | 105      |

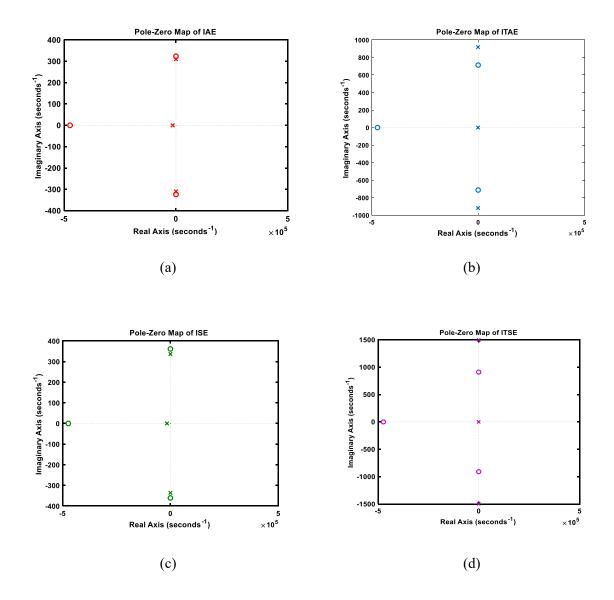

| 5.46 | Pole Zero Mapping for SA-PID-3 (a) IAE (b) ITAE (c) ISE (d) ITSE                                                                                 | 106      |

| 5.47 | Step Response of Conventional PID for 5% change in inductor's value                                                                              | 109      |

| 5.48 | Step Response of GA-PID-2 (IAE) for 5% change in inductor's value                                                                                | 110      |

| 5.49 | Step Response of SA-PID-2 (IAE) for 5% change in inductor's value                                                                                | 111      |

| 5.50 | Comparative Analysis of Step Responses of<br>Conventional PID, GA-PID-2 (IAE) and SA-PID-2<br>(IAE) controller for 5% change of inductor's value | 112      |

## **LIST OF ACRONYMS**

| Abbreviated Form | Descrption                                        |

|------------------|---------------------------------------------------|

| LED              | Light Emiting Diode                               |

| HID              | High Intensity Discharge                          |

| SEPIC            | Single Ended Primary Inductance Converter         |

| GA               | Genetic Algorithm                                 |

| SA               | Simulated Annelaing Algorithm                     |

| FNN              | Fuzzy Neural Network                              |

| PSO              | Particle Swarm Optimization                       |

| FLC              | Fuzzy Logic Controller                            |

| MPPT             | Maximum Power Point Tracking                      |

| NLC              | Non Linear Carrier                                |

| PFC              | Power Factor Correction                           |

| GMPPT            | Global Maximum Power Point Tracking               |

| SPDT             | Single Pole Double Throw                          |

| MOSFET           | Metal Oxide Semiconductor Field Effect Transistor |

| BJT              | Bipolar Junction Transistor                       |

| IAE              | Integral of Absolute Magnitude of Error           |

| ITAE             | Integral of Time multiplied by Absolute Error     |

| ISE              | Integral of Squared Error                         |

| ITSE             | Integral of Time multiplied by Squared Error      |

### **CHAPTER 1**

### INTRODUCTION AND BACKGROUND STUDY

Power Electronics is the technology associated with efficient conversion, control and conditioning of electric power by static means from its available input into the desired electrical output form. With rapid advancement and modernization in the field of power electronics, researchers are more aligned in modeling and designing reliable and robust systems to achieve better performance and efficiency. In this regard, DC-DC converters are on the top of the choice because of their widespread applications in battery charger [1], maximum power point tracking [2], LED drivers [3], motor drivers [4], braking system [5], renewable energy system applications, such as photovoltaic, fuel cell and wind turbine, dc micro-grid, telecommunication industries, high intensity discharge (HID) lamp ballast used in automotive headlamps, hybrid vehicles and switching mode regulators such as uninterruptable power supplies (UPS) etc. [6-11]. Hence, the increasing demand of dc-dc step up converters for various household and industrial applications demands further improvement of the performance of conventional dc-dc converters that could convert a fixed dc voltage level into a desired level in the most efficient way.

#### 1.1 Introduction

The DC-DC conversion techniques were established in the 1920s. Some preliminary types of DC-DC converters were used in industrial applications before the Second World War. Research was blocked during the war, but applications of DC-DC converters were recognized. After the war, the communication technology developed very rapidly and required low voltage dc power supplies. This resulted in the rapid development of DC-DC converter techniques.

Different types of converters are maneuvered in various applications in power electronics. Amongst them, Boost converter has high input current ripple and Buck converter gives high output voltage ripple. However, the effects can be minimized if coupled with switched capacitor [12] and switched inductor [13]. Meanwhile, Buck-boost converter suffers from harmonics and to minimize that phenomenon a large capacitor or an LC filter is required [14]. Hence, Cúk converters solve both of these problems by using an

extra capacitor and inductor [15]. However, huge amount of electrical stress on the components result in device failure or overheating. Thus, SEPIC converter manifests better performance in terms of these problems and is brought into play in different sectors of power electronics [16].

Various close loop control techniques like hysteresis current control, PI control and PID control are employed to observe the performance of SEPIC converter [17]. Among these control techniques, PID control is the most common and extensively used method for power converters. It comprises of three terms named as Proportional, Integral and Derivative component which are tuned by empirical methods like Ziegler-Nicholas method, analytical methods and different optimization techniques [18]. By taking into account different tuning methods, these parameters are tuned for close loop system to enhance the performance of the SEPIC converter.

However, it is quite difficult to determine the exact values of these parameters as most of the classical methods demand explicit mathematical modeling of the processing plant and may not provide satisfactory results because of input-output disturbances or nonlinear behavior of the plant. For this reason, nonlinear optimization methods named as Genetic Algorithm (GA), Simulated Annealing Algorithm (SAA), Particle Swarm Optimization (PSO), and Fuzzy Neural Network (FNN) are proven to be powerful tools in control engineering in recent years [19-21].

In this work, some effective nonlinear optimization techniques will be investigated and performances will be evaluated of the proposed system. Techniques like genetic algorithm (GA) and Simulated Annealing Algorithm (SAA) will be used for investigation and overall comparative analysis with the conventional method will be reported in terms of different performance parameters like rise time, settling time, overshoot, steady-state error and voltage stability.

#### 1.2 Literature review

DC-DC converters are considered to be of immense economical importance in today's modern society. The converters are classified into Buck, Boost, Buck-Boost, Cuk and SEPIC converters. Among all the converters, SEPIC converter is the most significant and widely employed as it can both increase and decrease the voltage by changing the duty cycle without reversing the polarity [22]. Moreover, small input ripple current and extension to multiple outputs are two prominent features of this converter [23].

The output voltage of SEPIC converter should be constant and stable. In this regard, feedback control is necessary so that stable output can be achieved. Various control techniques are employed in SEPIC converter to achieve better performance in terms of regulating the output voltage [24]. Among different control methods, Hysteresis Current control, PI control, PID control are the most common and extensively used methods for power converters [25]. Moreover, the usage of this controller ranges from small-scale industries to high technology industries [26], high step up applications [27], refineries and ship buildings.

PID controller comprises of three terms named as Proportional, Integral and Derivative component which are tuned by empirical methods like Ziegler-Nicholas method [28], analytical methods and different optimization techniques. The proportional component utilizes proportion of the system error to control it, the integral component introduces lag in the system which implicates that it evaluates the total past history of error by continuously integrating the area under the error curve and the derivative component responds to the rate of change of error and which can pro-duce a correction before the error approaches to a larger value. By taking into account different tuning methods, these parameters are tuned for different close loop systems to enhance the performance of the system. However, it is quite difficult to determine the exact values of these parameters as most of the classical methods demand explicit mathematical modeling of the processing plant and may not provide satisfactory results because of input-output disturbances or nonlinear behavior of the plant. To encounter the nonlinear behavior of the plant, different nonlinear optimization techniques are employed in order to design optimized PID controller. Genetic Algorithm (GA), Simulated Annealing (SA) Algorithm, Particle Swarm Optimization (PSO), Fuzzy Neural Network (FNN) are some of the techniques that are widely employed in optimizing the parameters of PID controller with a view to achieving better controller for power converters.

A Rubaai et al [29] employed a fuzzy controller in DC-DC converter where two different fuzzy logic control topologies are developed and implemented using different types of DC-DC converters such as the buck, the boost, the buck-boost, and the SEPIC converters. A. El Khateb et al. [30] presents a fuzzy logic controller (FLC)-based singleended primary-inductor converter (SEPIC) for maximum power point tracking (MPPT) operation of a photovoltaic (PV) system. The fuzzy controller for the SEPIC MPPT scheme shows high precision in current transition and keeps the voltage without any changes, in the variable-load case, represented in small steady-state error and small overshoot. Wei-Der Chang et al. [31] presented an improved particle swarm optimization algorithm to search for the optimal PID controller gains for a class of nonlinear systems. The proposed algorithm is to modify the velocity formula of the general PSO systems in order for improving the searching efficiency. In the improved PSO-based nonlinear PID control system design, three PID control gains are optimized to obtain stable output from nonlinear system. W. M. Utomo et al. [32] proposes a neural network control scheme of a DC-DC buck-boost converter using online learning method. In this technique, a back propagation algorithm is derived. The controller is designed to stabilize the output voltage of the DC-DC converter and to improve performance of the Buck-Boost converter during transient operations.

*R. Zane et al* [33] proposed a nonlinear-carrier (NLC) control for high-power-factor rectifiers based on fly back, Cuk or SEPIC converters operated in the continuous conduction mode. In the NLC controller, the switch duty ratio is determined by comparing a signal proportional to the integral of the switch current with a periodic nonlinear carrier waveform. *Subbiah Durgadevi et al.* [34] presents the analysis and design of a single phase power factor correction (PFC) scheme using a DC–DC single ended primary inductance converter (SEPIC) with genetic algorithm (GA)-tuned proportional integral (PI) controllers. A systematic off-line design approach using GA for optimizing the parameters of the PI controller. *Stefan Daraban et al.* [35] present a novel MPPT (maximum power point tracking) algorithm, based on a modified GA (genetic algorithm).

When photovoltaic systems are affected by partial shading, a GMPPT (global maximum power point tracking) algorithm is required to increase the energy harvesting capability of the system. *Amin Alqudah* [36] states a new adaptive control method used to adjust the output voltage and current of DC-DC power converter under different sudden changes in load where a PID controller is used. The gains of the PID controller tuned using Simulated Annealing (SA) algorithm which is part of Generic Probabilistic Metaheuristic family. The new control system is expected to have a fast transient response feature, with les undershoot of the output voltage and less over-shoot of the reactor current.

Genetic algorithm, a heuristic search algorithm [37-42] is proven to be the most powerful optimization technique in a large solution space and has received quite a lot of attention in control engineering in recent years. This algorithm is a method for solving both constrained and unconstrained optimization problems that is based on natural selection, the process that drives biological evolution and repeatedly modifies a population of individual solutions. In this case, GA is used to achieve optimum values of the PID controller [43-44] when implemented in close loop analysis of the SEPIC converter to investigate the stability of the system. Simulated Annealing (SA) algorithm is a probabilistic search algorithm which is widely applied in power electronics [45], stability analysis in different power converters [46], robotics [47], bioinformatics [48] and optimization problems [49]. In order to make really strong metallic objects, slow and controlled cooling is followed which is known as annealing. Hence, the concept is applied in this thesis with an intention of achieving the values of the PID controller ( $k_P$ ,  $k_I$  and  $k_D$ ) without the requirement of manual tuning.

#### **1.3** Statement of the Problem

SEPIC converter is one of the most widely employed converters in different applications of power electronics. As nonlinearity is associated with the system, obtaining stable and faster response is always a challenge for the control engineers. In case of open loop response of the converter, stable output can be achieved but high overshoot, longer rise time and settling time are noticed which is not desirable in modern power converters. In accordance to that, researchers are more aligned in developing compact, fast and robust power converters where stability can be achieved rapidly. In this regard, closed loop system is needed to achieve stable output with less overshoot, rise time and settling time and steady state error. For this, classical PID controller is employed but rigorous trial and error method is required to tune the parameters of the controller in order to achieve stable output. Hence, nonlinear optimization technique is deployed with a view to achieving optimized values of PID controller and acquiring enhanced performance of the overall system. Among various techniques, genetic algorithm and simulated annealing algorithm are implemented to design and develop optimized PID controller for SEPIC converter.

#### 1.4 Thesis objectives

The main thesis objective is to develop nonlinear optimization technique based PID controller for SEPIC converter. However, more particularly, the objectives include:

- To observe and estimate different performance parameters of power electronic converters specifically DC-DC SEPIC converter.

- To analyze the compatibility of different nonlinear techniques for controller design of power electronic converters.

- To optimize the performance parameters of closed loop SEPIC converter employing nonlinear control techniques. To carry out a comparative analysis between conventional controller and nonlinear optimization technique based controller for SEPIC Converter.

#### 1.5 Thesis organization

This thesis focuses on studying and developing nonlinear optimization technique based PID controller for obtaining better performance of SEPIC converter.

- In Chapter 2, different types of existing widely used dc-dc converters are discussed. The methods and analysis dc-dc converters are presented in details.

- In Chapter 3, conventional SEPIC converter is studied and State Space Modeling of the converter is illustrated. Then, open loop and closed loop analysis of the converter is carried out.

- In **Chapter 4**, general discussion on different nonlinear optimization techniques are reported. The elaborate discussion on implementation of Genetic Algorithm and Simulated Annealing Algorithm is depicted where overviews, objective function of the algorithm and design of the optimized PID Controller are stated.

- **Chapter 5** includes the simulation results of the nonlinear optimized PID controller for SEPIC converter. The performance parameters are investigated and quantitative analysis is presented.

- **Chapter 6** contains the conclusion of the thesis, where the brief summary of the results is given with some recommendations for future works.

### **CHAPTER 2**

### **DC-DC CONVERTERS**

DC-DC power converters are employed in a variety of applications, including renewable energy systems, power supplies for personal computers, office equipment, spacecraft power systems, laptop computers, and telecommunications equipment, as well as dc motor drives. The input to a dc-dc converter is an unregulated dc voltage,  $V_i$ . The converter produces a regulated output voltage,  $V_0$ , having a magnitude (and possibly polarity) that differs from $V_i$ . For example, in a computer off-line power supply, the 120 V or 240 V ac utility voltage is rectified, producing a dc voltage of approximately 170 V or 340 V, respectively.

A dc-dc converter then reduces the voltage to the regulated 5 V or 3.3 V required by the processor ICs. High efficiency is invariably required, since cooling of inefficient power converters is difficult and expensive. The ideal dc-dc converter exhibits 100% efficiency; in practice, efficiencies of 70% to 95% are typically obtained. This is achieved using switched-mode, or chopper, circuits whose elements dissipate negligible power. Pulse-width modulation (PWM) allows control and regulation of the total output voltage. This approach is also employed in applications involving alternating current, including high-efficiency dc-ac power converters (inverters and power amplifiers), ac-ac power converters, and some ac-dc power converters (low harmonic rectifiers).

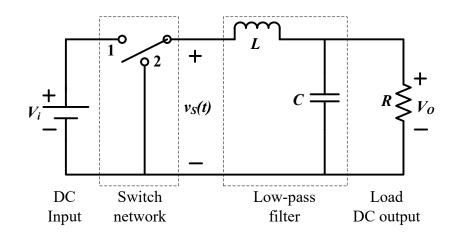

(a)

**Fig. 2.1** The buck converter consists of a switch network that reduces the dc component of voltage, and a low pass filter that removes the high-frequency switching harmonics: (a) schematic, (b) switch voltage waveform.

#### 2.1 Working principle of a dc-dc converter

A basic dc-dc converter circuit known as the buck converter is illustrated in Fig. 2.1. A single-pole double-throw (SPDT) switch is connected to the dc input voltage  $V_i$  as shown. The switch output voltage  $v_s(t)$  is equal to  $V_i$  when the switch is in position 1, and is equal to zero when the switch is in position 2. The switch position is varies periodically, such that  $v_s(t)$  is a rectangular waveform having period  $T_s$  and duty cycle D. The duty cycle is equal to the fraction of time that the switch is connected in position 1, and hence  $0 \le D \le 1$ . The switching frequency  $f_s$  is equal to  $1/T_s$ . In practice, the SPDT switch is realized using semiconductor devices such as diodes, power MOSFETs, IGBTs, BJTs, or thyristors. Typical switching frequencies lie in the range of 1 kHz to 1 MHz, depending on the speed of the semiconductor devices.

The switch network changes the dc component of the voltage. By Fourier analysis, the dc component of a waveform is given by its average value. The average value of  $v_s(t)$  is given by

$$V_{S} = \frac{1}{T_{S}} \int_{0}^{T_{S}} v_{s}(t) dt = DV_{i}$$

(2.1)

The integral is equal to the area under the waveform, or the height  $V_i$  multiplied by the time  $DT_s$ . It can be seen that the switch network reduces the dc component of the voltage by a factor equal to the duty cycle D. Since  $0 \le D \le 1$ , the dc component of  $v_s$  is less than or equal to  $V_i$ .

The power dissipated by the switch network is ideally equal to zero. When the switch contacts are closed, then the voltage across the contacts is equal to zero and hence the power dissipation is zero. When the switch contacts are open, then there is zero current and the power dissipation is again equal to zero. Therefore, the ideal switch network is able to change the dc component of voltage without dissipation of power.

In addition to the desired dc voltage component  $V_s$ , the switch waveform  $v_s(t)$  also contains undesired harmonics of the switching frequency. In most applications, these harmonics must be removed, such that the converter output voltage  $v_0(t)$  is essentially equal to the dc component  $V_0 = V_s$ . A low-pass filter is employed for this purpose. The converter of Figure 2.1 contains a single-section L-C low-pass filter. The filter has corner frequency  $f_0$  given by

$$f_0 = \frac{1}{2\pi\sqrt{LC}} \tag{2.2}$$

The corner frequency  $f_0$  is chosen to be sufficiently less than the switching frequency  $f_s$ , so that the filter essentially passes only the dc component of  $v_s(t)$ . To the extent that the inductor and capacitor are ideal, the filter removes the switching harmonics without dissipation of power. Thus, the converter produces a dc output voltage whose magnitude is controllable via the duty cycle D, using circuit elements that (ideally) do not dissipate power.

The conversion ratio G known as voltage gain is defined as the ratio of the dc output voltage  $V_0$  to the dc input voltage  $V_i$  under steady-state conditions:

$$G = \frac{v_0}{v_i} \tag{2.3}$$

For buck converter it is given by

$$G = D \tag{2.4}$$

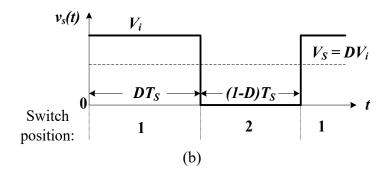

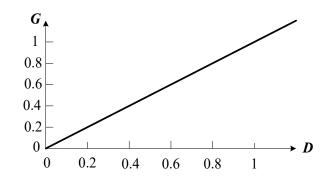

This equation is plotted in Fig. 2.2.

Fig. 2.2 Buck converter dc output voltage  $V_0$  vs. duty cycle D

It can be seen that the dc output voltage  $V_0$  is controllable between 0 and  $V_i$ , by adjustment of the duty cycle D.

#### 2.2 Analysis of converter waveforms

Under steady-state conditions, the voltage and current waveforms of a dc-dc converter can be found by use of two basic circuit analysis principles. The principle of inductor voltsecond balance states that the average value, or dc component, of voltage applied across an ideal inductor winding must be zero. This principle also applies to each winding of a transformer or other multiple winding magnetic devices. Its dual, the principle of capacitor amp second or charge balance, states that the average current that flows through an ideal capacitor must be zero. Hence, to determine the voltages and currents of dc-dc converters operating in periodic steady state, one averages the inductor current and capacitor voltage waveforms over one switching period, and equates the results to zero.

The equations are greatly simplified by use of a third artifice, the small ripple approximation. The inductor currents and capacitor voltages contain dc components, plus switching ripple at the switching frequency and its harmonics. In most well designed converters, the switching ripple is small in magnitude compared to the dc components. For inductor currents, a typical value of switching ripple at maximum load is 10% to 20% of the dc component of current. For an output capacitor voltage, the switching ripple is typically required to be much less than 1% of the dc output voltage. In both cases, the ripple magnitude is small compared with the dc component, and can be ignored.

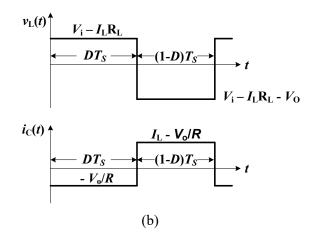

(a)

Fig. 2.3 A non-ideal boost converter: (a) schematic, (b) inductor voltage and capacitor current waveforms

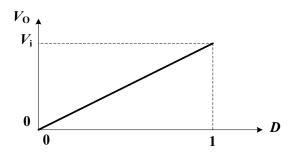

As an example, consider the boost converter of Fig. 2.3(a). A resistor  $R_L$  is included in series with the inductor, to model the resistance of the inductor winding. It is desired to determine simple expressions for the output voltage  $V_0$ , inductor current  $I_L$ , and efficiency  $\eta$ . Typical inductor voltage and capacitor current waveforms are sketched in Fig. 2.3(b).

With the switch in position 1, the inductor voltage is equal to  $v_L(t) = V_i - i_L(t)R_L$ . By use of the small ripple approximation, we can replace  $i_L(t)$  with its dc component  $I_L$ , and hence obtain  $v_L(t) \approx V_i - I_L R_L$ . Likewise, the capacitor current is equal to  $i_C(t) \approx$  $-v_0(t)/R$ , which can be approximated as  $i_C(t) = -V_0/R$ .

When the switch is in position 2, the inductor is connected between the input and output voltages. The inductor voltage can now be written  $v_L(t) = V_i - i_L(t)R_L - v_O(t) \approx V_i - I_LR_L - V_O$ . The capacitor current can be expressed as  $i_C(t) = i_L(t) - v_O(t)/R \approx I_L - V_O/R$ .

When the converter operates in steady state, the average value, or dc component, of the inductor voltage waveform  $v_L(t)$  must be equal to zero. Upon equating the average value of the  $v_L(t)$  waveform of Figure 2.4(b) to zero, we obtain

$$0 = D(V_i - I_L R_L) + (1 - D)(V_i - I_L R_L - V_0)$$

(2.5)

Likewise, application of the principle of capacitor charge balance to the capacitor current waveform of Fig. 2.4(b) leads to

$$0 = D\left(-\frac{V_0}{R}\right) + (1 - D)(I_L - \frac{V_0}{R})$$

(2.6)

Equations (2.5) and (2.6) can now be solved for the unknowns  $V_0$  and  $I_L$ . The result is

$$\frac{V_0}{V_i} = \frac{1}{(1-D)} \frac{1}{(1 + \frac{R_L}{(1-D)^2 R})}$$

(2.7)

$$I_L = \frac{V_i}{(1-D)^2 R} \frac{1}{(1+\frac{R_L}{(1-D)^2 R})}$$

(2.8)

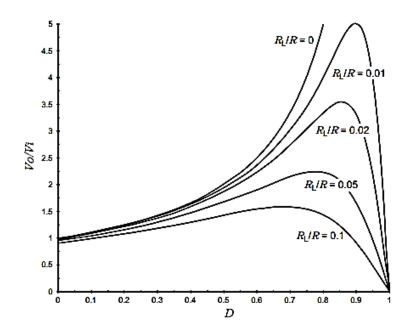

Fig. 2.4 Output voltage vs. duty cycle, for the non-ideal boost converter of Fig. 2.3

Equation (2.7) is plotted in Fig. 2.4, for several values of  $R_L/R$ . In the ideal case when  $R_L = 0$ , the voltage conversion ratio G is equal to one at D = 0, and tends to infinity as D approaches one. In the practical case where some small inductor resistance  $R_L$  is present, the output voltage tends to zero at D = 1. In addition, it can be seen that the inductor winding resistance  $R_L$  (and other loss elements as well) limits the maximum output voltage

that the converter can produce. Obtaining a given large value of  $V_0/V_i$  requires that the winding resistance  $R_L$  be sufficiently small.

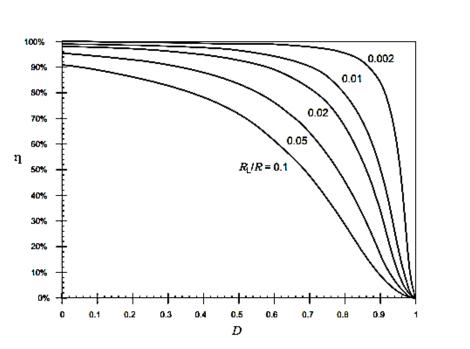

The converter efficiency can also be determined. For this boost converter example, the efficiency is equal to

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_0^2 / R}{V_i i_L}$$

(2.9)

Substitution of (2.7) and (2.8) into (2.9) leads to

$$\eta = \frac{1}{(1 + \frac{R_L}{(1 - D)^2 R})}$$

(2.10)

Fig. 2.5 Efficiency vs. duty cycle, for the non-ideal boost converter of Fig. 2.3

This expression is plotted in Fig. 2.5, again for several values of  $R_L/R$ . It can be seen that, to obtain high efficiency, the inductor winding resistance  $R_L$  should be much smaller than  $(1 - D)^2 R$ . This is much easier to accomplish at low duty cycles, where (1 - D) is close to unity, that at high duty cycles where (1 - D) approaches zero. Consequently, the efficiency is high at low duty cycles, but decreases rapidly to zero near D = 1. This behavior is typical of converters having boost or buck-boost characteristics.

#### 2.3 Converter circuit topologies

A large number of dc-dc converter circuits are known that can increase or decrease the magnitude of the dc voltage and/or invert its polarity [50-54]. These are basically divided into two categories- Isolated converters and Non-isolated converters. In this chapter, a discussion on different non-isolated converters is presented.

#### 2.3.1 Non- isolated converters

The commonly used non-isolated converters are:

- 1. Buck converter

- 2. Boost converter

- 3. Buck-boost converter

- 4. Cuk converter

- 5. SEPIC converter

In each of the above the converters, the switch is realized using a power MOSFET and diode. However, other semiconductor switches such as IGBTs, BJTs, or thyristors can be substituted if desired.

#### 2.3.1.1 Buck converter

Buck converter shown in Fig. 2.6 reduces the output voltage. When the switch is on, the diode is reverse biased and the inductor is charged by  $V_i$ . When the switch is off, the diode is forward biased and the inductor discharges to load. It has a voltage gain of G = D and it is plotted in Fig. 2.7.

Fig. 2.6 Buck converter

Fig. 2.7 Voltage gain versus duty cycle of buck converter

#### 2.3.1.2 Boost converter

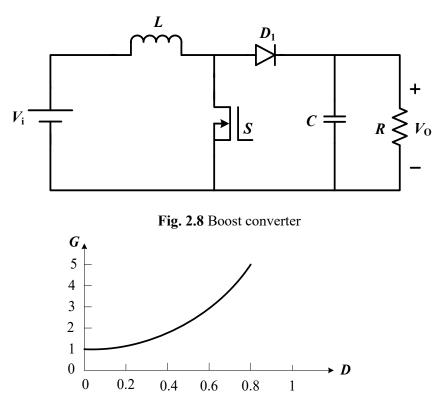

When the positions of switch and inductor are interchanged, the buck converter becomes boost converter shown in Fig. 2.8. It produces the output voltage greater than the input voltage. When the switch is on, the diode is reverse biased and the inductor is energized by  $V_i$ . When the switch is off, the diode gets forward biased and the inductor discharges to the load. The voltage gain of this converter is G = 1/(1-D) and it is depicted in Fig. 2.9.

Fig. 2.9 Voltage gain versus duty cycle of boost converter

#### 2.3.1.3 Buck-boost converter

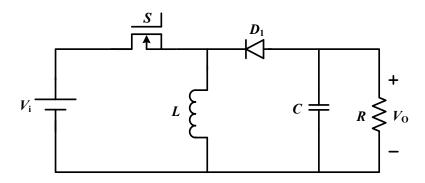

The buck-boost converter is the cascaded form of buck converter and boost converter. In the buck-boost converter shown in Fig. 2.10, the switch alternately connects the inductor across the power input and output voltages. This converter inverts the polarity of the voltage, and can either increase or decrease the voltage magnitude. When the switch is on, the diode is reverse biased and the inductor is charged, and the capacitor delivers power to load. When the switch is off, the diode gets forward biased and the inductor discharges to the capacitor and the load. The voltage gain is G = -D/(1-D) and it is shown in Fig. 2.11. The voltage stress in the switches will be high. It has non pulsating current characteristics [47]-[48].

Fig. 2.10 Buck-boost converter

Fig. 2.11 Voltage gain versus duty cycle of buck-boost converter

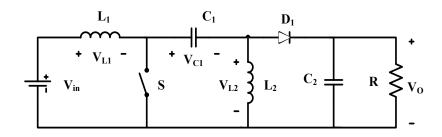

#### 2.3.1.4 Cuk converter

The Cuk converter contains inductors in series with the converter input and output ports. The switch network alternately connects a capacitor to the input and output inductors. The conversion ratio G is identical to that of the buck-boost converter. Hence, this converter also inverts the voltage polarity, while either increasing or decreasing the voltage magnitude. Fig. 2.12 and Fig. 2.13 show the circuit diagram and the voltage gain with respect to duty cycle respectively.

Fig. 2.12 Cuk converter

Fig. 2.13 Voltage gain versus duty cycle of cuk converter

The cuk converter has low switching losses and the highest efficiency. It can provide better output current characteristics due to the inductor on the output stage [55]-[57].

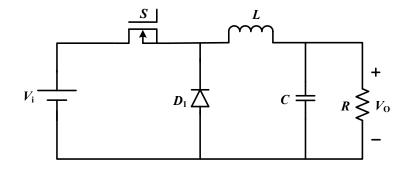

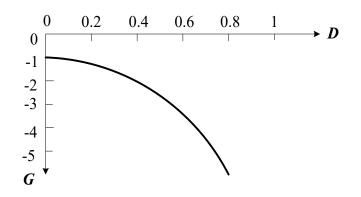

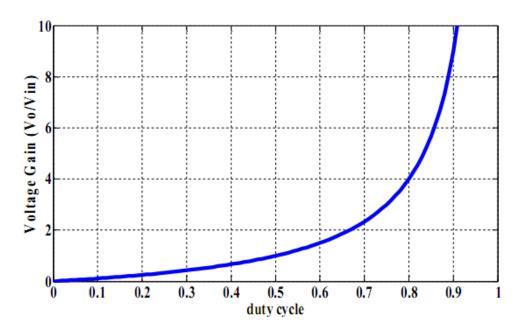

#### 2.3.1.6 SEPIC converter

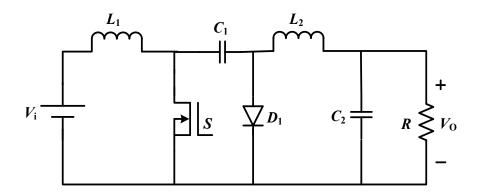

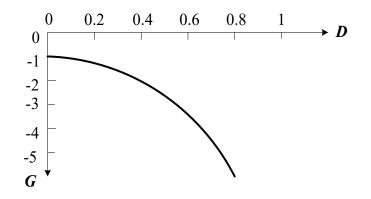

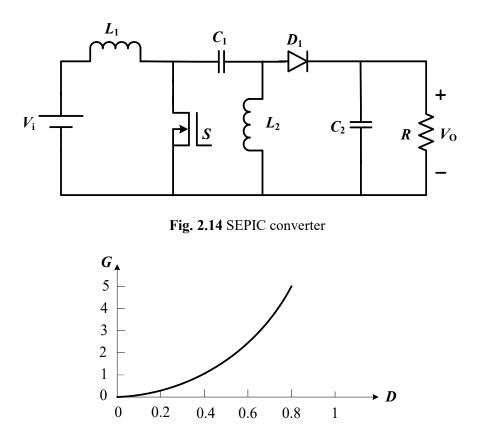

The single-ended primary inductance converter (SEPIC) can also either increase or decrease the voltage magnitude. However, it does not invert the polarity. The conversion ratio is G = D/(1 - D). The circuit diagram and the voltage gain with respect to duty cycle are shown in Fig. 2.14 and Fig. 2.15 respectively.

Fig. 2.15 Voltage gain versus duty cycle of SEPIC converter

Among all the converters, SEPIC converter is the most significant and widely employed as it can both step up and step down the voltage by changing the duty cycle without reversing the polarity. Moreover, small input ripple current and extension to multiple outputs are two prominent features of this converter [58]. For this reason, SEPIC converter is chosen as processing plant of this thesis. The mathematical modeling, open loop and closed loop response, implementation of optimized PID controller by nonlinear techniques, simulation results and comparative study are discussed in the forthcoming chapters.

# **CHAPTER 3**

# **DC-DC SEPIC CONVERTER**

Single Ended Primary Inductor converter is a widely used DC-DC converter which is a fourth-order system which makes it difficult to control and makes them only suitable for very slow varying applications. The output of the SEPIC is controlled by changing the duty cycle of the control transistor. *Hren & Slibar et al.* (2015) [59] have discussed that SEPIC is a DC-DC converter possessing high-voltage transfer gain, high power density, high efficiency, reduced ripple voltage and current. *Jaafer et al* (2013) [60] have studied that SEPIC converters are widely used in computer peripheral equipment, industrial applications and switch mode power supplies. *Chen & Sun* (2006) [61] have presented reduced order averaged modeling and analysis of soft switching DC-DC converters employing active clamping techniques which are applied in SEPIC converter.

Hence, it is identified that the SEPIC has high nonlinear behavior in static and dynamic conditions due to the switching nature of the power converter. The design of high performance control for SEPIC is a challenge for both the control engineers and the power electronic engineers. In general, a good control of DC-DC converters always ensures stability in arbitrary operating condition. With different state-space averaging techniques, a small-signal state-space equation of the converter system could be derived. For the purpose of optimizing the stability of SEPIC converter dynamics, while ensuring correct operation in any working condition, PI and PID control is a feasible approach. These control techniques offer several advantages such as stability, even for large line and load variations, reduce the steady error, robustness, good dynamic response and simple implementation. The main advantage of PI control schemes is its insusceptibility to plant/system parameter variations that lead to invariant dynamic and static response in the ideal case.

#### 3.1 Conventional SEPIC Converter

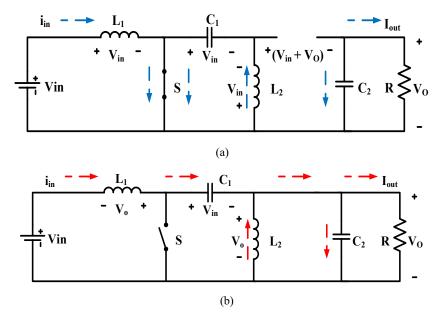

A Single Ended Primary Inductor Converter (SEPIC) is a significant converter in power electronics whose output voltage can be controlled by the duty cycle of the switching device. The SEPIC converter consists of two inductors ( $L_1$  and  $L_2$ ), two capacitors ( $C_1$  and  $C_2$ ), a switch (S) with duty cycle (D), a diode ( $D_1$ ), and a resistive load (R).

Fig. 3.1 Conventional SEPIC Converter [62]

The circuit diagram of the conventional SEPIC converter is shown in Fig. 3.1 and the equivalent circuits during ON and OFF states are shown in Fig. 3.2 (a & b). In SEPIC converter, at first when the switch is open, by applying KVL, is obtained. When the switch is closed, if KVL is applied in the inner loop is formed. So, capacitor C<sub>2</sub> is providing the load power in this case. The current through inductors L<sub>1</sub> and L<sub>2</sub> are ramping up and the capacitors (C<sub>1</sub> and C<sub>2</sub>) are getting discharged. When the switch is open again, the capacitors are getting charged and inductor currents are getting discharged. In this case, KVL shows that  $V_{L_1} = -V_o$ . The average voltage across L<sub>1</sub> is zero.

So, the equation can be written as,

$$V_{L_{1}(avg)} = DV_{in} + (1 - D)(-V_{out}) = 0$$

$$V_{o}(1 - D) = DV_{in}$$

$$\frac{V_{o}}{V_{in}} = \frac{D}{1 - D}$$

(3.1)

Fig. 3.2. Modes of operation of the conventional SEPIC converter (a) Switch ON and (b) Switch OFF

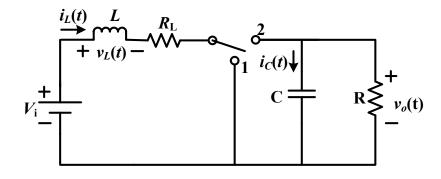

# 3.2 State Space Modeling

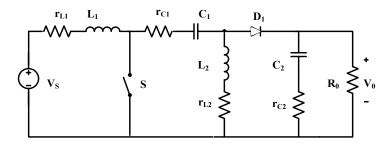

In order to represent the SEPIC converter by first order differential equation, state space average technique is taken into consideration as this mathematical model is best suited to describe any nonlinear dynamic system into simple form. A set of input, output and state variables are modeled in first order differential form and later the matrix is obtained. Hence, the state space representation provides a convenient and compact way to model and analyze a system with multiple inputs and outputs. Unlike the frequency domain approach, the use of the state space representation is to demonstrate the system with linear components and zero initial conditions which make it a handy tool to model power converters.

With a view to deriving the differential equations for the SEPIC converter, the circuit that is considered is as follows:

Fig. 3.3 Conventional SEPIC Converter

The state variables of SEPIC are considered as currents and voltages, respectively. When the converter is in continuous conduction mode, the operation can be outlined for two cases:

- A. Switch (S) is ON and Diode (D<sub>1</sub>) is OFFB. Switch (S) is OFF and Diode (D<sub>1</sub>) is ON

The circuit diagrams for case-A and case-B are given below as shown in Fig. 3.4:

Fig. 3.4 Modes of operation for the SEPIC converter (a) case A and (b) case B

The corresponding equations for the two cases are stated below:

Switch (S) is ON and Diode  $(D_1)$  is OFF:

$$\frac{dI_{L1}}{dt} = \frac{1}{L_1} \left( -r_{L1}I_{L1} + V_s \right)$$

(3.2)

$$\frac{dI_{L2}}{dt} = \frac{1}{L_2} \left[ -(r_{C1} + r_{L2})I_{L2} + V_{C1} \right]$$

(3.3)

$$\frac{dV_{C1}}{dt} = -\frac{1}{C_1} I_{L2}$$

(3.4)

$$\frac{dV_{C2}}{dt} = -\frac{1}{C_2} \frac{1}{R_0 + r_{C2}} V_{C2}$$

(3.5)

• Switch (S) is OFF and Diode (D<sub>1</sub>) is ON

$$\frac{dI_{L1}}{dt} = \frac{1}{L_1} \left[ -(r_{C1} + r_{L1} + r_{C2}r_A)I_{L1} - r_{C2}r_AI_{L2} - V_{C1} - r_AV_{C2} + V_s \right]$$

(3.6)

$$\frac{dI_{L2}}{dt} = \frac{1}{L_2} \left[ -r_{C2} r_A I_{L1} - (r_{L2} + r_{C2} r_A) I_{L2} - r_A V_{C2} \right]$$

(3.7)

$$\frac{dV_{C1}}{dt} = \frac{1}{C_1} I_{L1}$$

(3.8)

$$\frac{dV_{C2}}{dt} = \frac{1}{C_2} [r_A I_{L1} + r_A I_{L2} - \frac{1}{R_0 + r_{C2}} V_{C2}]$$

(3.9)

where,

$$r_A = \frac{R_o}{(R_o + r_{C2})}$$

For  $r_{C1} = r_{C2} = 0$ ,  $r_A = 1$ , putting the value in above equations the simplified forms are obtained and they are as follows:

i) For S ON and

$$D_1$$

OFF:

$$\frac{dI_{L1}}{dt} = \frac{1}{L_1} \left( -r_{L1} I_{L1} + V_s \right)$$

(3.10)

$$\frac{dI_{L2}}{dt} = \frac{1}{L_2} \left[ -r_{L2}I_{L2} + V_{C1} \right]$$

(3.11)

$$\frac{dV_{C1}}{dt} = -\frac{1}{C_1} I_{L2} \tag{3.12}$$

$$\frac{dV_{C2}}{dt} = -\frac{1}{C_2 R_0} V_{C2} \tag{3.13}$$

So in matrix form, the following equation is obtained:

$$\frac{d}{dt} \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix} = \begin{pmatrix} \frac{-r_{L1}}{L_1} & 0 & 0 & 0 \\ 0 & \frac{-r_{L2}}{L_2} & \frac{1}{L_2} & 0 \\ 0 & \frac{-1}{C_1} & 0 & 0 \\ 0 & 0 & 0 & \frac{-1}{R_0C_2} \end{pmatrix} \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix} + \begin{pmatrix} \frac{1}{L_1} \\ 0 \\ 0 \\ 0 \end{pmatrix} V_s$$

ii) For S OFF and  $D_1$  ON:

$$\frac{dI_{L1}}{dt} = \frac{1}{L_1} \left[ -r_{L1}I_{L1} - V_{C1} - V_{C2} + V_s \right]$$

(3.14)

$$\frac{dI_{L2}}{dt} = \frac{1}{L_2} \left[ -r_{L2} I_{L2} - V_{C2} \right]$$

(3.15)

$$\frac{dV_{C1}}{dt} = \frac{1}{C_1} I_{L1}$$

(3.16)

$$\frac{dV_{C2}}{dt} = \frac{1}{C_2} \left[ I_{L1} + I_{L2} - \frac{1}{R_0} V_{C2} \right]$$

(3.17)

So, in matrix form, the following equation is achieved:

$$\frac{d}{dt} \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix} = \begin{pmatrix} \frac{-r_{L1}}{L_1} & 0 & \frac{-1}{L_1} & \frac{-1}{L_1} \\ 0 & \frac{-r_{L2}}{L_2} & 0 & \frac{-1}{L_2} \\ \frac{1}{C_1} & 0 & 0 & 0 \\ \frac{1}{C_2} & \frac{1}{C_2} & 0 & \frac{-1}{R_0C_2} \end{pmatrix} \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix} + \begin{pmatrix} \frac{1}{L_1} \\ 0 \\ 0 \\ 0 \end{pmatrix} V_s$$

The state vector for the SEPIC converter is defined as

$$x(t) = \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix},$$

where  $I_{L1}$  and  $I_{L2}$  are the currents through  $L_1$  and  $L_2$  respectively,  $V_{C1}$  and  $V_{C2}$  are the voltages across the capacitors  $C_1$  and  $C_2$  respectively. So, the overall state space representation is stated by the following equation:

$$x(t) = Ax(t) + Bu(t)$$

where,

$$A = A_1 D + A_2 (1 - D)$$

$$B = B_1 D + B_2 (1 - D)$$

Here , A and B are system matrix and control matrix.  $A_1$  and  $B_1$  stand for ON condition;  $A_2$  and  $B_2$  stand for OFF condition.  $A_1$ ,  $A_2$ ,  $B_1$ ,  $B_2$  are as follows:

$$A_{1} = \begin{pmatrix} -r_{L1} & 0 & 0 & 0 \\ 0 & -r_{L2} & 1 & 0 \\ 0 & -\frac{1}{C_{1}} & 0 & 0 \\ 0 & 0 & -\frac{1}{C_{1}} & 0 & 0 \\ 0 & 0 & 0 & -\frac{1}{R_{0}C_{2}} \end{pmatrix}, A_{2} = \begin{pmatrix} -r_{L1} & 0 & -\frac{1}{L_{1}} & -\frac{1}{L_{1}} \\ 0 & -r_{L2} & 0 & -\frac{1}{L_{2}} \\ \frac{1}{C_{1}} & 0 & 0 & 0 \\ \frac{1}{C_{2}} & \frac{1}{C_{2}} & 0 & -\frac{1}{R_{0}C_{2}} \end{pmatrix}$$

$$B_{1} = \begin{pmatrix} \frac{1}{L_{1}} \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}, B_{2} = \begin{pmatrix} \frac{1}{L_{1}} \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}$$

The output of the system is stated by the following equation:

$$y(t) = Cx(t)$$

$$y(t) = (0 \quad 0 \quad 0 \quad 1) \begin{pmatrix} I_{L_1} \\ I_{L_2} \\ V_{C_1} \\ V_{C_2} \end{pmatrix}$$

C is the output matrix. In this case voltage ( $V_{C2}$ ) across capacitor  $C_2$  is considered as output variable. y(t) is the output vector. Hence, the transfer function of the DC-DC SEPIC converter is achieved from the following equation:

$$H_4(s) = (sI - A)^{-1}B + C \tag{3.18}$$

Here,  $H_4(s)$  states the forth order transfer function of the system. In order to reduce the computation time and complexity in the controller design, the fourth-order system is converted into the second-order system so that the transient behavior of the reduced order model remains the same as that of the original order model by retaining the dominant poles. Thus, it is inferred that the time domain parameters of the reduced order model are retained as that of the original fourth order model. There are various model order reduction

methods available. Here, the moment matching technique has been applied to reduce the fourth-order system into the second-order system. The technique is essentially the matching of time-moments of full order model's response to those of the reduced order model. The transfer function for third order reduced model is given by the following equation:

$$H_{3}(s) = \frac{a_{31} + a_{32}s + a_{33}s^3}{1 + a_{21}s + a_{22}s^2 + a_{23}s^3}$$

(3.19)

Here, The values of  $a_{31}$  to  $a_{33}$  are found by using the coefficients C<sub>0</sub>, C<sub>1</sub>,C<sub>2</sub>, C<sub>3</sub>, C<sub>4</sub>, C<sub>5</sub> as given in the following equations:

$$\begin{bmatrix} a_{31} \\ a_{32} \\ a_{33} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ C_0 & 0 & 0 \\ C_1 & C_0 & 0 \end{bmatrix} \begin{bmatrix} a_{21} \\ a_{22} \\ a_{23} \end{bmatrix} + \begin{bmatrix} C_0 \\ C_1 \\ C_2 \end{bmatrix}$$

(3.20)

$$\begin{bmatrix} a_{21} \\ c_{22} \\ a_{23} \end{bmatrix} = \begin{bmatrix} C_2 & C_1 & C_0 \\ C_3 & C_2 & C_1 \\ C_4 & C_3 & C_2 \end{bmatrix} \begin{bmatrix} -C_3 \\ -C_4 \\ -C_5 \end{bmatrix}$$

(3.21)

After that, the general expression for the reduced second-order transfer function is given as:

$$H_{2}(s) = \frac{a_{21} + a_{22}s}{1 + a_{11}s + a_{12}s^2}$$

(3.22)

The values of  $a_{11}$ ,  $a_{12}$ ,  $a_{21}$ ,  $a_{22}$  are found by using the coefficients C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> as given below:

$$\begin{bmatrix} a_{11} \\ a_{12} \end{bmatrix} = \begin{bmatrix} C_1 & C_0 \\ C_2 & C_1 \end{bmatrix} \begin{bmatrix} -C_2 \\ -C_3 \end{bmatrix}$$

(3.23)

$$\begin{bmatrix} a_{21} \\ a_{22} \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ C_0 & 0 \end{bmatrix} \begin{bmatrix} a_{11} \\ a_{12} \end{bmatrix} + \begin{bmatrix} C_0 \\ C_1 \end{bmatrix}$$

(3.24)

Thus, the reduced model is obtained so that this transfer function can be utilized to inspect the stability of the DC-DC converter.

## 3.3 Design of DC-DC SPEIC Converter

DC–DC SEPIC can perform in Buck mode for d<0.5 and in Boost mode for d>0.5. The assumption of a lossless circuit needs that the input power should be equal to output power.

So,

$$I_0 = \frac{(1-D)I_{in}}{D}$$

. When the switch is OFF, L is discharging,  $\Delta I_{L1} = \frac{V_0(1-D)}{L1f_s}$

Here, fs is the switching frequency.

The boundary of continuous condition for L1 is when  $I_{L1\min} = 0$ .

At boundary condition,  $2I_{in} = \frac{V_o(1-D)}{Llbf_s}$ . So that,  $Llb = \frac{V_o(1-D)}{2I_{in}f_s} = \frac{V_sD}{2I_{in}f_s}$ where L1b is the inductance at the boundary condition. As d approaches unity, the inductor L1 becomes,  $Ll > \frac{V_s}{2I_{in}f_s}$

This equation confirms that the continuous conduction can be achieved more easily, when Iin and fs are larger than than  $I_D$ .

When the switch S is OFF, L<sub>2</sub> is discharging

So,

$$\Delta I_{L2} = \frac{-V_O(1-D)}{L2f_S}$$

The boundary of continuous conduction for L2 is when  $I_{L2\min} = 0$ .

At this boundary,  $2I_o = \frac{V_o(1-D)}{L2bf_S}$

Since the maximum value occurs at d=0, the derived inductor L2 becomes  $L2 > \frac{V_0}{2I_0 f_s}$

The maximum peak to peak ripple voltage  $\Delta V_m$  occurs as d=1, so  $\Delta V_m = \frac{I_o}{Clf_s}$

And

$$C2 = \frac{P_o}{4\pi f_s V_o \Delta V_0}$$

Thus the circuit parameters are chosen for SEPIC converter and tabulated in Table 3.1

| Parameter           | Symbol                    | Values          |  |  |  |  |

|---------------------|---------------------------|-----------------|--|--|--|--|

| Input Voltage       | V <sub>in</sub>           | 10 V            |  |  |  |  |

| Switching Frequency | $\mathbf{f}_{\mathbf{s}}$ | 100 KHz         |  |  |  |  |

| Duty Cycle          | d                         | 0.5             |  |  |  |  |

| Inductor            | $L_{1, L_{2}}$            | 100 µH          |  |  |  |  |

| Resistance          | $r_{L1}, r_{L2}$          | 1 mΩ            |  |  |  |  |

|                     | r <sub>C1</sub>           | 3 mΩ<br>1 mΩ    |  |  |  |  |

|                     | r <sub>C2</sub>           |                 |  |  |  |  |

| Capacitor           | $C_{1,}C_{2}$             | 800 µF, 3000 µF |  |  |  |  |

| Load Resistance     | R <sub>o</sub>            | 1 Ω             |  |  |  |  |

| Output Voltage      | Vo                        | 10 V            |  |  |  |  |

Table 3.1 Parameters used for SEPIC Converter [91]

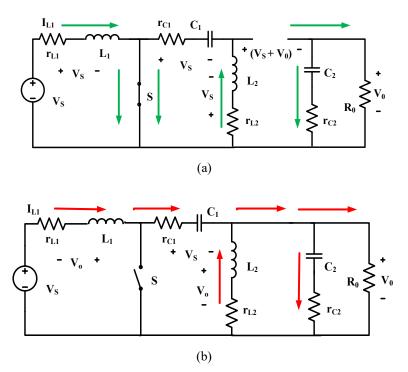

## 3.4 Gain Equation of SEPIC Converter

For ideal converter, when no equivalent series is considered, the output voltage is related to the input voltage by duty cycle.

$$\frac{V_o}{V_{in}} = \frac{D}{1 - D} \tag{3.25}$$

By varying the duty cycle from 0 to 1, the output voltage can be varied. The equation 3.18 is rearranged to convert into voltage gain  $(V_o/V_{in})$ . The graph is taken between voltage gain and duty cycle which is shown in Fig. 3.5. When the duty cycle is 0, the voltage gain is 0. By increasing the duty cycle, the voltage gain increases, and at duty cycle of 0.5, the voltage gain is 1. That means the duty cycle below 0.5, the converter steps down the input voltage. At 0.5, the output voltage is equal to the input voltage. Duty cycle above 0.5, the voltage gain increases above 1 and since the derivation is for ideal converter, when duty cycle is 1, the voltage gain is infinity. The equation 3.18 is not valid for practical converter. That's why the equation is modified by including the internal resistances for inductor and capacitor. In ideal converter, the output voltage does not depend upon the load resistance whereas in practical converter, the output voltage depends on both load resistance and equivalent series resistance.

Fig. 3.5 Voltage Gain vs. duty cycle with variable load.

The output voltage for practical converter is

$$V_o = \frac{V_{in}}{\frac{1-D}{D} + \frac{Dr_{L1}}{(1-D)R} - \frac{(1-D)r_{L2}}{DR} + \frac{(2D-1)r_{C1}}{R}}$$

(3.26)

By rearranging the equation, the voltage gain is calculated and it is drawn against the duty cycle. Fig. 3.6 shows the variation of voltage gain with respect to duty cycle for different load. It is shown that when the load resistance increases, the maximum voltage gain is also increases. In this figure, R is varied from 1 to 10  $\Omega$  and it is observed that upto duty cycle 0.8, there is no change of voltage gain, but when it is more than 0.8, the voltage gain is different for different value of R which is increasing for increasing of R.

Fig. 3.6 Voltage Gain vs. duty cycle with variable load.

# 3.5 Response of Average Model

The converter is derived by converting into mathematical equation. The averaging state space model in matrix form is defined in the program and the values of parameters are utilized and with the help of programming language, the state space model is converted into transfer function which is a 4th order function.

$$H_4(s) = \frac{4.995s^3 + 1.655e^6s^2 + 7.284e^7s + 1.041e^{13}}{s^4 + 393s^3 + 7.933e^6s^2 + 2.319e^9s + 1.045e^{13}}$$

(3.27)

Now the converter is reduced into  $2^{nd}$  order by using model order reduction technique. The  $2^{nd}$  order transfer function is

$$H_2(s) = \frac{3.515s + 1.664e^6}{s^2 + 362.8s + 1.671e^6}$$

(3.28)

The average model is used for steady state analysis. The output voltage waveform is shown in Fig. 3.7 with duty cycle 0.5. It is shown that the steady state is achieved approximately at 0.03 sec.

Fig. 3.7 Voltage amplitude Vs. Time for output of average model