### VOLTAGE CONVERSION TECHNIQUES: DESIGN AND ANALYSIS OF HIGH GAIN HYBRID DC-DC CONVERTER USING SC-SL COMBINED STRUCTURES

by

Md Sultanul Arfin (152480) Abdullah Al Mamun (152477) Sharif Nafis Mahmood (152455) Tanzil Chowdhury (152481)

A Thesis Submitted to the Academic Faculty in Partial Fulfillment of the Requirements for the Degree of

#### BACHELOR OF SCIENCE IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering

Islamic University of Technology (IUT)

Gazipur, Bangladesh

November 2019

### VOLTAGE CONVERSION TECHNIQUES: DESIGN AND ANALYSIS OF HIGH GAIN HYBRID DC-DC CONVERTER USING SC-SL COMBINED STRUCTURES

Approved by:

### **Dr. Golam Sarowar**

Supervisor and Associate Professor, Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT) Board Bazar, Gazipur- 1704.

Date:

# Table of Contents

| List of Figures                                | VII   |

|------------------------------------------------|-------|

| List of Tables                                 | XI    |

| Acknowledgment                                 | XII   |

| Abstract                                       | XIII  |

| 1 Introduction                                 |       |

| 1.1 Background                                 |       |

| 1.2 Motivation                                 | 2     |

| 1.3 Objective                                  |       |

| 2 Brief Analysis of DC-DC Converter            |       |

| 2.1 Introduction                               |       |

| 2.2 Historical Review                          | 5     |

| 2.3 DC-DC Converter Family Tree                | 6     |

| 2.4 Development of DC-DC Conversion Techniques | 7     |

| 2.4.1 Classical Converters                     | 7     |

| 2.4.2 Multi-quadrant Converters                | 15    |

| 2.4.3 Switched Component Converters            |       |

| 2.4.4 Soft Switching Converters                |       |

| 2.4.5 Synchronous Rectifier Converters         |       |

| 2.4.6 Multi-elements Resonant Power Converters |       |

| 3 Voltage Boosting Techniques                  | 21-35 |

| 3.1 Switched Capacitor                         |       |

| 3.2 Voltage Multiplier                         |       |

| 3.2.1 Voltage Multiplier Cell                  |       |

| 3.2.2 Voltage Multiplier Rectifier             |       |

| 3.3 Switched Inductor and Voltage Lift                           |              |

|------------------------------------------------------------------|--------------|

| 3.4 Magnetic Coupling                                            |              |

| 3.4.1 Transformer                                                |              |

| 3.4.2 Coupled Inductor                                           |              |

| 3.5 Multistage/Multilevel                                        |              |

| 3.5.1 Cascaded                                                   |              |

| 3.5.2 Interleaved                                                |              |

| 3.5.3 Multilevel                                                 |              |

| 3.6 Summary                                                      |              |

| 4 Design of Switched Capacitor and Switched Inductor Combined St | ructure36-52 |

| 4.1 Introduction                                                 |              |

| 4.2 Working Procedure                                            |              |

| 4.3 Existing Structures                                          | 41           |

| 4.4 Applications                                                 |              |

| 4.5 Proposed Design                                              |              |

| 4.5.1 Proposition                                                |              |

| 4.5.2 Proposed Structures                                        |              |

| 5 Conventional Zeta & Ćuk circuits Analysis                      | 53-64        |

| 5.1 Zeta Converter                                               | 53           |

| 5.1.1 Converter Circuits                                         | 53           |

| 5.1.2 Operating Principle                                        | 54           |

| 5.1.3 Steady State Analysis                                      | 55           |

| 5.1.3.1 Continuous Conduction Mode                               |              |

| 5.2 Ćuk Converter                                                |              |

| 5.2.1 Converter Circuits                                         |              |

| 5.2.2 Operating Principle                                        | 59           |

| 5.2.3 Steady State Analysis                           |       |

|-------------------------------------------------------|-------|

| 5.2.3.1 Continuous Conduction Mode                    | 62    |

| 5.2.3.2 Discontinuous Conduction Mode                 | 64    |

| 6 Zeta based Combined SC-SL Structure Analysis in CCM | 65-82 |

| 6.1 Topology of proposed circuit                      | 65    |

| 6.2 Assumptions                                       |       |

| 6.3 Working Principle                                 | 66    |

| 6.3.1 Time Interval: 0 < t < DT                       | 66    |

| 6.3.2 Time Interval: DT < t < T                       | 67    |

| 6.4 Steady State Analysis of proposed circuit         |       |

| 6.4.1 DC gain Analysis                                |       |

| 6.4.2 Average Current Analysis                        | 69    |

| 6.4.3 Current Stress Analysis of Switches             |       |

| 6.4.4 Voltage Stress Analysis of Components           |       |

| 6.4.5 Power Loss and Efficiency Measurement           |       |

| 6.5 Simulation Results                                |       |

| 6.5.1 Assumptions                                     |       |

| 6.5.2 Waveform of Voltage & Current                   |       |

| 6.5.3 Comparison of Gain                              | 77    |

| i) Comparison of Theoretical and Simulated gain       |       |

| ii) Comparison with existing converters               |       |

| 6.5.4 Comparison of Voltage Stress                    |       |

| 6.5.5 Efficiency Results                              |       |

| 6.5.6 Comparison Table                                |       |

| 6.6 Conclusion                                        |       |

| 7 Ćuk based Combined SC-SL Structure Analysis in CCM  |       |

| 7.1 Topology of proposed circuit                      |       |

| 7.2 Assumptions                                 | . 84 |

|-------------------------------------------------|------|

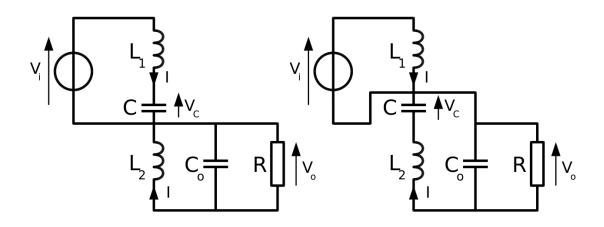

| 7.3 Working Principle                           | . 84 |

| 7.3.1 Time Interval: 0 < t < DT                 | . 84 |

| 7.3.2 Time Interval: DT < t < T                 | . 85 |

| 7.4 Steady State Analysis of proposed circuit   | .86  |

| 7.4.1 DC gain Analysis                          | . 86 |

| 7.4.2 Average Current Analysis                  | . 88 |

| 7.4.3 Current Stress Analysis of Switches       | . 90 |

| 7.4.4 Voltage Stress Analysis of Components     | . 91 |

| 7.4.5 Power Loss and Efficiency Measurement     | 91   |

| 7.5 Simulation Results                          | . 94 |

| 7.5.1 Assumptions                               | . 94 |

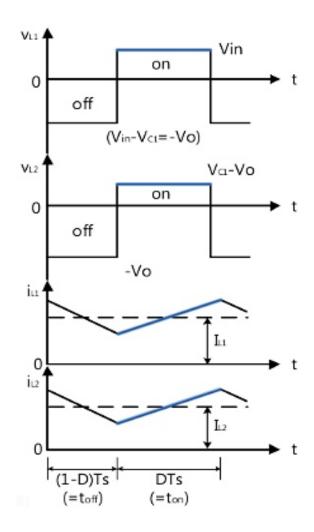

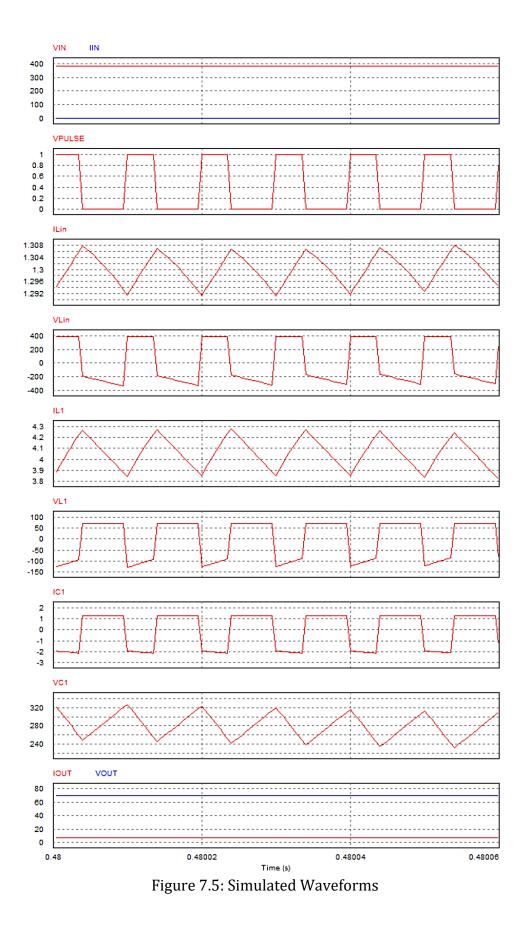

| 7.5.2 Waveform of Voltage & Current             | . 94 |

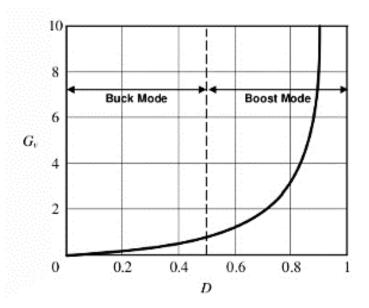

| 7.5.3 Comparison of Gain                        | . 96 |

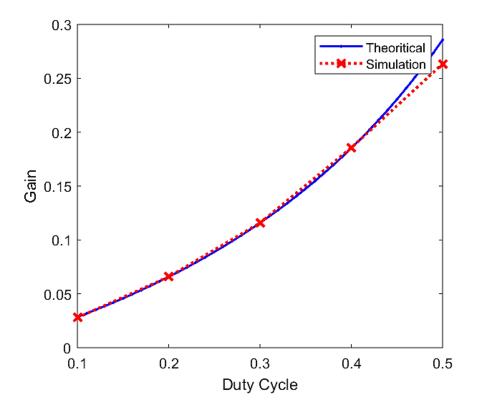

| i) Comparison of Theoretical and Simulated gain | . 96 |

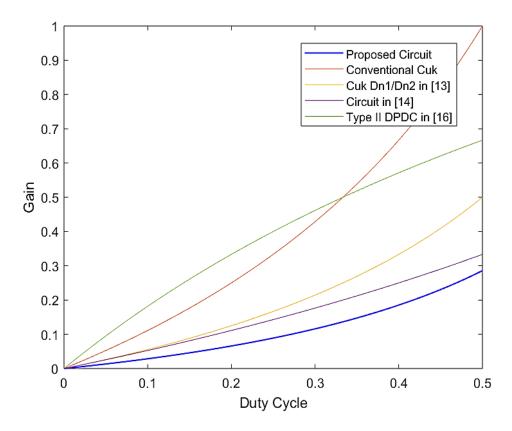

| ii) Comparison with existing converters         | . 97 |

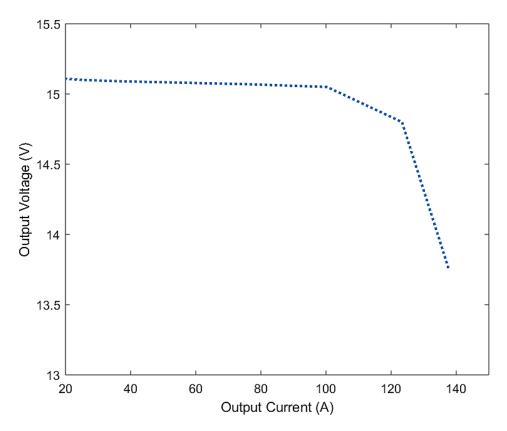

| 7.5.4 Load Regulation                           | . 98 |

| 7.5.5 Comparison Table                          | . 99 |

| 7.6 Conclusion                                  | 99   |

| 8 Summary and Contribution of the dissertation  | 101  |

| 8.1 Summary                                     | 100  |

| 8.2 Future Contribution                         | 101  |

| 9 Bibliography 102-2                            | 107  |

# <u>List of Figures</u>

| Figure 2.1  | Energy Storage Device L1 & C1 in a DC-DC Converter       | . 4 |

|-------------|----------------------------------------------------------|-----|

| Figure 2.2  | Basic Block Diagram of DC-DC Converter                   | . 5 |

| Figure 2.3  | DC-DC Converter Family Tree                              | . 6 |

| Figure 2.4  | Conventional Buck Converter circuit diagram              | . 7 |

| Figure 2.5  | Conventional Boost Converter circuit diagram             | . 8 |

| Figure 2.6  | Conventional Buck Boost Converter circuit diagram        | . 8 |

| Figure 2.7  | Forward Converter circuit diagram                        | . 9 |

| Figure 2.8  | Push Pull Converter circuit diagram                      | 10  |

| Figure 2.9  | Fly Back Converter circuit diagram                       | 10  |

| Figure 2.10 | Half Bridge Converter circuit diagram                    | 11  |

| Figure 2.11 | Full Bridge Converter circuit diagram                    | 11  |

| Figure 2.12 | Positive Output Luo Converter circuit diagram            | 12  |

| Figure 2.13 | Negative Output Luo Converter circuit diagram            | 12  |

| Figure 2.14 | Ćuk Converter circuit diagram                            | 13  |

| Figure 2.15 | SEPIC circuit diagram                                    | 13  |

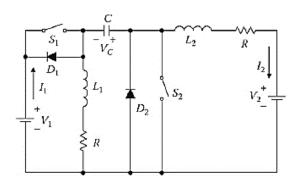

| Figure 2.16 | Self lift Ćuk Converter circuit diagram                  | 14  |

| Figure 2.17 | Positive Output Super Lift Luo Converter Circuit Diagram | 14  |

| Figure 2.18 | Multi-quadrant Luo Converter Circuit Diagram             | 15  |

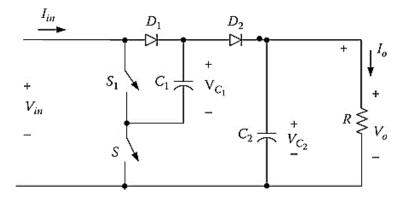

| Figure 2.19 | P/O Push Pull SC Luo Converter circuit diagram           | 16  |

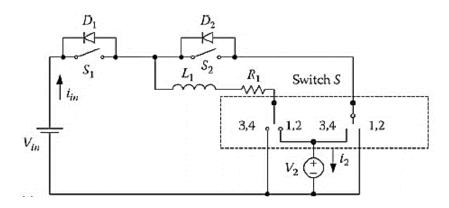

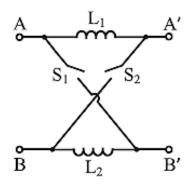

| Figure 2.20 | 4-Quadrant SL DC-DC Luo Converter circuit diagram        | 17  |

| Figure 2.21 | DC-DC ZCS Quasi Resonant Luo Converter for Q-I & Q-II                 | 18   |

|-------------|-----------------------------------------------------------------------|------|

| Figure 2.22 | DC-DC ZVS Quasi Resonant Luo Converter for Q-I & Q-II                 | 19   |

| Figure 2.23 | Zero-transition DC-DC Luo-converters for Q-I & Q-II                   | 19   |

| Figure 3.1  | Categorizations of voltage boost techniques used for DC-DC converters | 21   |

| Figure 3.2  | Basic charge pump and switched capacitor circuits                     | 22   |

| Figure 3.3  | Voltage multiplier cells in step-up converters                        | . 23 |

| Figure 3.4  | General topological view of the placement of VMRs                     | . 24 |

| Figure 3.5  | Various half-wave VMRs Configurations                                 | 25   |

| Figure 3.6  | Various full-wave VMRs Configurations                                 | 25   |

| Figure 3.7  | Voltage lift cell Configuration                                       | 26   |

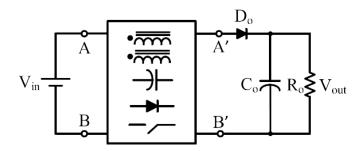

| Figure 3.8  | Isolated DC-DC converters                                             | . 28 |

| Figure 3.9  | Step-up DC-DC converter consisting of built-in transformer concept    | 28   |

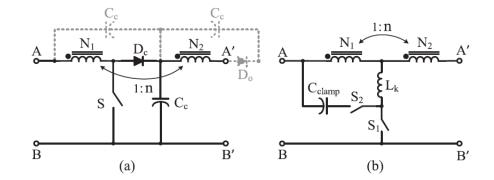

| Figure 3.10 | Tapped-inductor based converters                                      | 29   |

| Figure 3.11 | General layout of the coupled-inductor-based step-up converter        | 30   |

| Figure 3.12 | Coupled-inductor-based circuits.                                      | 30   |

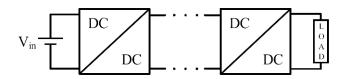

| Figure 3.13 | General layout of the cascaded DC-DC converter.                       | 31   |

| Figure 3.14 | Quadratic DC-DC converters.                                           | . 31 |

| Figure 3.15 | General layout of the cascaded connection of two different converters | 32   |

| Figure 3.16 | Interleaved DC-DC converters Configurations.                          | . 32 |

| Figure 3.17 | Interleaved DC-DC converters                                          | 33   |

| Figure 3.18 | Multilevel cascaded DC-DC converters with multiple dc sources         | 34   |

| Figure 4.1  | Basic SC step-down DC-DC converter                                    | 37   |

| Figure 4.2  | Step-down converter with two SC sub-circuits                          | 37   |

| Figure 4.3  | Basic Switched Inductor cell.                                         | 38   |

| Figure 4.4    | Basic Switched Capacitor Cell                                                           | . 38 |

|---------------|-----------------------------------------------------------------------------------------|------|

| Figure 4.5    | Switched Capacitor Structure for Step Down purposes                                     | . 39 |

| Figure 4.6    | Switching States of Switched Capacitor cell                                             | . 39 |

| Figure 4.7    | Switched Inductor Structure for Step Up purposes                                        | . 40 |

| Figure 4.8    | Switching states of Switched Inductor cell                                              | 40   |

| Figure 4.9    | Switched Capacitor VM cell with auxiliary Switch                                        | . 41 |

| Figure 4.10   | Various Switched capacitors DC-DC Converters                                            | 42   |

| Figure 4.11   | Basic A- SL Improved A-SL & Hybrid A-SL cells.                                          | . 42 |

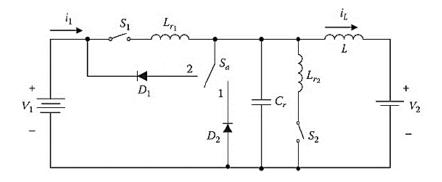

| Figure 4.12   | Switched Coupled Inductor based Boost Converter                                         | . 43 |

| Figure 4.13   | Typical Switched Coupled Inductor Components                                            | . 44 |

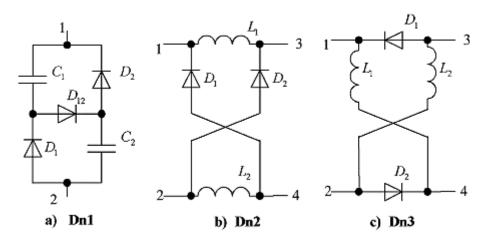

| Figure 4.14   | Basic Step Down switching structures, (a) Dn1 (b) Dn2 & (c) Dn3                         | 45   |

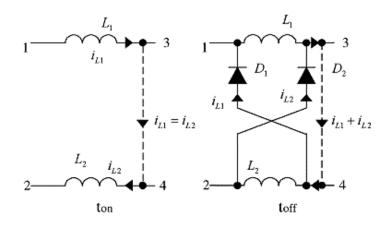

| Figure 4.15   | Switching Topology of the Dn2 step down structure                                       | 45   |

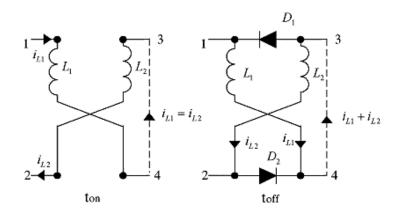

| Figure 4.16   | Switching Topology of the Dn3 step down structure                                       | 45   |

| Figure 4.17   | Basic Step Up switching structures, (a) Up1 (b) Up2 & (c) Up3                           | . 46 |

| Figure 4.18   | Switching Topology of the Up1 step up structure                                         | . 46 |

| Figure 4.19   | Switching Topology of the Up2 step up structure                                         | . 47 |

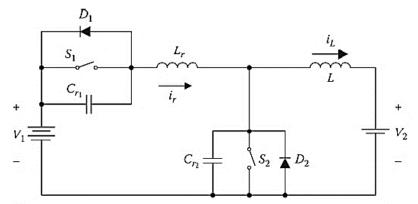

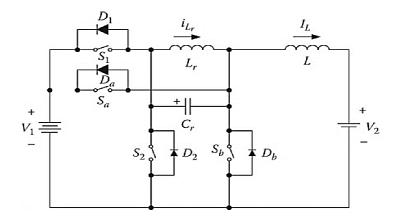

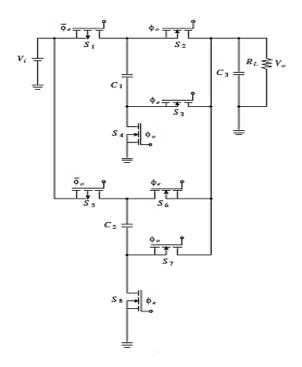

| Figure 4.20   | Combined structure for step up converter implemented on Zeta                            | . 49 |

| Figure 4.21   | Current direction in Time interval 0 <t<dts (mode="" i)<="" td=""><td>. 50</td></t<dts> | . 50 |

| Figure 4.22   | Current direction in Time interval DTs <t<ts (mode="" ii)<="" td=""><td> 50</td></t<ts> | 50   |

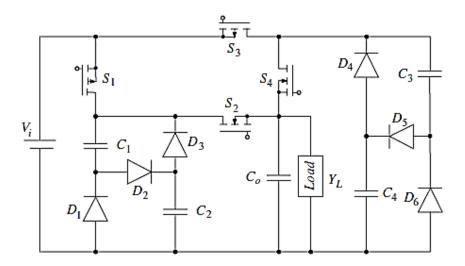

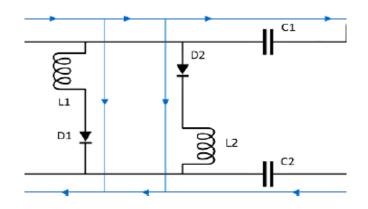

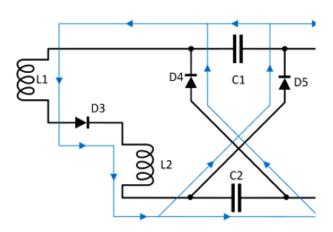

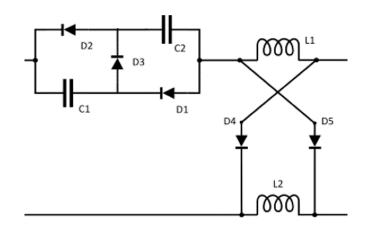

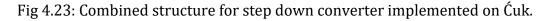

| Figure 4.23   | Combined structure for step down converter implemented on Ćuk                           | 51   |

| Figure 4.24   | Current direction in Time interval 0 <t<dts (mode="" i)<="" td=""><td>. 52</td></t<dts> | . 52 |

| Figure 4.25   | Current direction in Time interval DTs <t<ts (mode="" ii)<="" td=""><td> 52</td></t<ts> | 52   |

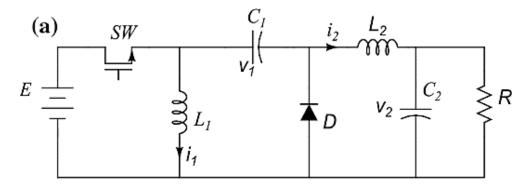

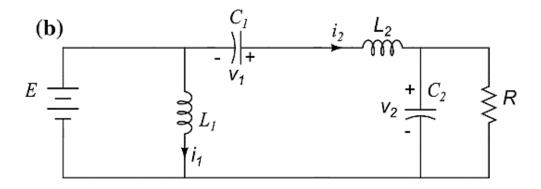

| Figure 5.1(a) | ) Conventional Zeta Converter circuit diagram                                           | 53   |

| Figure 5.1(b) | ) Time interval 0 <t<dts. (sw="" mode)<="" on="" td=""><td>. 54</td></t<dts.>           | . 54 |

| Figure 5.1(c) | Time interval DTs <t<ts. (sw="" mode)<="" off="" td=""><td> 54</td></t<ts.>             | 54   |

| Figure 5.2    | Component Current during ON & OFF states of CCM                                         | 55   |

| Figure 5.3    | Schematic of a non-isolated Ćuk Converter                                               | 58   |

| Figure 5.4 | ON state of a non-isolated Ćuk Converter                                    |

|------------|-----------------------------------------------------------------------------|

| Figure 5.5 | OFF state of a non-isolated Ćuk Converter                                   |

| Figure 5.6 | ON and OFF state of a Ćuk converter 60                                      |

| Figure 5.7 | Waveform of conventional Ćuk converter                                      |

| Figure 5.8 | Gain Vs Duty cycle of Conventional Ćuk63                                    |

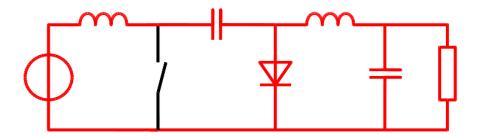

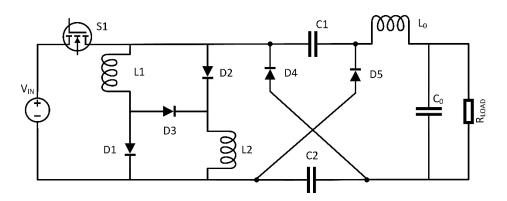

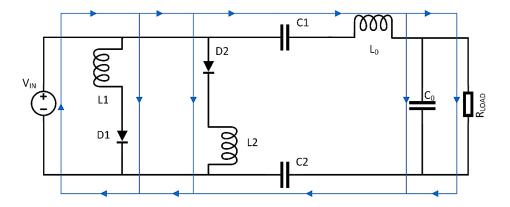

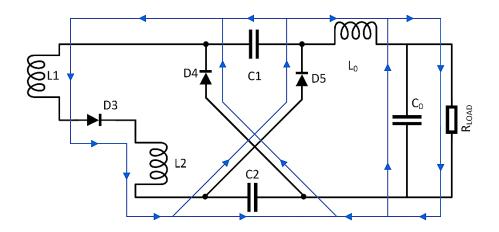

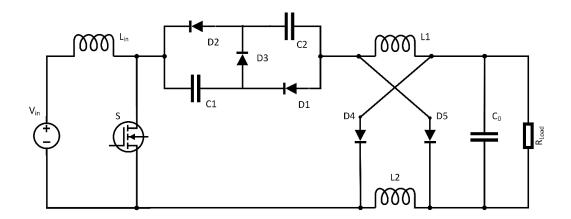

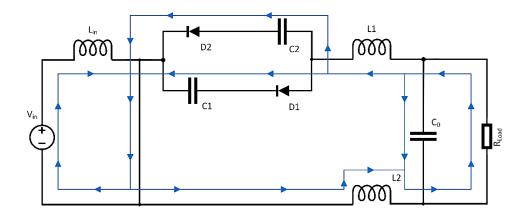

| Figure 6.1 | Proposed converter circuit                                                  |

| Figure 6.2 | Current flow during switch on state                                         |

| Figure 6.3 | Current flow during switch off state                                        |

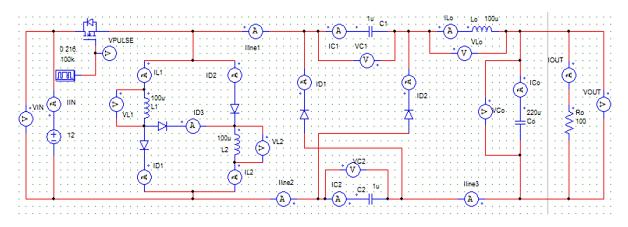

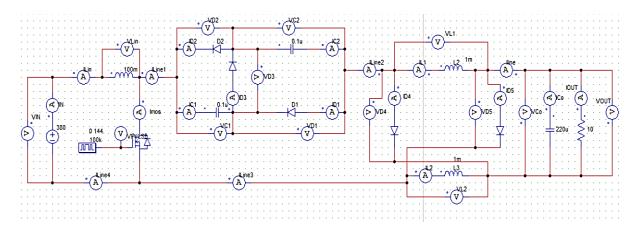

| Figure 6.4 | Snapshot of proposed circuit with ammeters & voltmeters connected in PSIM75 |

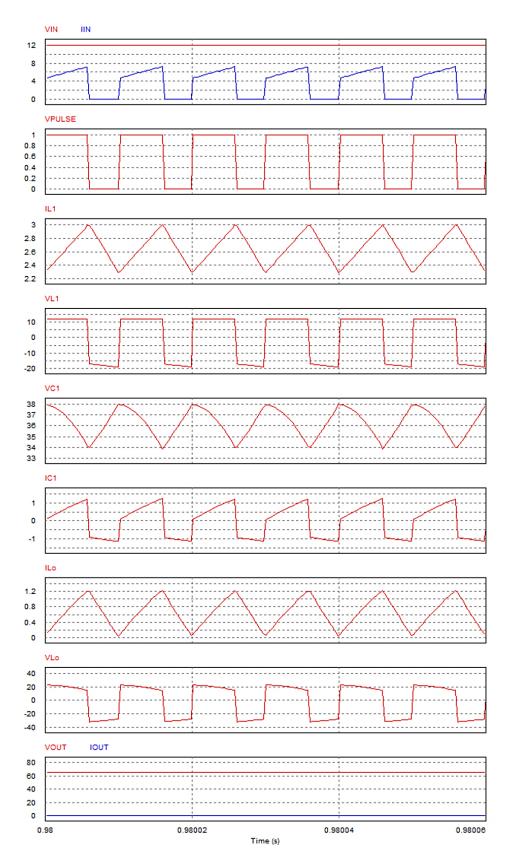

| Figure 6.5 | Voltage and Current waveforms of the proposed circuit                       |

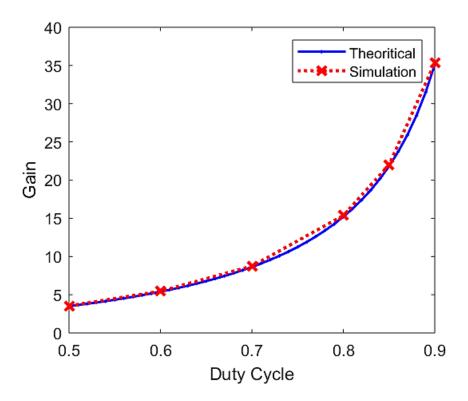

| Figure 6.6 | Graph of Theoretical and Simulated gain against duty cycle                  |

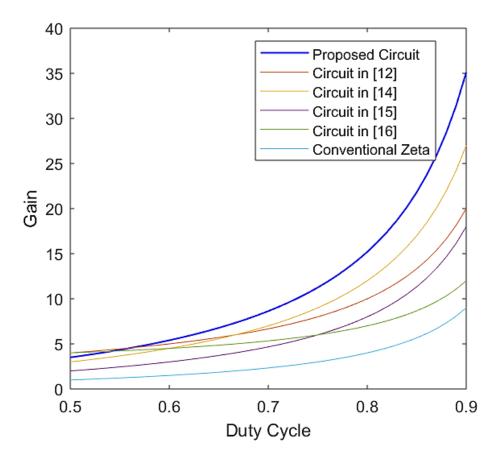

| Figure 6.7 | Gain against duty cycle comparison between existing converter               |

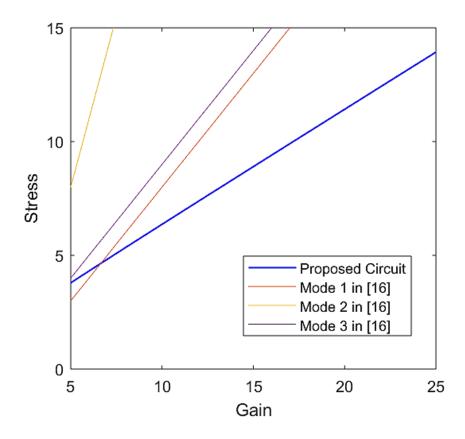

| Figure 6.8 | Graph of voltage stress against gain of proposed converter                  |

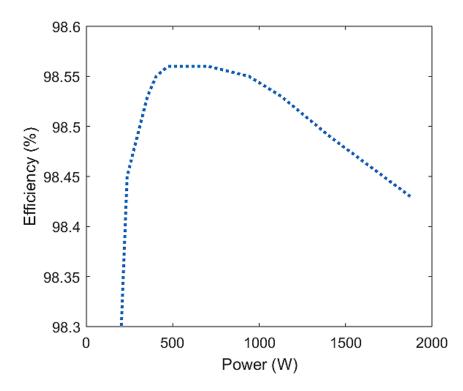

| Figure 6.9 | Converter operating efficiency at different output power 80                 |

| Figure 7.1 | Proposed converter circuit                                                  |

| Figure 7.2 | Current flow during switch on state                                         |

| Figure 7.3 | Current flow during switch off state                                        |

| Figure 7.4 | Snapshot of proposed circuit with ammeters & voltmeters connected in PSIM94 |

| Figure 7.5 | Simulated Waveforms                                                         |

| Figure 7.6 | Comparison of Theoretical and Simulated gain against duty cycle             |

| Figure 7.7 | Gain against duty cycle comparison between existing converter               |

| Figure 7.8 | Load regulation of the proposed converter circuit                           |

# List of Tables

| Table 3.1 | VOLTAGE STRESS FOR VARIOUS VMRS                                               | 24   |

|-----------|-------------------------------------------------------------------------------|------|

| Table 6.1 | THEORETICAL & SIMULATED GAIN OF PROPOSED STEP-UP CONVERTER                    | . 35 |

| Table 6.2 | VOLTAGE GAIN OF THE PROPOSED CONVERTER & OTHER EXISTING STEP-UP<br>CONVERTERS | . 77 |

| Table 6.3 | EFFICIENCY & POWER OUTPUT OF PROPOSED CONVERTER CIRCUIT                       | 78   |

| Table 6.4 | COMPARISON BETWEEN PROPOSED CONVERTER & EXISTING CONVERTER<br>CIRCUITS        | 80   |

| Table 6.5 | GAIN AND STRESS EQUATIONS OF VARIOUS CONVERTERS                               | . 81 |

| Table 7.1 | THEORETICAL & SIMULATED GAIN OF PROPOSED STEP-DOWN CONVERTER                  | 81   |

| Table 7.1 | COMPARISON BETWEEN PROPOSED AND OTHER CONVERTER                               | . 81 |

| Table 7.2 | VOLTAGE GAIN OF THE PROPOSED CONVERTER & OTHER EXISTING STEP-DOW CONVERTERS   |      |

| Table 7.3 | OUTPUT VOLTAGE & OUTPUT CURRENT OF THE PROPOSED CIRCUIT                       | 98   |

| Table 7.4 | COMPARISON TABLE OF PROPOSED CONVERTER WITH EXISTING CONVERTER CIRCUITS       | 99   |

# Acknowledgement

We would like to express our profound gratitude to our academic and research advisor Dr. Golam Sarowar, Associate Professor, Department of Electrical and Electronic Engineering at Islamic University of Technology for his continuous guidance, supervision and invaluable suggestions during the entire research work. We are extremely thankful and indebted to him for sharing expertise, and sincere and valuable guidance and encouragement extended to us. We also wish to acknowledge and express our appreciation to family, friends and mentors who directly or indirectly supported us throughout this work and helped with worthy suggestions and information in completing this thesis. Finally, we thank the Electrical and Electronic Engineering Department and its Laboratory personnel for their patient assistance during the period of the thesis work.

# Abstract

#### *Voltage Conversion Techniques: Design and Analysis of High Gain Hybrid DC-DC Converter Using SC-SL Combined Structures*

DC-DC Converter plays an important role in power electronic systems for renewable energy applications. Numerous literatures have been dedicated to improving the voltage gain of DC-DC power converters that employs various voltage boosting techniques such as using voltage multiplier cell, switched capacitor (SC), switched inductor (SL) and magnetic coupling to name a few. The objective of this work is to present and analyze two new hybrid structure that is a simultaneous combination of SC and SL structures working together to provide superior gain compared to any existing voltage up and down structure alone. The proposed structure for step up voltage conversion is applied to Zeta converter to produce a hybrid high step up Zeta converter and the proposed structure for step down voltage conversion is applied to a Ćuk converter which resulted in a hybrid high step down Ćuk converter. Both of the designed converter circuits were able to provide a theoretical and simulated voltage gain ratio up to 35 times using only one active switch and without exceeding the pulse-width modulation (PWM) duty cycle ratio of 0.9 for step up conversion and without going below 0.1 for step down conversion. Working principles of the proposed converters were described in detail and their steady state analysis in continuous conduction mode (CCM) was done to derive expressions for voltage gain, current flow through individual components, voltage and current stress on the switch and diodes. Efficiency analysis was made to derive expressions for power loss in diodes, capacitors, inductors and switch which in turn provided the total power loss and conversion efficiency of the proposed converter circuits.

# Chapter 1 Introduction

### 1.1 Background

Power electronic converters find their usage in almost all sorts of electrical and electronic device, data & telco centers, and renewable energy applications. They can be broadly grouped into four categories: AC-DC rectifiers, DC-AC inverters, AC-AC converters, DC-DC converters. DC-DC converters are further divided into three separate classes known as: buck (step down), boost (step up), buck-boost (step up-down). Power electronic converters provide an efficient and reliable way to convert source voltage levels and various other parameters according to load requirements. They enable us to utilize the generated power efficiently by regulating and altering the parameters of the input or source power and then supplying the output power with desired characteristics which can be used by the connected load. The DC-DC converter family can also be divided into categories such as classical, multi-quadrant, switched component, soft switching, synchronous rectifier and multi element resonant power converter. some voltage boosting techniques have been developed which provide for the large output utilizing a combination of switches and storage elements of the circuits. switched capacitor or charge pump (SC or CP), voltage multiplier, switched inductor and voltage lift (SL & VL), magnetic coupling, and converters with multistage or multilevel structures. Switched capacitor and switched inductor structures are mainly utilized in building the hybrid DC-DC structures that provide both step-up and step-down voltage ratios. DC-DC converters are also classified into several categories depending on their quadrant operations.

### **1.2** Motivation

Rapid advancement in the field of power electronics was made in last few decades and were driven mostly by some key factors. The most important being the increasing push towards the use of sustainable energy technologies and the integration of clean energy generation to limit global warming. Energy distribution systems based on HVDC, flexible AC transmission systems, rise of electric vehicles, fast and compact charging requirement were also some important driving factors. The improvement in battery storage technology means that more batteries are being used which in turn increases the demand of DC-DC power converters to make use of the batteries which stores voltage at a lower voltage level than load requirement. While using renewable energy sources the use of DC-DC converter becomes obvious due to the fact that the generation voltage, storage battery voltage, and the distribution voltage levels are rarely the same. Energy from renewable sources are first stored in batteries which has a voltage level in the range of 12-48V DC. This voltage is then stepped up to a level of 350-400V DC which is more convenient for transmission and distribution using power converters. Almost every electronic device or appliances used in our daily life that we take for granted have some form of power electronic circuitry in use. They could be inside a coffee maker, a medical instrument or a military equipment. Power electronic converters can take the form of an external power supply, mobile phone charger or they could be embedded inside the mobile phone itself. Wide use of the DC-DC converters makes their development to produce improved design with higher gain, better reliability and efficiency more important than ever.

# 1.3 Objective

Design a Hybrid DC-DC converter circuit with high step-up conversion based on Zeta topology:

- Use switched capacitor and switched inductor structure

- Modify and combine structures for highest voltage gain ratio

- Describe working principle of the proposed topology

Design a Hybrid DC-DC converter circuit with high step-down conversion based on Ćuk topology:

- Use switched capacitor and switched inductor structure

- Modify and combine structures for highest voltage gain ratio

- Describe working principle of the proposed topology

Perform mathematical analysis of the proposed circuits:

- Apply steady state analysis in continuous conduction mode (CCM)

- Derive expression for DC voltage gain

- Analysis of currents through each component

- Current stress analysis

- Voltage stress analysis

- Power loss and efficiency analysis

Simulation and validation of results:

- Compare between theoretical result and simulated result

- Compare obtained voltage gain between existing converter circuits

- Obtain the load regulation and voltage regulation characteristic

- Make conclusion based on the overall performance of the designed DC-DC converters.

### Chapter 2

## Brief Analysis of DC-DC Converter

### 2.1 Introduction

DC/DC converter technology is an important subject area in the field of power engineering and drives and is widely used in industrial applications and computer hardware circuits. A DC to DC converter is an electronic circuit which by electronic switching transforms a DC source voltage from one level to another.

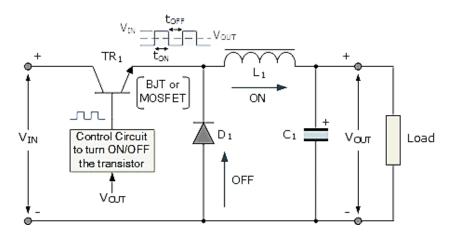

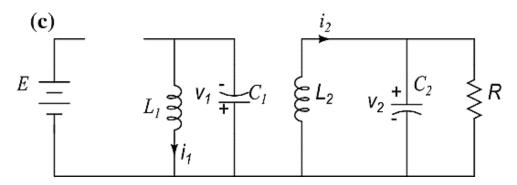

The DC-DC converter is an electrical circuit that transfers energy from a DC voltage source to a load. Electronic switches transfer energy to the energy storage devices and then subsequently switched from storage into the load. The switches are transistors and diodes; the storage devices are inductors and capacitors (Fig 2.1). This process of energy transfer results in an output voltage that is related to the input voltage by the duty ratios of the switches.

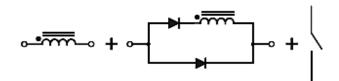

Fig 2.1: Energy Storage Device L1 & C1 in a DC-DC Converter

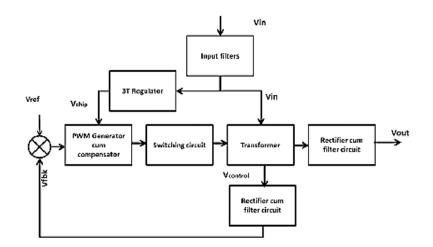

DC-DC converters use high-frequency switching and inductors, transformers, and capacitors to smooth out switching noise into regulated DC voltages. Closed feedback loops (Fig. 2.2) maintain constant voltage output. They are generally much more efficient and smaller than linear regulators.

### 2.2 Historical Review

DC/DC converters have been under rapid development for seven decades since the 1940s. In the 1940s, the buck converter was derived from the "A"-type chopper. The boost converter was derived later from the "B"-type chopper. The buck-boost converter was invented after buck converter and boost converter, and its output voltage is negative.

Fig 2.2: Basic Block Diagram of DC-DC Converter

The 1980s and 1990s are the decades called the "DC/DC conversion prosperous decades." Hundreds of DC/DC converters were invented during this period, such as Ćuk converter, single ended primary inductance converter (SEPIC), Luo converters, and soft-switching converters. Extending the developing impetus, many new types of DC/DC converters followed, such as superlift (SL) Luo-converters, cascaded boost converters, switched-capacitor converters, and synchronous rectifier (SR) converters [1].

### 2.3 DC-DC Converter Family Tree

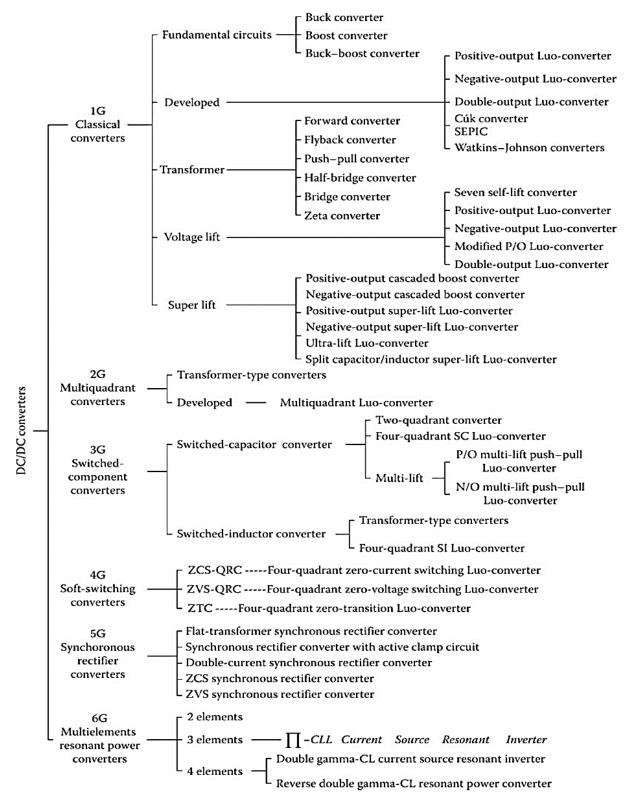

There are more than 800 topologies of DC/DC converters existing. There is a DC-DC converter family tree, which categorized all prototypes and defined the characteristics of all the existing prototypes [1].

Fig 2.3: DC-DC Converter Family Tree [1]

### 2.4 Development of DC-DC Conversion Techniques

DC-DC conversion techniques have undergone rapid development in recent decades. All existing prototypes of DC/DC converters are categorized into six generations in [Advanced DC/DC Converter]:

- First-generation (classical/traditional) converters

- Second-generation (multi-quadrant) converters

- Third-generation (switched-component: *SI/SC*) converters

- Fourth-generation (soft-switching: ZCS/ZVS/zero-transition [ZT]) converters

- Fifth-generation (SR) converters

- Sixth-generation (multiple-energy-storage-element resonant [MER]) converters

### 2.4.1 Classical Converters

Classical converters perform in a single-quadrant mode and in a low power range (up to around 100 W). Since their development lasts a long time, they have, briefly, five categories:

- A. Fundamental converters

- B. Transformer-type converters

- C. Developed converters

- D. Voltage-lift (VL) converters

- E. Super-Lift (SL) converters

#### A. Fundamental converters:

Three types of fundamental DC/DC topologies were constructed: *buck* converter, *boost* converter, and *buck-boost* converter. They can be derived from single-quadrant operation choppers.

Fig 2.4: Conventional Buck Converter circuit diagram

#### **Buck Converter:**

Buck converter is a step-down DC/DC converter in (Fig 2.4) which works in firstquadrant. It can be derived from quadrant I chopper. The diode is replaced with a second Transistor in modern Buck converter. There is at least one energy storage element. The output voltage is calculated by the formula:

$$V_o = \frac{t_{on}}{T} V_{in} = D V_{in} \tag{2.1}$$

#### **Boost Converter:**

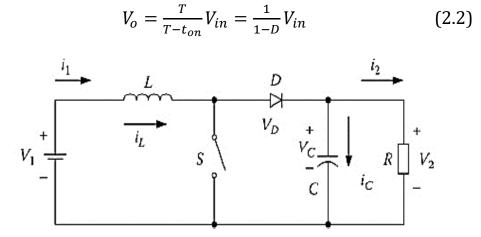

Boost converter is a step-up DC/DC converter in (Fig 2.5). It works in second-quadrant operation. It can be derived from quadrant II chopper. A filter is added to the output to reduce voltage ripple. The output voltage is calculated by the formula:

Fig 2.5: Conventional Boost Converter circuit diagram

#### **Buck-Boost Converter:**

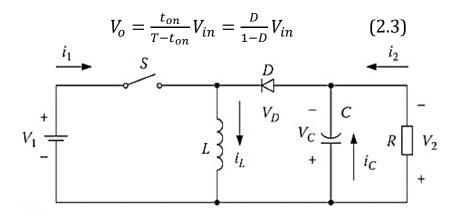

Buck-boost converter is a step-down/step-up DC/DC converter. It works in thirdquadrant operation. There are Two Topology for buck boost converter. The inverting topology and the 4 Switch topology. The output voltage is calculated by the formula:

Fig 2.6: Conventional Buck Boost Converter circuit diagram

#### B. Transformer-type converters:

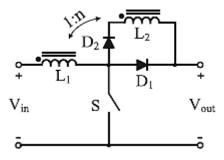

There is a linkage between the input side and the output side in the Fundamental DC/DC converters. That's why the voltage transfer gain is comparably low. To remove this problem one transformer is introduced in between. There are large number of converters such as *forward* converter. *push-pull* converter, *flyback* converter, *half-bridge* converter, *bridge* converter, and *Zeta* (or *ZETA*) converter use transformers.

#### Forward converter:

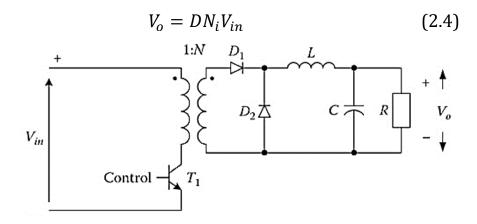

Forward converter in (Fig 2.7) is a transformer-type buck converter with the turns ratio *N*, which works in first quadrant operation. Some industrial applications require multiple outputs. For this requirement there are multiple secondary windings and the corresponding conversion circuit available. The output voltage is calculated by the formula:

Fig 2.7: Forward Converter circuit diagram.

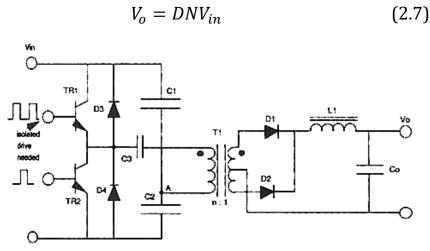

#### **Push-Pull Converter:**

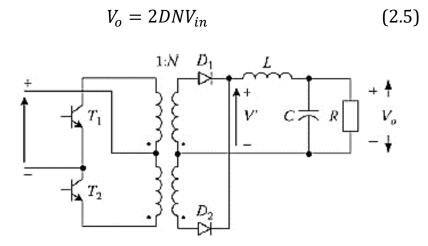

Boost converter works in a push-pull state, which effectively avoids the iron core saturation. A simple Push-Pull Converter with fixed 50% duty cycle is often used as a low noise transformer driver and distributed power supplies. There are two switches in the converter working alternatively. For this reason, the output voltage is doubled. The circuit diagram is depicted in (Fig 2.8). The output voltage is calculated by the formula:

Fig 2.8: Push Pull Converter circuit diagram.

#### **Fly-back Converter:**

Fly-back converter in (Fig 2.9) is a transformer-type converter using the demagnetizing effect. The Fly-back converter is a buck boost converter with the inductor is replaced by a transformer. So the voltage ratios are multiplied with an additional advantages of isolation. The output voltage is calculated by the formula:

Fig 2.9: Fly Back Converter circuit diagram.

#### Half-Bridge Converter:

The half-bridge converter was constructed to reduce the primary side in one winding by replacing the center tapped transformer with traditional transformer.

It removes the Flux Unbalanced problem of the Push Pull Converter. It uses two input switches to control the output. And it also uses two sets of diodes and two bulk capacitors which increases the efficiencies to the 90% range. The output voltage is calculated by the formula:

Fig 2.10: Half Bridge Converter circuit diagram.

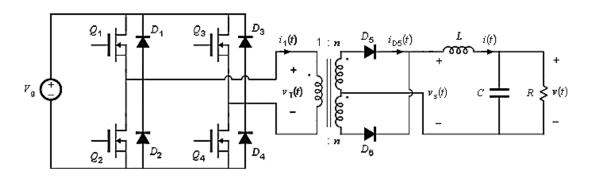

#### Full-Bridge Converter:

Bridge converter is a DC - DC converter which employs four active switching components in a bridge configuration for control the output voltage. Therefore, gains of this converter is double. It also provides multiple output voltages simultaneously. The output voltage is calculated by the formula:

$$V_o = 2DNV_{in} \tag{2.8}$$

Fig 2.11: Full Bridge Converter circuit diagram.

#### C. Developed converters:

In order to overcome the second fault of the fundamental DC/DC converters, Developedtype converters add a low-pass filter to reduce the output voltage ripple. The typical converters are Positive Output *Luo*-converter, negative-output *Luo*-converter, doubleoutput *Luo*-converter, Ćuk converter, *SEPIC*, and Watkins-Johnson converter. Developed converters can obtain output voltage higher or lower than the input voltage which means these converters can act as buck boost converter.

#### Positive Output Luo-converter:

Positive Output (P/O) Luo-converter is the elementary circuit of the series of new DC-DC step up converters that uses voltage lift technique. It can be derived from buck-boost converter. The output voltage is calculated using formula:

Fig 2.12: Positive Output Luo Converter circuit diagram

#### Negative-output *Luo*-converter:

Negative-output (N/O) Luo-converter is the elementary circuit which can also be derived from buck-boost converter. The output voltage is calculated using formula:

Fig 2.13: Negative Output Luo Converter circuit diagram

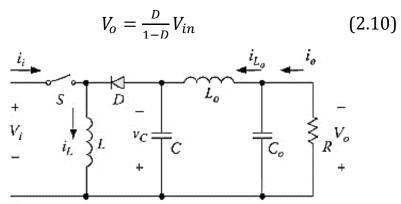

#### **Double-output** *Luo*-converter:

In order to obtain mirror symmetrical P/O and N/O voltage, D/O Luo-converter was constructed. D/O Luo-converter is the elementary circuit of the series "D/O Luo-converters." The output voltage is calculated using formula:

$$V_o = \frac{D}{1-D} V_{in} \tag{2.11}$$

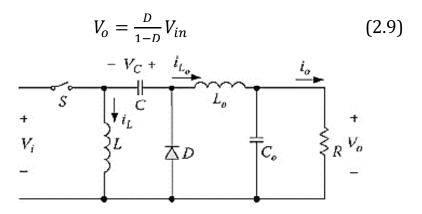

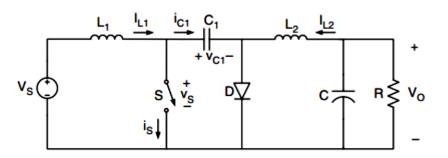

#### **Ćuk converter:**

Ćuk converter is derived from boost converter. It has a output voltage magnitude either greater than or less than the input voltage. The output voltage is calculated using formula:

$$V_o = \frac{D}{1 - D} V_{in}$$

(2.12)

Fig 2.14: Ćuk Converter circuit diagram.

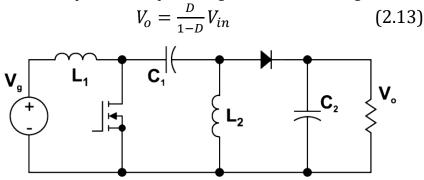

#### **SEPIC Converter:**

The *SEPIC* or single ended primary-inductor converter is a DC-DC converter which can be derived from boost converter. It allows the voltage at its output voltage is greater than, less than or equal to its input. The output voltage is calculated using formula:

Fig 2.15: SEPIC circuit diagram

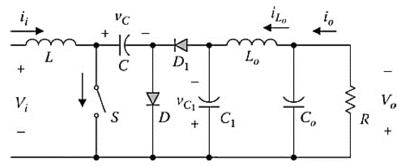

#### D. Voltage-lift (VL) converters:

VL technique is a good method to lift the output voltage. It is widely applied in electronic circuit design. The voltage lift circuit has been successfully applied to several series of DC-DC converters. Using this Voltage lift method, the output voltage can be easily lifted by tens to hundreds of times. VL converters can be classed into *self-lift, re-lift, triple-lift, quadruple-lift*, and *high-stage-lift* converters. Here's an example of self-lift Ćuk Converter in Fig 2.16.

Fig 2.16: Self lift Ćuk Converter circuit diagram.

#### E. Super-lift (SL) converters:

VL technique is a popular method that is widely used in electronic circuit design. It has been successfully employed in DC/DC converter applications in recent years and has opened a way to design high-voltage-gain converters. Three-series Luo-converters are examples of VL technique implementations. However, the output voltage increases stage by stage just along the arithmetic progression. A novel approach—SL technique—has been developed, which implements the output voltage increasing stage by stage along in geometric progression. It effectively enhances the voltage transfer gain in power law. The typical circuits are sorted into five series: P/O *SL Luo-converters*, N/O *SL Luo-converters*, P/O *cascaded boost converters*, N/O *cascaded boost converters*, and *ultra-lift Luo-converters*. Here's an example of Positive Output Super Lift Luo Converter:

Fig 2.17: Positive Output Super Lift Luo Converter Circuit Diagram.

### 2.4.2 Multi-quadrant Converters:

Multiple-quadrant converters perform in two-quadrant operation and four-quadrant operation with medium output power range. The topologies can be sorted into two main categories:

- First are the converters derived from the multiple-quadrant choppers and/or from the first-generation converters and

- Second are constructed with transformers.

Multiple quadrant choppers were employed in industrial applications for a long time. They can be used to implement the DC motor multiple-quadrant operation. These converters are derived from multi-quadrant choppers, for example, class-B converters are derived from B-type choppers and class-E converters are derived from E-type choppers.

- ✓ The class-B converter works in quadrant I and II operation, which corresponds to the forward-running motoring and regenerative braking operation of a DC motor drive.

- ✓ The class-C converter works in quadrant I and VI operation.

- ✓ The class-D converter works in quadrant III and VI operation, which corresponds to the reverse-running motoring and regenerative braking operation of a DC motor drive.

- ✓ The class-E converter works in four-quadrant operation, which corresponds to the four-quadrant operation of a DC motor drive.

Multi-quadrant operation converters can be derived from the first-generation converters. For example, multi-quadrant Luo-converters are derived from P/O Luo-converters and N/O Luo-converters. The transformer-type multi-quadrant converters easily change the current direction by transformer polarity and diode rectifier. The main types of such converters can be derived from the *forward* converter, *half-bridge* converter, and *bridge* converter.

Fig 2.18: Multi-quadrant Luo Converter Circuit Diagram.

### 2.4.3 Switched-component (*SI/SC*) converters:

The third-generation converters are called switched-component converters and are made of either inductors or capacitors, the so-called switched inductor and switched capacitors. They can perform in two- or four-quadrant operation with high output power range.

#### 1. Switched capacitors (SC) converters:

Switched-capacitor DC/DC converters consist of only capacitors. Because there is no inductor in the circuit, their size is small. They have outstanding advantages such as low power losses and low electromagnetic interference. The switched capacitor can be integrated into an integrated chip (IC). Hence, its size is largely reduced. most of the converters in the literature perform a single-quadrant operation. Some of them work in the push-pull status. In addition, their control circuit and topologies are very complex, especially for the large difference between input and output voltages.

Fig 2.19: Positive Output Push Pull Switched Capacitor Luo Converter circuit diagram.

#### 2. Multiple-Quadrant Switched-Capacitor Luo-Converters:

Switched-capacitor DC/DC converters consist of only capacitors. Since their power density is very high, they are widely applied in industrial applications. Some industrial applications require multiple-quadrant operation, so multiple-quadrant switched-capacitor Luo-converters have been developed. There are two-quadrant operation types and four-quadrant operation types.

#### 3. Multiple-Lift Push-Pull Switched-Capacitor Converters:

VL technique is a popular method widely used in electronic circuit design. It has been successfully employed in DC/DC converter applications in recent years and has opened a way to design high voltage- gain converters. Three-series Luo-converters are examples of VL technique implementation. However, the output voltage increases stage by stage just along the arithmetic progression. A novel approach—multiple-lift push-pull technique—has been developed, which implements the output voltage, which increases stage by stage along the arithmetic progression. It

effectively enhances the voltage transfer gain. The typical circuits are sorted into two series: *P/O multiple-lift push-pull switched-capacitor Luo-converters* and *N/O multiple-lift push-pull switched-capacitor Luo-converters*.

#### 4. Switched-Inductor Converters:

The switched capacitors have many advantages, but their circuits are not simple. If the difference of input and output voltages is large, many capacitors are required. The switched inductor has the outstanding advantage that only one inductor is required for one switched-inductor converter no matter how large the difference between input and output voltages is. This characteristic is very important for large power conversion.

Fig 2.20: Four Quadrant Switched Inductor DC/DC Luo Converter circuit diagram.

### 2.4.4 Soft-switching (*ZCS/ZVS*) converters:

The fourth-generation DC/DC converters are called soft-switching converters. There are four

types of soft-switching methods:

- 1. Resonant-switch converters

- 2. Load-resonant converters

- 3. Resonant-DC-link converters

- 4. High-frequency-link integral-half-cycle converters

This resonance method is available for working independently to load. There are three main categories: ZCS, ZVS, and ZT converters. Most topologies usually perform in singlequadrant operation in the literature. Actually, these converters can perform in two- and four-quadrant operation with high output power range.

ZCS and ZVS converters have three resonant states: over-resonance (completed resonance), optimum-resonance (critical resonance), and quasi-resonance (sub-resonance). Only the quasi-resonance state has two clear zero-cross points in a repeating period.

#### 1. ZCS-QRCs:

ZCS-QRC equips resonant circuit in the switch side to keep the switch-on and switch-off at zero current condition. There are two states: full-wave state and half-wave state. Most of the engineers enjoy the half-wave state. This technique has half-wave current resonance waveform with two zero-cross points.

Fig 2.21: DC-DC Zero Current Switching Quasi Resonant Luo Converter for quadrant I and quadrant II

#### 2. ZVS-QRCs:

ZVS-QRC equips resonant circuit in the switch side to keep the switch-on and switch-off at zero voltage condition. In Fig 2.22 there are two states: full-wave state and half-wave state. Most of the engineers enjoy the half-wave state. This technique has half-wave voltage resonance waveform with two zero-cross points.

Fig 2.22: DC-DC Zero Voltage Switching Quasi Resonant Luo Converter for quadrant I and quadrant II

#### 3. ZT Converters:

Using ZCS-QRC and ZVS-QRC largely reduces the power losses across the switches.

Consequently, the switch device power rates become lower and converter power efficiency is increased. However, ZCS-QRC and ZVS-QRC have large current and voltage stresses. Therefore, the device's current and voltage peak rates usually are three to five times higher than the working current and voltage. It is not only costly but also ineffective. ZT technique overcomes this fault. It implements zero-voltage plus ZCS technique without significant current and voltage stresses.

Fig 2.23: Zero-transition DC/DC Luo-converters for quadrant I and quadrant II

### 2.4.5 Synchronous Rectifier Converters or Fifthgeneration converters:

Corresponding to the development of the micro-power consumption technique and highdensity IC manufacture, the power supplies with low output voltage and strong current are widely used in communications, computer equipment, and

other industrial applications. Inter-80 computers used the 5 V power supply. In order to increase the memory size and operation speed, large-scale integrated chip technique has been quickly developed. As the amount of IC manufacturing increased, the gaps between the layers became narrower. At the same time, the micropower consumption technique was completed. Therefore, new computers, such as those using Pentium I, II, III, and IV, use a 3.3 V power supply. Future computers will have larger memory and will require lower power supply voltages, for example, 2.5, 1.8, 1.5, and even 1.1 V. The fundamental topology is derived from the forward converter. Active-clamped circuit, flat transformers, double-current circuit, soft-switching methods, and multiple-current methods can be used in SR DC/DC converters.

# 2.4.6 Multiple-energy-storage-element resonant [*MER*] power converters:

Current source resonant inverters are the heart of many systems and equipment, for example, uninterruptible power supply and high frequency annealing apparatus. Many topologies shown in the literature are the series resonant converters and parallel resonant converters that consist of two or three or four energy-storage elements. However, they have limitations. These limitations of two-, three-, and/or four-element resonant topologies can be overcome by special design. These converters have been categorized into three main types:

- Two-energy-storage-element resonant DC/AC and DC/AC/DC converters

- Three-energy-storage-element resonant DC/AC and DC/AC/DC converters

- Four-energy-storage-element (2L-2C) resonant DC/AC and DC/AC/DC converters

there are 8 prototypes of two-element converters, 38 prototypes of three-element converters, and 98 prototypes of four-element (2L-2C) converters.

### Chapter 3

### **Voltage-Boosting Techniques**

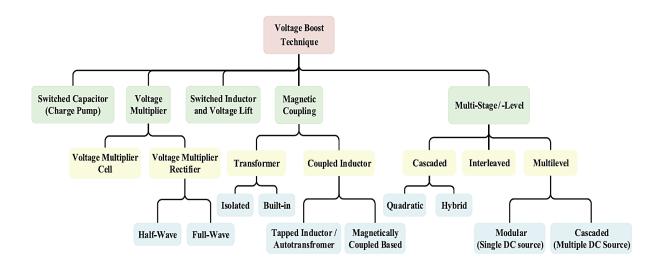

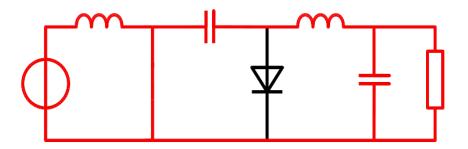

Power electronic converter employs various voltage-boosting techniques for dc-dc step up conversion of voltage levels. The boosting techniques can be broadly categorized into five major sections named as: switched capacitor or charge pump (SC or CP), voltage multiplier, switched inductor and voltage lift (SL & VL), magnetic coupling, and converters with multistage or multilevel structures [2]. The boosting techniques are shown in Fig.3.1. The general structures of each technique are first illustrated and then described in the subsequent sections.

Figure 3.1: Broad categorizations of voltage boost techniques used for dc-dc converters [2]

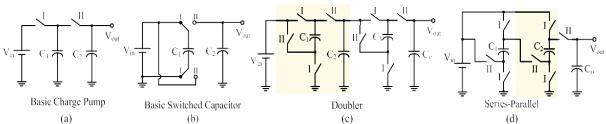

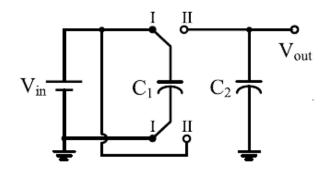

### 3.1. Switched Capacitor (Charge Pump)

Switched Capacitor (SC) is one of the popular implementations of Charge Pump (CP) circuit. The SC voltage boosting technique is entirely based on CP circuit. Fig.3.2 shows some basic charge pump and switched capacitor circuits. Fig. 3.2(a) shows a schematic CP circuit, in which two switches are turned ON and OFF in succession. When switch I is turned ON, capacitor C1 charges to the input voltage level, and when switch II is turned ON, the stored energy in C1 transfers to capacitor C2 and the switches are phased alternately (odd-numbered switches (I) in phase 1, even numbered switches (II) in phase 2). This process is called pumping the energy from one capacitor to another [3]-[6].

Fig.3.2: Basic charge pump and switched capacitor circuits. (a) Basic charge pump. (b) Basic switched capacitor. (c) Doubler. (d) Series-parallel. (e) Ladder. (f) Dickson. (g) Makowski or Fibonacci.

Output voltage level can be doubled by the two-phase SC voltage doubler (TPVD) shown in Fig.3.2(b). First the capacitor C1 is charged to the input voltage then the capacitor C1 is placed in series with the input source, which doubles the output voltage level [7] TPVD can be connected in series for higher voltage gains as shown in Doubler SCs in Fig. 3.2(c). Series–parallel SC as shown in Fig. 3.2(d) use capacitors efficiently, as the capacitors in this topology are at the same voltage [8].

Main issue related to SC circuits is their high-current transients, which have a degrading effect on both power density and efficiency. One way to prevent the detrimental effects of current transients in SC circuits is to insert an inductor at the output in order to form a buck converter with the existing switch(es). This technique has the two advantages of providing efficient regulation and eliminating current transients, which together are known as the soft-charging of SC converters [9].

### 3.2. Voltage Multiplier

Voltage multipliers can be divided into two major groups from a structural point of view: 1) the in-circuit VMC, which can be implemented in the middle of a circuit usually after the main switch, in order to reduce voltage stress; and 2) the voltage multiplier rectifier (VMR), which is placed at the output stage of transformer- and coupled-inductor-based structures in order to rectify ac or pulsating dc voltage while acting as a voltage multiplier.

### 3.2.1. Voltage Multiplier Cell

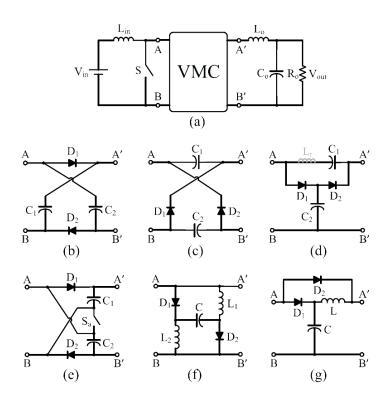

Some generic voltage multiplier cell topologies are shown in Fig. 3.3. Some of these cells consist only of diodes and capacitors [Fig.3.3 (b)–(d)] and hence are known as switched/diode capacitor VMCs [10]-[12]. Other VMCs have more components, such as an auxiliary switch as in Fig.3.3(e), while some use inductors to increase the voltage-boosting ratio as in Fig.11(f) and (g) [13]-[14].

Fig.3.3: (a) General topological view of the placement of voltage multiplier cells in step-up converters. (b)–(g) Various voltage multiplier cells.

All of the converters using VMCs shown in Fig. 3.3 operate by switching the main switch (S), with the exception of the VMC in Fig. 3.3(e), in which the boost converter operates only with the switch Sa of the VMC. The VMC in Fig. 3.3(f) uses a capacitor and inductors to increase the boost factor of the converters [13]. The VMC in Fig. 3.3(g) is typically inserted before the main switch to increase the voltage level of very low voltage sources (under50 V). This VMC has been used in various ultra-step-up dc-dc converters [10].

### 3.2.2. Voltage Multiplier Rectifier

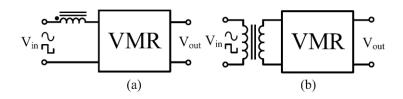

This group consist solely of different configurations of diodes and capacitors and are commonly referred to as voltage multipliers. VMRs can be further grouped into half wave VMRs and full wave VMRs. General topological view of the placement of VMR is shown in Fig. 3.4.

Figure 3.4: General topological view of the placement of VMRs (a) at dc pulsating output and (b) at ac output

#### A) Half Wave:

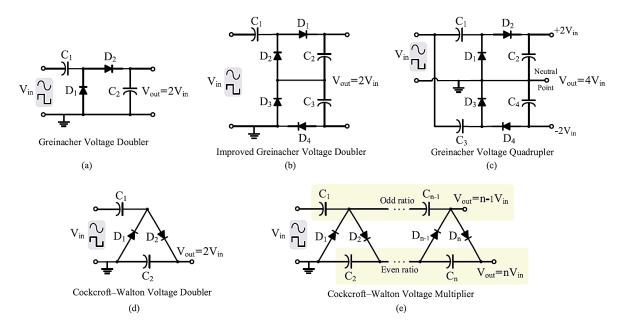

these circuits are not confined to the secondary side of isolated transformers and coupled inductors but can also be used in converters with built-in transformers and coupled inductors. Fig. 3.5(a) shows a Greinacher voltage doubler rectifier (G-VDR) which used at the output stage of many transformer-based dc-dc converters [15]. Fig. 3.5(b) shows an improved version of the G-VDR [16]. The advantage of this VMR is that the voltage stresses of all components are half of the output voltage; this allows for the use of lower voltage rating components than in conventional VMRs, which in turn leads to low-power loss and high efficiency. Fig. 3.5(c) shows a Greinacher voltage quadrupler rectifier formed by connection of one normal and one inversed G-VDR. The advantage of this VMR is that it can provide a neutral point terminal, which is necessary for half bridge-based transformer-less inverters [17]. Another well-known voltage multiplier is the Cockcroft–Walton (CW). CW-VMRs, as shown in Fig. 3.5(d), are popular for their simple cascading structures that can provide high-voltage level [18].

| Voltage Multiplier<br>Rectifier (VMR)  | Output Voltage<br>(V <sub>out</sub> ) | Output Diode<br>Voltage Stress | Output Capacitor<br>Voltage Stress |

|----------------------------------------|---------------------------------------|--------------------------------|------------------------------------|

| Greinacher Voltage<br>Doubler          | 2 V <sub>in</sub>                     | Vout                           | Vout                               |

| Improved Greinacher<br>Voltage Doubler | 2 V <sub>in</sub>                     | $\frac{V_{out}}{2}$            | $\frac{V_{out}}{2}$                |

| Greinacher Voltage<br>Quadrupler       | 4 V <sub>in</sub>                     | $\frac{V_{out}}{2}$            | $\frac{V_{out}}{2}$                |

| Cockcroft-Walton<br>Voltage Multiplier | n V <sub>in</sub>                     | Vout                           | V <sub>out</sub>                   |

TABLE 3.1: VOLTAGE STRESS FOR VARIOUS VMRS

Figure 3.5: Various half-wave VMRs. (a) Greinacher voltage doubler. (b) Improved Greinacher voltage doubler. (c) Greinacher voltage quadrupler. (d) CW voltage doubler. (e) CW voltage multiplier.

#### **B)** Full Wave:

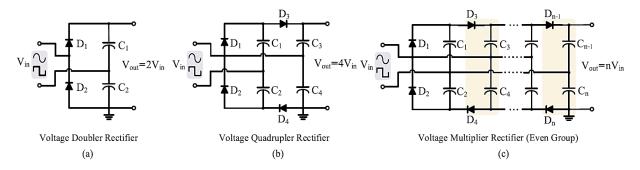

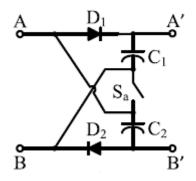

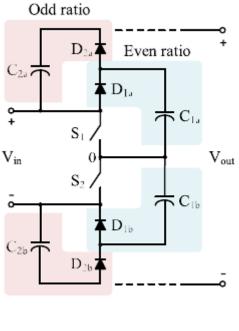

Full-wave VMRs, another well-known type of independent boosting stage, are commonly employed at the output stage of transformer-based converters. Fig. 3.6 illustrates some basic and generalized structures for even and odd voltage multiplier groups. The VMR in Fig. 3.6(a) is a full-bridge voltage doubler rectifier that, owing to its reduced voltage stress on output capacitors (it reduces the output voltage by one-half), is commonly used in various dc–dc converters [19]-[23]. The VMR in Fig. 3.6(b) is a quadrupler voltage rectifier that is considered to be a useful boosting stage in modern dc–dc converters owing to its balanced voltage stress on both capacitors and diodes [24]-[25]. Fig. 3.6(c) shows a multi stage structure consisting of the VMRs in Fig. 3.6(a) and (b) (even group) [26].

Figure 3.6: Various full-wave VMRs. (a) Voltage doubler rectifier. (b) Voltage quadrupler rectifier. (c) VMR (even group)

### 3.3 Switched Inductor and Voltage Lift

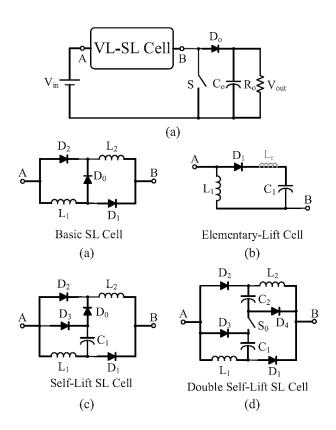

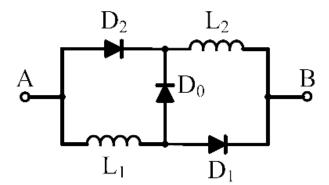

Voltage lift switched inductor (VL-SL) cells are shown in Fig. 3.7, with a typical placement of these cells in a step-up dc–dc converter shown in Fig. 3.7(a). The basic SL cell depicted in Fig. 3.7(b) was first introduced in [11]. In an SL cell, the inductors are magnetized in parallel and demagnetized in series. As both inductors have the same inductance value and operational condition, they can be integrated into a single core in order to reduce the size and weight of the converter. The elementary circuit of a VL circuit is shown in Fig.15(c).

Implementing an elementary VL cell in an SL cell produces the so-called self-lift SL cell, as shown in Fig. 3.7(d). Adding another diode and capacitor to a self-lift SL cell produces a double self-lift SL cell, as shown in Fig. 3.7(e) [27]. In a double self-lift SL cell, SO is used instead of D0 in a basic SL cell with switching operation complementary to the switch S in Fig. 3.7(a).

Figure 3.7: Voltage lift cells. (a) General placement of the voltage lift cell in step- up converters. (b)–(e) Various voltage lift switched inductor cells. [(a) Basic SL cell. (b) Elementary-lift cell. (c) Self-lift SL cell. (d) Double self-lift SL cell.]

## 3.4 Magnetic Coupling

Magnetic coupling is a popular voltage-boosting technique that is used in both isolated and nonisolated dc–dc converters. Using a coupled inductor reduces the number of magnetic cores, which are often the bulkiest components in the layout. Despite benefits such as dominant boost ability, utilization of magnetic coupling is often incurring drawbacks such as leakage inductance that may require consideration in terms of recycling the leakage energy. In this section, the various transformer-based boost techniques, as well as the inductor coupling technique, are presented.

### 3.4.1 Transformer

Transformer-based dc-dc converters are the subject of increasing research interest as the transformer turns ratio provides an additional degree of design freedom that, along with the duty cycle, can be manipulated to achieve high- voltage boost ability. Transformer converters can be broken into two types: isolated transformers, which are used to electrically isolate dc-dc converters; and nonisolated dc-dc converters de- rived from isolated converters, which are known in the literature as built-in transformers. Although their underlying circuit theories are similar; however, the performance differs by type.

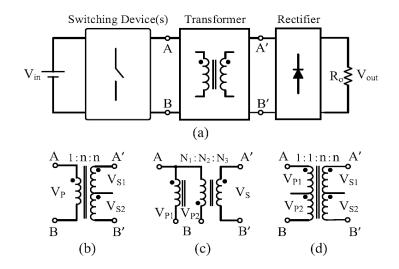

### A) Isolated Transformer:

Fig. 3.8(a) shows a schematic of a basic transformer-based converter with an input dc source followed by a network of switches, diodes, and transformer that is then rectified and connected to an output filter. There are several common types of isolation transformers that can be incorporated into dc–dc converters according to their switching network layouts [28]-[29]. Full- and half-bridge converters typically use a transformer of the type shown in Fig. 3.8(b), in which one or two windings in the secondary (depending on the rectifier circuit) are used to step-up the primary voltage. One type of buck-based converter called the forward converter incorporates a three-winding transformer, as shown in Fig. 3.8(c). Push-pull based converters typically use a multi-winding transformer, as shown in Fig. 3.8(d), in which the two windings in the primary (each one activating in a switching state) are followed by one or two windings in the secondary (depending on the rectifier circuit).

Figure 3.8: Isolated dc-dc converters. (a) General layout of basic transformer- based converters. (b) Full bridge/half bridge. (c) Forward. (d) Push-pull

#### **B)** Built-in Transformer:

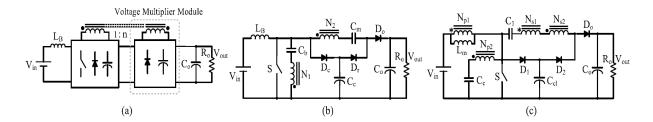

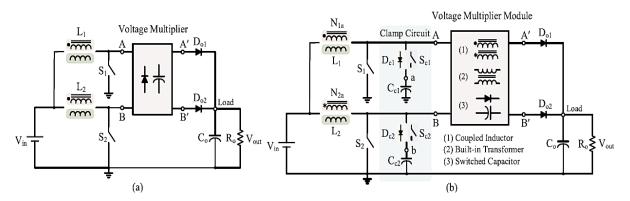

Some examples of general built-in transformer-based converter structures are shown in Fig. 3.9. The primary side of such converters usually consists of switched networks to generate pulsating dc voltage, while the secondary side usually consists of SCs voltage multiplier modules [30]–[33]. In addition to the transformer shown in these circuits, various voltage multiplier circuits are used to further increase the voltage gain and reduce the built-in transformer turns ratio.

Figure 3.9: Step-up dc–dc converter consisting of built-in transformer concept. (a) General layout with the horizontal structure. (b) Comprising voltage multiplier. (c) Comprising both coupled inductor and built-in transformer.

### 3.4.2 Coupled Inductor

Coupled inductors are a valuable component of nonisolated dc-dc converters that store energy in one cycle and power the load in the other cycles. As many applications do not require electrical isolation, the use of coupled inductors provides a helpful alternative boosting technique in dc-dc converters that can be achieved by tapping or simply coupling the inductors.

#### A) Tapped inductor/autotransformer:

Tapped circuits can be categorized into three types: switched-tapped, diode-tapped, and rail-tapped. Fig. 3.10(a) shows the general configuration of a tapped-inductor boost dc–dc converter [34]-[35]. Switch tapping occurs by connecting A to 1, B1 to 2, and C to 3. Diode- tapping is obtained by connecting A to 1, B1 to 3, and C to 2. Finally, the circuit can be rail-tapped by connecting A to 3, B2 to 2, and C to 1.

Parasitic analysis shows that the gain voltage and efficiency of tapped inductor boost converters can be theoretically higher than that of PWM boost dc–dc converters. On the other hand, as the root mean square (RMS) current of the switches, RMS current of inductors, and diode-blocking voltages all increase when inductor tapping is utilized [36], designing a clamp/snubber circuit is sometimes necessary [34], [37]. Another advantageous use of tapped inductors is obtaining input current ripple cancellation in a PWM boost dc–dc converter, as demonstrated in [38].

Figure 3.10: Tapped-inductor based converters. (a) General configuration of a tapped inductor boost converter and (b) double-tapped inductor boost converter

#### B) Magnetically coupled-based converters:

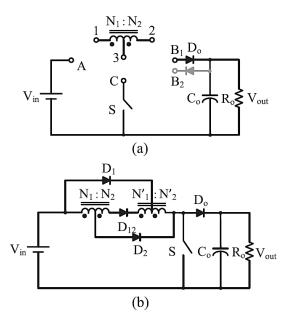

Fig. 3.11 shows the general configuration of a coupled-inductor-based boost converter. A basic coupled-inductor boost converter is shown in Fig. 3.12(a). The secondary winding acts as a voltage source in series with the power branch, while the clamp capacitor Cc and diode Dc are used to recover leakage energy. The clamp capacitor can be shifted within the circuit. The clamping function is similar in all placements and the leakage energy can be effectively recycled directly or through the secondary winding to the load [39].

Figure 3.11: General layout of the coupled-inductor-based step-up converter.

Figure 3.12: Coupled-inductor-based circuits. (a) Basic coupled inductor. (b) Switched coupled inductor. (c) Coupled inductor with active clamp. (d) Coupled inductor with a snubber circuit.

# 3.5 Multistage/ Multilevel

One well-known method for increasing the voltage gain of a dc-dc converter is to employ several stages of converter modules connected in various ways. This can be realized by implementing several identical/different converter modules combined with various voltage-boosting techniques. In this subsection, cascaded, interleaved, and multilevel converter topologies and their sub groups are presented. The voltage gain in multistage/ multilevel structures increases linearly or exponentially (often multiplicatively by number of stages) as a function of the topology used.

### 3.5.1 Cascaded

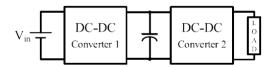

Cascading connection of converters is a simple approach for increasing voltage gain. Fig. 3.13 shows general layout of a cascaded dc–dc converter [40]. According to the depicted scheme, two or more boost converters can be connected in cascaded form (called a quadratic group) or different types of step-up converters can be connected in cascaded form (called a hybrid group).

Figure 3.13: General layout of the cascaded dc-dc converter.

### A) Quadratic Boost:

Fig. 3.14(a) shows a cascaded boost converter consisting of two boost converters in cascaded form [41]. To reduce the circuit complexity, the switches of the cascaded boost converter can be integrated into one switch. In a structure called a quadratic boost converter [42]. The configuration of a quadratic boost converter is shown in Fig. 3.14(b). Moreover, quadratic boost converters are advantageous for low-power applications where sophisticated magnetic designs are avoided.

Figure 3.14: Quadratic dc–dc converters. (a) Two cascaded boost converters. (b) Quadratic boost converter.

#### **B)** Hybrid cascaded:

In this subsection, two types of cascaded converters are introduced: quadratic boostbased converters with auxiliary circuits, and hybrid connections of two different types of dc-dc converters. Fig. 3.15 shows the general structure of a hybrid cascaded two different dc-dc converter.

Figure 3.15: General layout of the cascaded connection of two different converters.

### 3.5.2 Interleaved

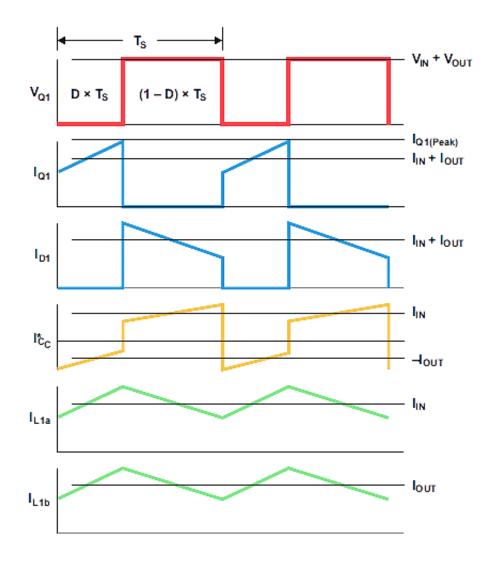

In step-up dc-dc converters, the input cur- rent level is higher than the output current level. As such, the multiphase interleaving technique is a promising solution for decreasing the current ripple and increasing the power density in high step-up dc-dc converters. Fig. 3.16(a) shows a schematic of a two-phase interleaved boost converter. In addition to zero reverse-recovery of output diodes, an interleaved boost converter with coupled input inductors has lower current ripple and a smaller switching duty cycle than a normal boost [43]. Fig. 3.16(b) shows a schematic of a two-phase interleaved step-up dc-dc converter with passive/active clamp circuits and a voltage multiplier module (coupled inductor or transformer, SC) between the input switches and output diodes to increase the voltage step-up gain.

Figure 3.16: Interleaved dc–dc converters. (a) and (b) General layouts of interleaved step-up converters

### 3.5.3 Multilevel

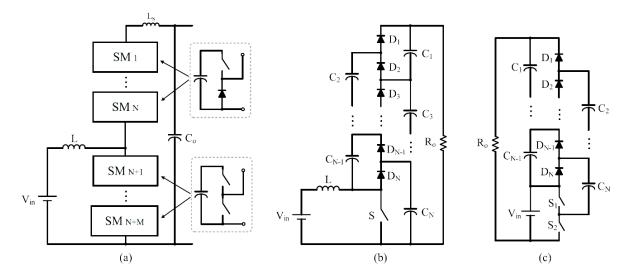

Useful in high-power high-voltage applications. Multilevel converters in a dc–dc structure can help to decrease or almost eliminate magnetic components, which leads to reduced converter size and weight [44]-[46]. From the input voltage view, multilevel dc– dc converters can be divided into two major types: multilevel converters with a single dc or multiple dc sources. Single-source multilevel modular structures are of interest for use in electric vehicle (EV) or HEV and motor traction, as multiple distributed energy sources such as batteries, PVs, and FCs can be connected through a multilevel cascaded dc–dc converter to feed into a load or the ac grid without voltage balancing problems.

#### A) Single dc source (Modular):

One topology for single- input multilevel structures is the boost converter with multiple submodules consisting of switches/diodes and capacitors [47]. A schematic of this converter with several submodules is shown in Fig. 3.17(a). The main advantages of this type of converter are its simplicity, modularity, and flexibility [48]. As can be inferred from Fig. 3.17(a), this type of multilevel converter comprises several submodules and is, therefore, called a multilevel modular dc-dc converter. Two basic structures of this kind without active switching at their output stages are shown in Fig. 3.17. In Fig. 3.17(b), a PWM boost converter is employed as the base level of a proposed multilevel converter [49]. In Fig. 3.17(c), a two-switch multilevel converter with no inductive element is shown in [50]. The main advantage of these structures is their low-voltage stress on output devices.

Figure 3.17: Interleaved dc–dc converters. (a) and (b) General layouts of interleaved step-up converters

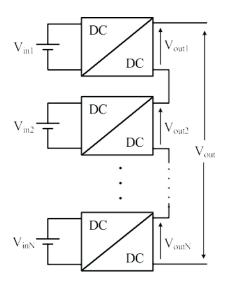

#### B) Multiple dc source (Cascaded):

To increase the out- put voltage level of PV or FC modules, such sources can be connected in series to increase their string voltage. This series-connected voltage can then be connected to a converter for regulation or further step-up purposes. On the other hand, such sources can be connected in cascaded multilevel connections, which have been claimed to have better reliability, safety/protection, and maintainability and lower cost [51]-[53]. This group of multilevel converter comprises cascaded connections of multiple lower voltage dc-dc converters [see Fig. 3.18(a)] and is therefore called multilevel cascaded dc-dc converters.

Figure 3.18: Multilevel cascaded dc–dc converters with multiple dc sources. (a) General cascaded structure.

# 3.5 Summary

The ongoing technological progress in high-voltage step-up dc-dc converter has five primary drivers—energy efficiency, power density, cost, complexity, and reliability—all of which also influence each other to some extent. Each voltage- boosting technique has its own unique features and suitable applications, and there is no one-size-fits-all solution. Nevertheless, it is generally not fair to permanently favor any particular technique or solution [2]. Table 3.2 provides a comparative summary of various voltage-boosting techniques in terms of their major characteristics (i.e., power level, cost, reliability, efficiency, power density, weight, integration, and complexity).

| Voltage Boosting<br>Technique          | Advantages                                                                                                                                                                                                                                                 | Disadvantages                                                                                                                                                                          | Appropriate<br>Applications                                                                                                                                                                                                 |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Switched<br>Capacitor<br>(Charge Pump) | <ul> <li>Cheap &amp; lightweight circuits</li> <li>Small size &amp; high power density.</li> <li>Easy to be integrated</li> <li>Fast dynamic response</li> </ul>                                                                                           | <ul> <li>Startup inrush current</li> <li>Sensitive to the ESR of<br/>capacitors.</li> <li>Lack of output voltage<br/>regulation.</li> <li>Only discrete output<br/>voltage.</li> </ul> | <ul> <li>Energy Harvesting.</li> <li>Mobile displays<br/>(AMOLED).</li> <li>Automotive and<br/>vehicular applications.</li> <li>High gain dc—dc<br/>applications.</li> </ul>                                                |

| Voltage Multiplier                     | <ul> <li>Very high voltage ability<br/>with simple topology.</li> <li>Cell based structure.</li> <li>Can be integrated to<br/>various structures.</li> </ul>                                                                                               | <ul> <li>High voltage stress on components.</li> <li>Need several cells with high ratings for very high voltage applications.</li> </ul>                                               | <ul> <li>Medical (X-ray, laser).</li> <li>Military (high power<br/>laser).</li> <li>Physics research</li> </ul>                                                                                                             |

| Switched Inductor<br>and Voltage Lift  | <ul> <li>High boost ability.</li> <li>Amenable in many converters.</li> </ul>                                                                                                                                                                              | <ul> <li>Need more passive components.</li> <li>Not suitable for high power applications.</li> </ul>                                                                                   | <ul> <li>Mid-range dc—dc<br/>converters.</li> <li>High gain dc—dc<br/>applications.</li> </ul>                                                                                                                              |

| Magnetic<br>Coupling                   | <ul> <li>Versatile in boost ability<br/>due to tunable turns ratio of<br/>magnetic coupling.</li> <li>Switch can be implemented<br/>in low voltage side help to<br/>reduce conduction loss.</li> <li>High efficiency in soft<br/>switched type.</li> </ul> | <ul> <li>Negative effects of<br/>leakage inductance such<br/>as large voltage spike.</li> <li>Need precise coupled<br/>magnetic design.</li> <li>Relatively bulky.</li> </ul>          | <ul> <li>High power/voltage<br/>applications</li> <li>DC microgrids.</li> <li>Data &amp; Telco Centers</li> <li>Bidirectional and<br/>regenerative converter</li> <li>Avionic and space.</li> </ul>                         |

| Multi-Stage Level                      | <ul> <li>Modularity structure.</li> <li>High power capability.</li> <li>Reliable and efficient.</li> <li>High voltage/current level.</li> </ul>                                                                                                            | <ul> <li>Large number of components.</li> <li>Relatively heavy, bulky and costly.</li> <li>Efficiency deteriorate with number of stages/-levels.</li> </ul>                            | <ul> <li>HVDC transmission.</li> <li>Renewable energy<br/>systems &amp; distributed<br/>power generation</li> <li>DC micro-grids.</li> <li>High power DC supply</li> <li>Space technology &amp;<br/>applications</li> </ul> |

#### TABLE 3.2: SUMMARY OF VOLTAGE BOOSTING TECHNIQUES & THEIR APPLICATIONS

# Chapter 4

# Design of Switched Capacitor and Switched Inductor Combined Structure

# 4.1 Introduction

One of the main orientations in power electronics in the last decade has been the development of switching mode converters without transformers. Light weight, small size and high-power density are the result of using only switches, capacitors and inductors in the power stage of these converters. Thus, they serve as ideal power supplies for mobile electronic systems (e.g. cellular phones, personal digital assistants, and so forth). Switched-capacitor (SC) converters and Switched-inductor (SL) converter, with their large voltage conversion ratio, promise to be a response to such challenges of the 21st century as high-efficiency converters with low EMI emission and the ability to realize steep step-down of the voltage (to 3V or even a smaller supply voltage for integrated circuits) or steep step-up of the voltage for automotive industry or internet services in the telecom industry.

The primary goal of any switching-mode power converter is to provide a constant (DC or AC) output voltage at its load, despite variations in the input voltage or load. A control element, therefore, has to be introduced in the process of transmitting energy so that the converter (power stage) changes its topology cyclically, and the durations of the switching topologies are adjusted for regulation purposes.

### First SC Converters and Basic Principles

The first SC converters were developed by a group of researchers from Kumamoto, Japan, who processed a DC unregulated voltage toward a DC regulated voltage. The first SC converters suffered from some drawbacks. In order to solve these problems, new configuration of the SC circuit was proposed. The SC block was divided into two symmetrical SC-sub circuits. For the first half-cycle the capacitors in the first SC cell are in a charging phase, and the capacitors in the second SC cell discharge on the load. The role of the two cells is interchanged in the second half-cycle.

Fig 4.1: Basic SC step-down DC-DC converter

Fig 4.2: Step-down converter with two SC sub-circuits.

A switched-capacitor circuit can also be used in the structure of a zero-current-switching (ZCS) converter—a converter in which the transistor turns off at the instant when the current through it reaches the value zero, implying zero-turn-off switching losses.

### Switched Inductor used in Voltage Lifting

The basic SL cell depicted in Fig. 4.3 was first introduced in some literatures. In an SL cell, the inductors are magnetized in parallel and demagnetized in series. As both inductors have the same inductance value and operational condition, they can be integrated into a single core in order to reduce the size and weight of the converter.

Fig 4.3: Basic Switched Inductor cell.

### 4.2 Working Principles

The SC is a well-known voltage-boosting technique based on a CP circuit that is used in many converters. It can be used as a Voltage Multiplier cell. Voltage-level enhancement in a SC circuit comes solely from capacitive energy transfer and does not involve magnetic energy transfer.

The circuit shown in Fig. 4.4A is two-phase Switched Capacitor voltage doubler (TPVD). In the first phase, which is also shown in Fig.4.4, capacitor C1 is charged to the input voltage. In the second phase, capacitor C1 is placed in series with the input source, which ideally doubles the output voltage level.

Fig 4.4: Basic Switched Capacitor Cell.

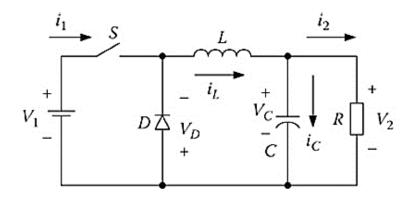

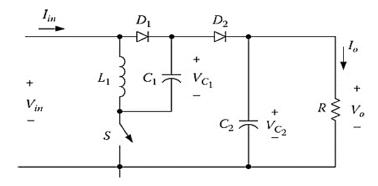

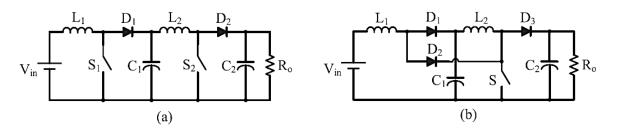

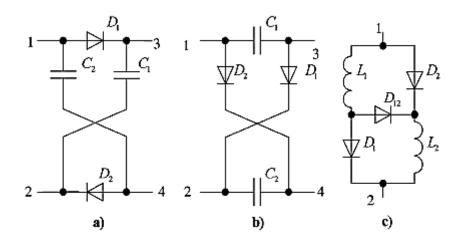

Some structures have been proposed in literatures for either step up and step-down purposes. These structures are formed by either two capacitors and 2–3 diodes, or two inductors and 2–3 diodes.

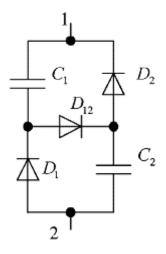

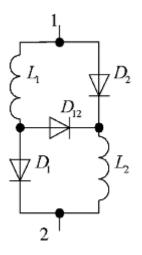

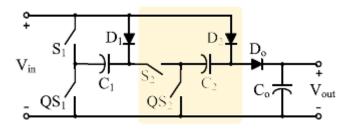

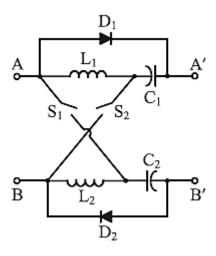

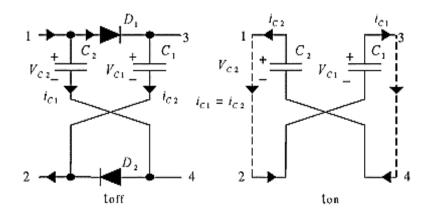

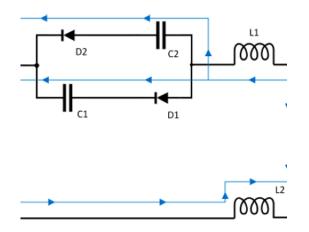

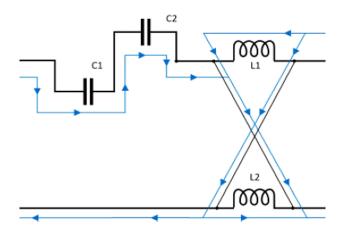

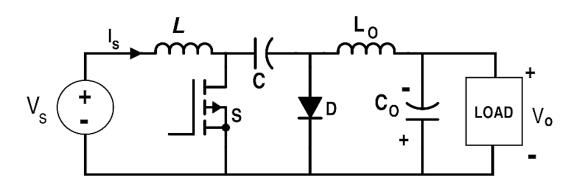

Fig.4.5 presents a switching blocks formed by two capacitors C1 & C2 where C1 is equal to C2 and Diode D1, D2 & D12. In time interval 0<T<DTs or ON state, capacitors C1 & C2 of the structure are charged in series from the input voltage source. In this state, diode D12 is ON and Diode D1 & D2 are OFF shown in Fig 4.6.

Fig 4.5: Switched Capacitor Structure for Step Down purposes.

Fig 4.6: Switching States of Switched Capacitor cell.

In time interval DTs<T<Ts or OFF state, capacitors C1 & C2 of the structure are discharges in parallel to the output load. In this state, Diode D12 is OFF and Diode D1 & D2 are ON.

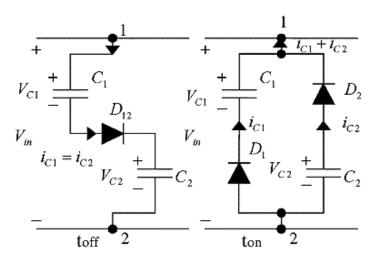

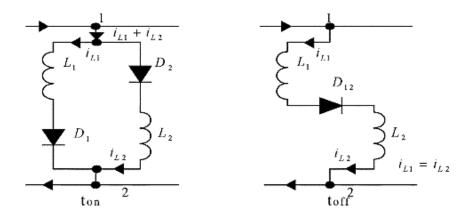

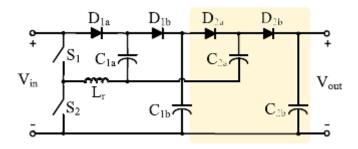

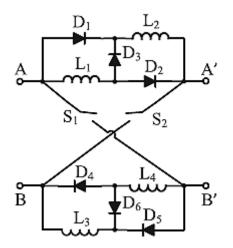

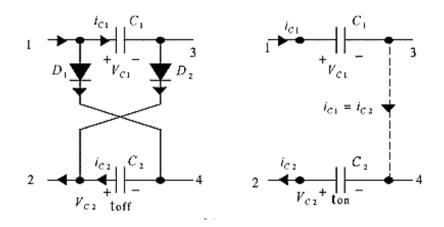

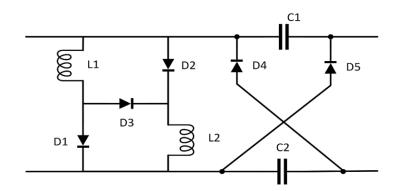

Fig 4.7: Switched Inductor Structure for Step Up purposes.

On the other hand, for Switched Inductor structure the block is formed by two inductor L1 & L2 and three Diode D1, D2 & D12.

In time interval 0<T<DTs or ON state, inductor L1 & L2 of the structure are charged in parallel from the input voltage source. In this state, Diode D12 is OFF and diode D1 & D2 are ON shown in Fig 4.8. On the other hand, in time interval DTs<T<Ts or OFF state, inductor L1 & L2 of the structure are discharges in series to the output load. In this state, diode D12 is ON and Diode D1 & D2 are OFF.

Fig 4.8: Switching states of Switched Inductor cell.

### 4.3 Existing Structures