## **DOCTOR OF PHILOSOPHY**

IN

# ELECTRICAL AND ELECTRONIC ENGINEERING

**Development of Input Switched Hybrid AC to DC Converters**

**Golam Sarowar**

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Board Bazar, Gazipur-1704, Bangladesh. December 30, 2016

## **Development of Input Switched Hybrid AC to DC Converters**

By

Golam Sarowar

A Thesis Submitted to the Board of Examiners in Partial Fulfilment of the Requirements for the Degree of

# DOCTOR OF PHILOSOPHY IN ELECTRICAL AND ELECTRONIC ENGINEERING

Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Board Bazar, Gazipur-1704, Bangladesh.

December, 2016

© 2016 Golam Sarowar

All Rights Reserved.

## **Certificate of Approval**

The thesis entitled "**Development of Input Switched Hybrid AC to DC Converters**" submitted by Golam Sarowar, Student No. 102701 of Academic Year 2010-2011 has been found as satisfactory and accepted as partial fulfilment of the requirement for the Degree of Doctor of Philosophy in Electrical and Electronic Engineering on December 30, 2016

### **Board of Examiners**

SAMO(2

1.

4.

Dr. Md. Ashraful Hoque Professor and Head, Department of EEE, IUT, Gazipur, Bangladesh

Roslant 2.

Dr. Kazi Khairul Islam Professor Department of EEE, IUT, Gazipur, Bangladesh

3.

Dr. Md. Ruhul Amin Professor Department of EEE, IUT, Gazipur, Bangladesh

Dr. Mohammad Jahangir Alam Professor Department of EEE, BUET, Dhaka, Bangladesh

5. malhondy

Dr. Mohammad Ali Choudhury Professor Department of EEE, BUET, Dhaka, Bangladesh Chairman (Supervisor and Ex-officio Member)

Member

Member

Member (External)

Member (External)

## Declaration

I hereby declare that I am the sole author of this dissertation and that the work presented in it, unless otherwise referenced, is entirely my own. I also declare that the work has not been submitted, in whole or in part, to any other university as an exercise for a degree or any other qualification.

Md. Ashraful Hoque Professor, Electrical and Electronic Engineering Department, Islamic University of Technology (IUT). Date: December, 2016

GERANDENA

Golam Sarowar Student No.: 102701 Academic Year: 2010-2011 Date: December, 2016

Dedicated to my family and friends

## **Table of Contents**

| Certificate  | of Approval                                           | iii  |

|--------------|-------------------------------------------------------|------|

| Declaration  | L                                                     | iv   |

| Table of Co  | Table of Contents                                     |      |

| List of Figu | res                                                   | xii  |

| List of Tab  | les                                                   | XX   |

| List of Abb  | reviations of Technical Terms                         | xxiv |

| Acknowled    | gments                                                | XXV  |

| Abstract     |                                                       | xxvi |

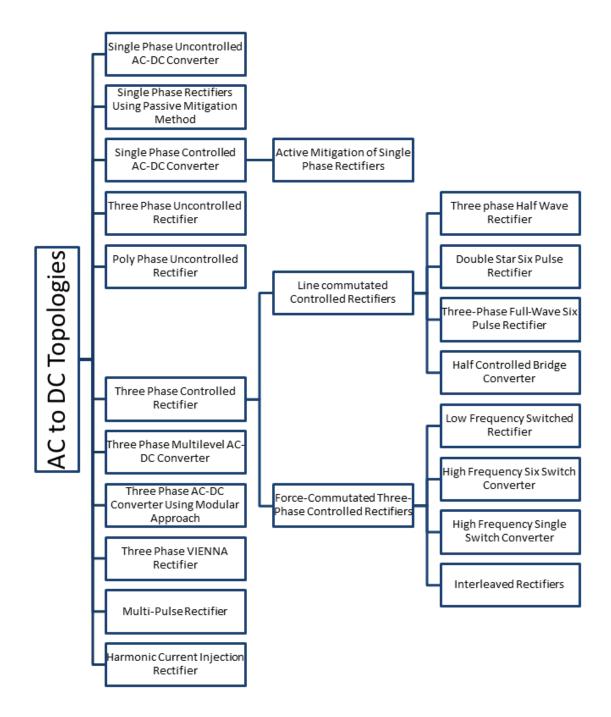

| Chapter 1    | Introduction                                          | 1    |

| 1.1          | AC to DC Converters                                   | 1    |

| 1.2          | Review of AC to DC Converter                          | 2    |

| 1.2.1        | Review According to Topologies                        | 2    |

| 1.2.2        | Review According to application                       | 6    |

| 1.2.3        | Review According to Control Technique                 | 7    |

| 1.3          | Problem Identification and Research Motivation        | 11   |

| 1.4          | Research Objectives                                   | 12   |

| 1.5          | Thesis Outline                                        | 12   |

| Chapter 2    | Background of the Research                            | 14   |

| 2.1          | Current Status of the Problem                         | 14   |

| 2.2          | Performance Parameters of AC to DC Converter          | 20   |

| 2.3          | Investigation of DC to DC converters                  | 23   |

| 2.3.1        | Hybrid Buck Converter                                 | 23   |

| 2.3.2        | Hybrid Boost Converter                                | 27   |

| 2.3.3        | Hybrid Buck-Boost Converter                           | 31   |

| 2.4          | Discussions                                           | 40   |

| Chapter 3    | Conventional and Proposed Single Phase Step-up AC to  | 41   |

|              | DC Converters                                         |      |

| 3.1          | Conventional Output Switched AC to DC Boost Converter | 41   |

| 3.1.1        | Principle of Operation                                | 42   |

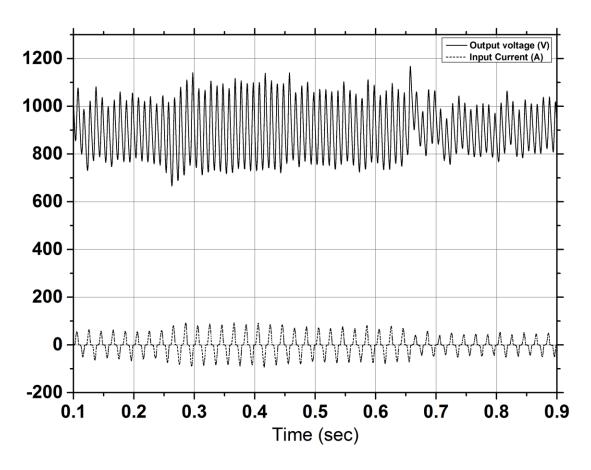

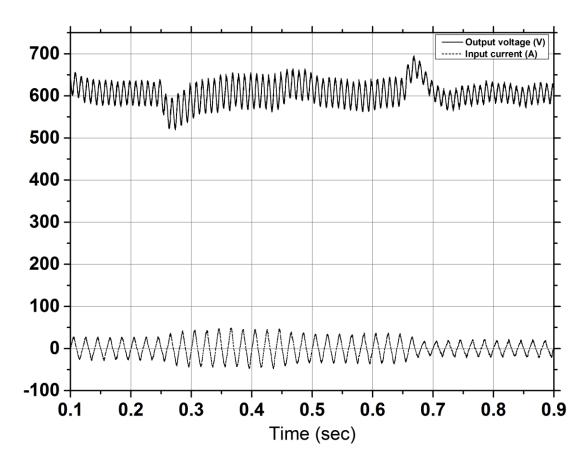

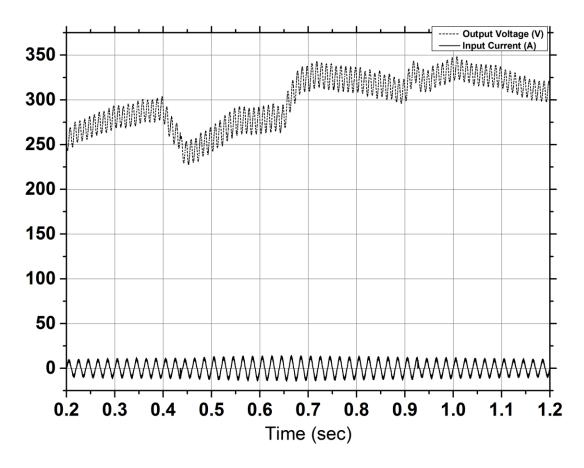

| 3.1.2 | Open Loop Simulation                                      | 43 |

|-------|-----------------------------------------------------------|----|

| 3.1.3 | Ideal Voltage Gain Expression                             | 45 |

| 3.2   | Diode-Capacitor Assisted Output Switched AC to DC Boost   | 46 |

|       | Converter                                                 |    |

| 3.2.1 | Principle of Operation                                    | 47 |

| 3.2.2 | Open Loop Simulation                                      | 48 |

| 3.2.3 | Ideal Voltage Gain Expression                             | 50 |

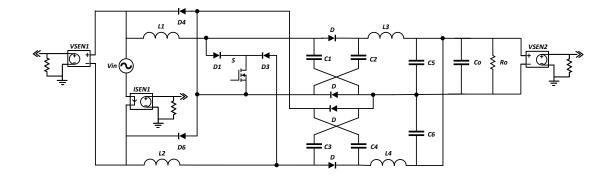

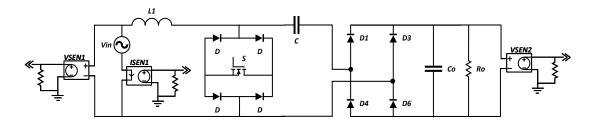

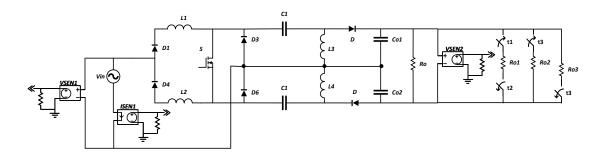

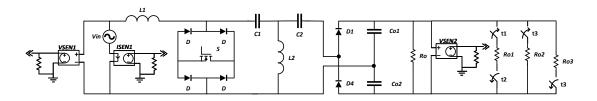

| 3.3   | Input Switched Full-Bridge AC to DC Boost Converter       | 51 |

| 3.3.1 | Principle of Operation                                    | 52 |

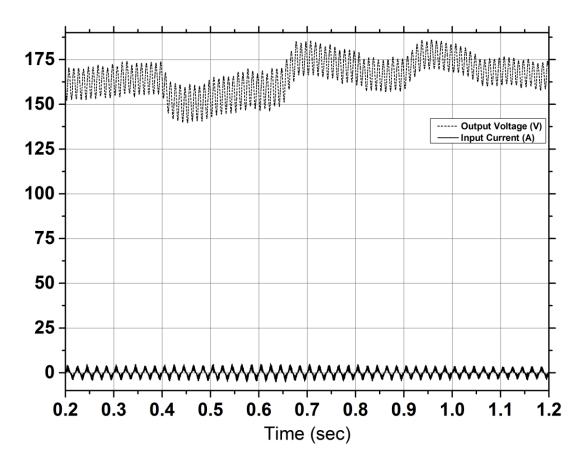

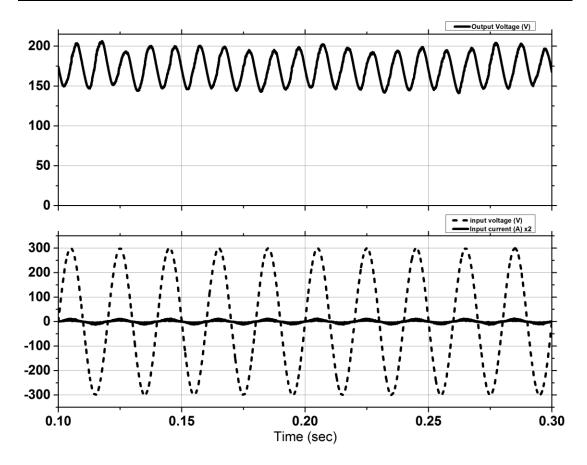

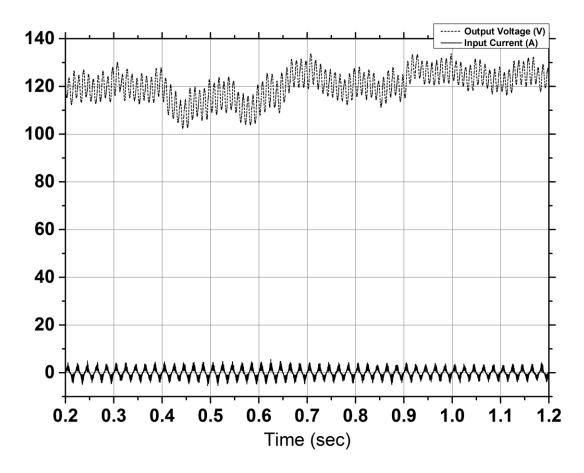

| 3.3.2 | Open Loop Simulation                                      | 53 |

| 3.3.3 | Ideal Voltage Gain Expression                             | 54 |

| 3.4   | Diode-Capacitor Assisted Input Switched Full-Bridge AC to | 58 |

|       | DC Boost Converter                                        |    |

| 3.4.1 | Principle of Operation                                    | 59 |

| 3.4.2 | Open Loop Simulation                                      | 61 |

| 3.4.3 | Ideal Voltage Gain Expression                             | 62 |

| 3.5   | Input Switched Half-Bridge AC-DC Boost Converter          | 63 |

| 3.5.1 | Principle of Operation                                    | 64 |

| 3.5.2 | Open Loop Simulation                                      | 65 |

| 3.5.3 | Ideal Voltage Gain Expression                             | 66 |

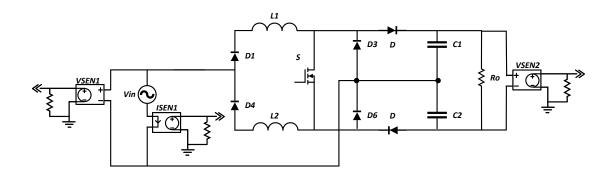

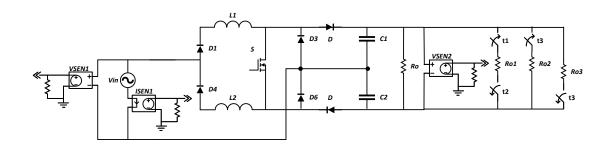

| 3.6   | Modified Input Switched AC to DC Boost Converter          | 71 |

| 3.6.1 | Principle of Operation                                    | 71 |

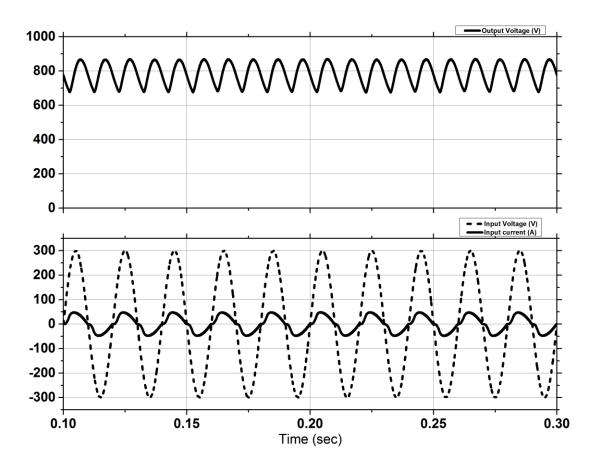

| 3.6.2 | Open Loop Simulation                                      | 73 |

| 3.6.3 | Ideal Voltage Gain Expression                             | 74 |

| 3.7   | Input Switched Coupled Capacitor Full-Bridge AC to DC     | 78 |

|       | Boost Converter                                           |    |

| 3.7.1 | Principle of Operation                                    | 79 |

| 3.7.2 | Open Loop Simulation                                      | 80 |

| 3.7.3 | Ideal Voltage Gain Expression                             | 82 |

| 3.8   | Input Switched Coupled Capacitor Half-Bridge AC to DC     | 86 |

|       | Boost Converter                                           |    |

| 3.8.1     | Principle of Operation                                    | 87  |

|-----------|-----------------------------------------------------------|-----|

| 3.8.2     | Open Loop Simulation                                      | 89  |

| 3.8.3     | Ideal Voltage Gain Expression                             | 90  |

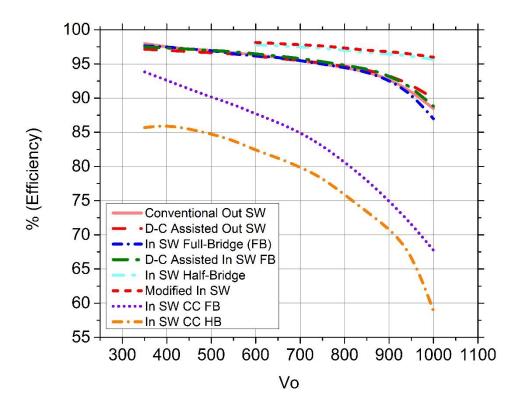

| 3.9       | Comparison of Conversion Efficiency                       | 95  |

| 3.10      | Discussions                                               | 96  |

| Chapter 4 | Investigation of Step-Up Converters with Feedback         | 98  |

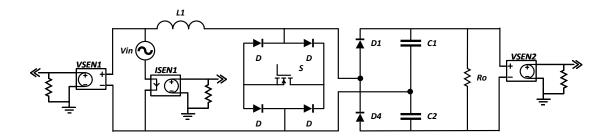

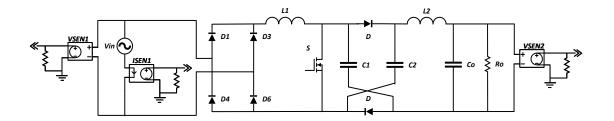

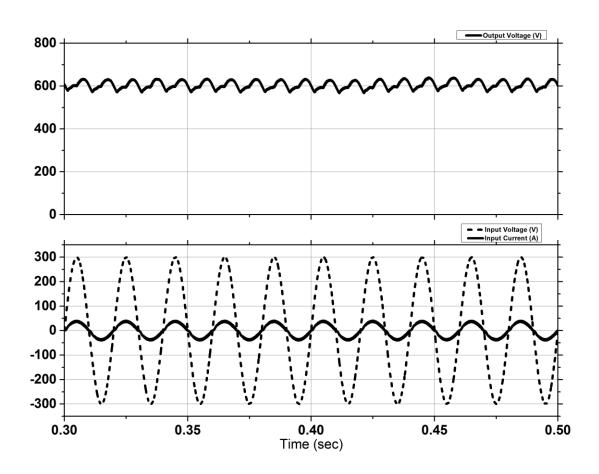

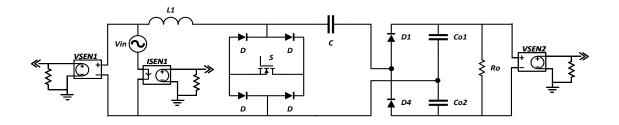

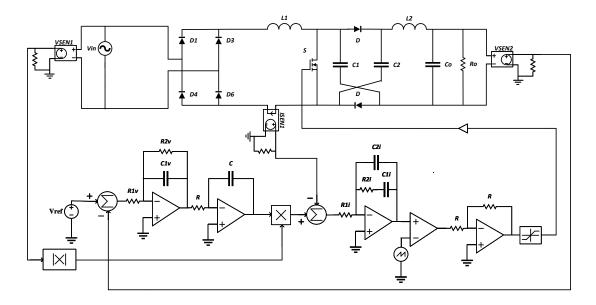

| 4.1       | Modified Input Switched AC to DC Boost Converter          | 98  |

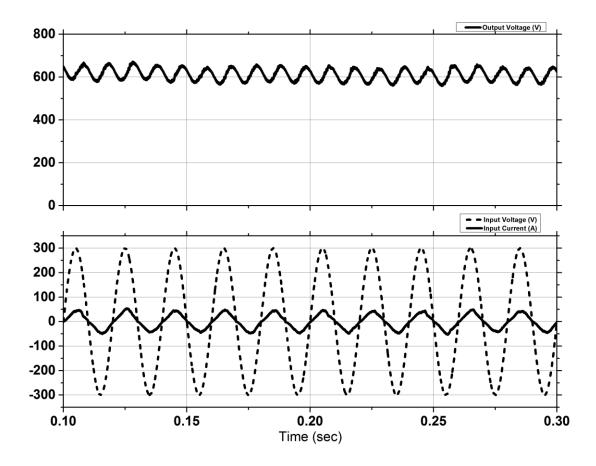

| 4.1.1     | Feedback Analysis                                         | 98  |

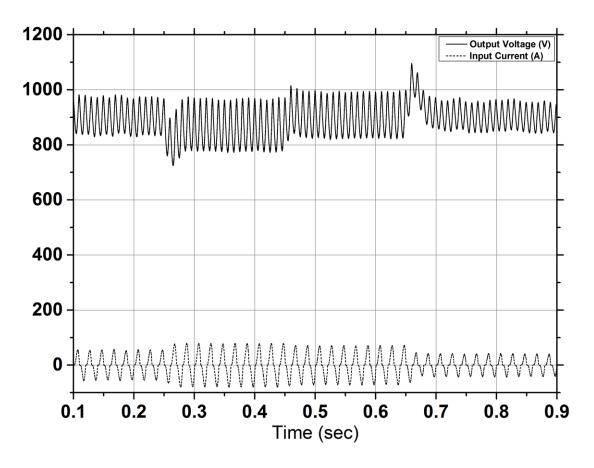

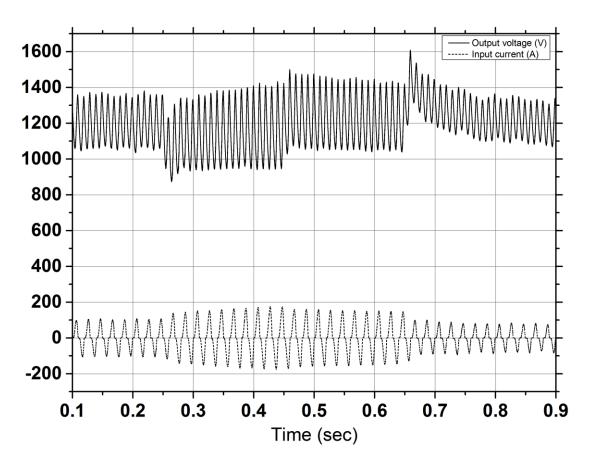

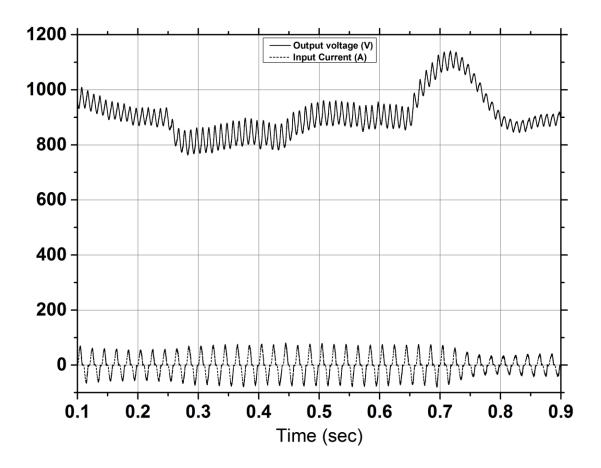

| 4.1.2     | Dynamic Response                                          | 100 |

| 4.2       | Input Switched Half-Bridge AC to DC Boost Converter       | 103 |

| 4.2.1     | Feedback Analysis                                         | 103 |

| 4.2.2     | Dynamic Response                                          | 106 |

| 4.3       | Diode-Capacitor Assisted Output Switched AC to DC Boost   | 108 |

|           | Converter                                                 |     |

| 4.3.1     | Feedback Analysis                                         | 108 |

| 4.3.2     | Dynamic Response                                          | 111 |

| 4.4       | Diode-Capacitor Assisted Input Switched Full-Bridge AC to | 113 |

|           | DC Boost Converter                                        |     |

| 4.4.1     | Feedback Analysis                                         | 113 |

| 4.4.2     | Dynamic Response                                          | 116 |

| 4.5       | Input Switched Coupled Capacitor Full-Bridge AC to DC     | 118 |

|           | Boost Converter                                           |     |

| 4.5.1     | Feedback Analysis                                         | 118 |

| 4.5.2     | Dynamic Response                                          | 121 |

| 4.6       | Input Switched Coupled Capacitor Half-Bridge AC to DC     | 123 |

|           | Boost Converter                                           |     |

| 4.6.1     | Feedback Analysis                                         | 123 |

| 4.6.2     | Dynamic Response                                          | 126 |

| 4.7       | Discussions                                               | 128 |

| Chapter 5 | Investigation of AC to DC Step-Down Converters            | 129 |

| 5.1       | Output Switched Full-Bridge AC to DC SEPIC Converter      | 129 |

|    | 5.1.1 | Principle of Operation                                  | 130 |

|----|-------|---------------------------------------------------------|-----|

|    | 5.1.2 | Open Loop Simulation                                    | 131 |

|    | 5.1.3 | Ideal Voltage Gain Expression                           | 132 |

| 5. | 2     | Diode-Capacitor Assisted Output Switched Full-Bridge AC | 133 |

|    |       | to DC SEPIC Converter                                   |     |

|    | 5.2.1 | Principle of Operation                                  | 134 |

|    | 5.2.2 | Open Loop Simulation                                    | 135 |

|    | 5.2.3 | Ideal Voltage Gain Expression                           | 136 |

| 5. | 3     | Output Switched Half-Bridge AC to DC SEPIC Converter    | 138 |

|    | 5.3.1 | Principle of Operation                                  | 138 |

|    | 5.3.2 | Open Loop Simulation                                    | 139 |

|    | 5.3.3 | Ideal Voltage Gain Expression                           | 141 |

| 5. | 4     | Capacitor Assisted Output Switched Half-Bridge AC to DC | 148 |

|    |       | SEPIC Converter                                         |     |

|    | 5.4.1 | Principle of Operation                                  | 148 |

|    | 5.4.2 | Open Loop Simulation                                    | 150 |

|    | 5.4.3 | Ideal Voltage Gain Expression                           | 151 |

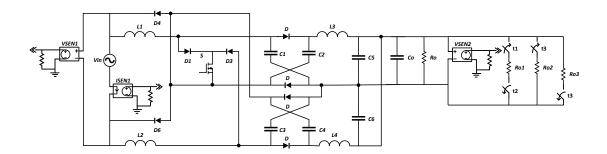

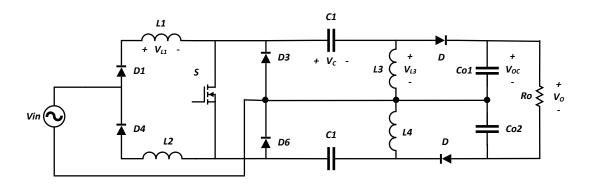

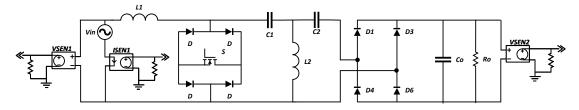

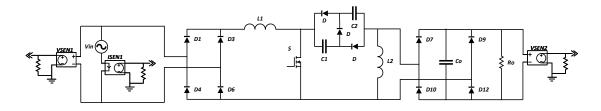

| 5. | 5     | Input Switched full-Bridge SEPIC AC to DC Converter     | 158 |

|    | 5.5.1 | Principle of Operation                                  | 159 |

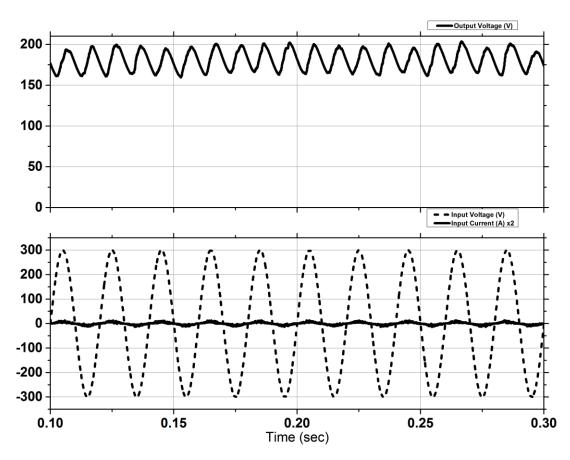

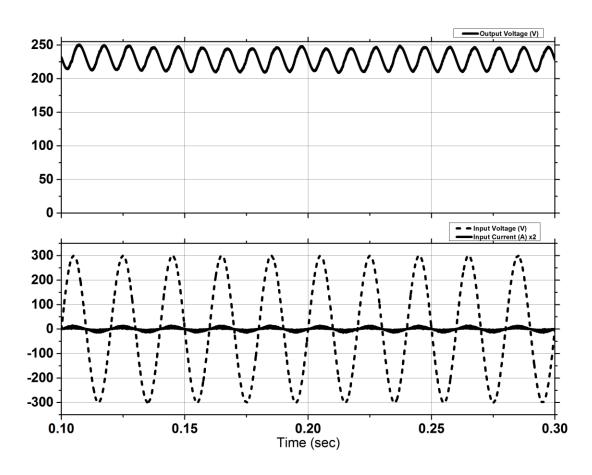

|    | 5.5.2 | Open Loop Simulation                                    | 160 |

|    | 5.5.3 | Ideal Voltage Gain Expression                           | 161 |

| 5. | 6     | Capacitor Assisted Input switched Full-Bridge AC to DC  | 168 |

|    |       | SEPIC Converter                                         |     |

|    | 5.6.1 | Principle of Operation                                  | 169 |

|    | 5.6.2 | Open Loop Simulation                                    | 170 |

|    | 5.6.3 | Ideal Voltage Gain Expression                           | 172 |

| 5. | 7     | Input Switched Half-Bridge AC to DC SEPIC Converter     | 179 |

|    | 5.7.1 | Principle of Operation                                  | 179 |

|    | 5.7.2 | Open Loop Simulation                                    | 181 |

|    | 5.7.3 | Ideal Voltage Gain Expression                           | 182 |

| 5.8 |          | Capacitor Assisted Input Switched Half-Bridge AC to DC     | 189 |

|-----|----------|------------------------------------------------------------|-----|

|     |          | SEPIC Converter                                            |     |

|     | 5.8.1    | Principle of Operation                                     | 190 |

|     | 5.8.2    | Open Loop Simulation                                       | 191 |

|     | 5.8.3    | Ideal Voltage Gain Expression                              | 192 |

| 5.  | .9       | Modified Input Switched AC to DC SEPIC Converter           | 200 |

|     | 5.9.1    | Principle of Operation                                     | 200 |

|     | 5.9.2    | Open Loop Simulation                                       | 202 |

|     | 5.9.3    | Ideal Voltage Gain Expression                              | 203 |

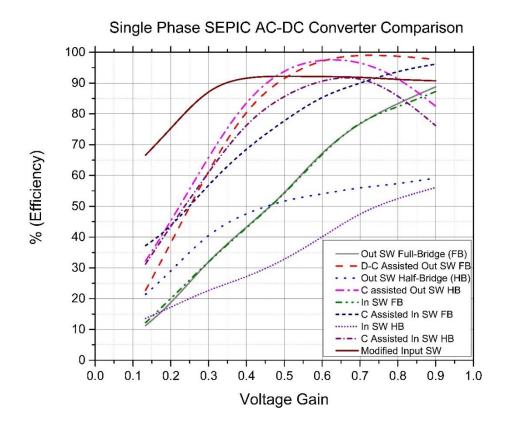

| 5.  | .10      | Comparison of Conversion Efficiency                        | 211 |

| 5.  | .11      | Discussions                                                | 213 |

| С   | hapter 6 | Investigation of Step-Down Converters with Feedback        | 214 |

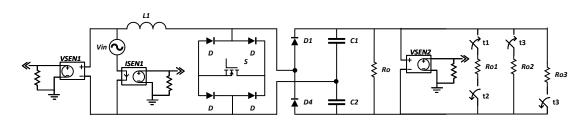

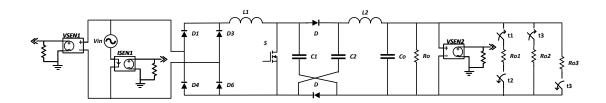

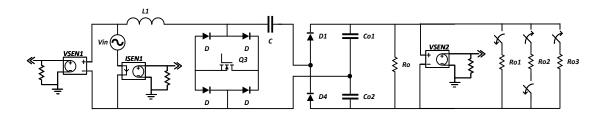

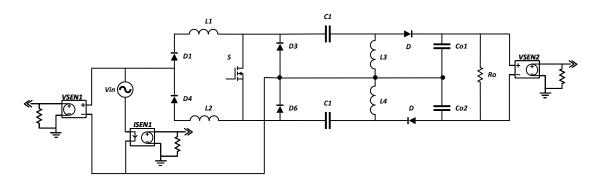

| 6.  | .1       | Modified input switched AC to DC SEPIC converter           | 214 |

|     | 6.1.1    | Feedback Analysis                                          | 214 |

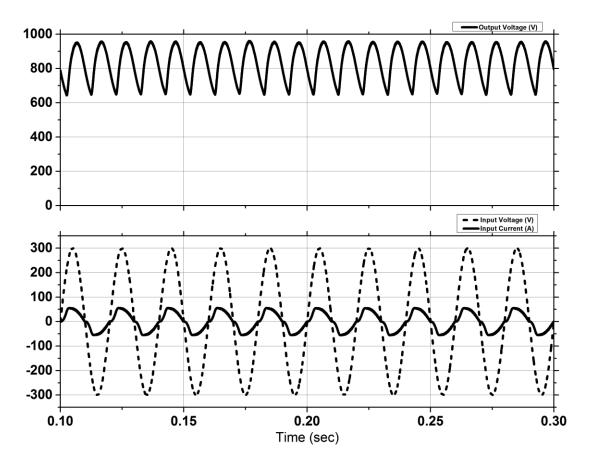

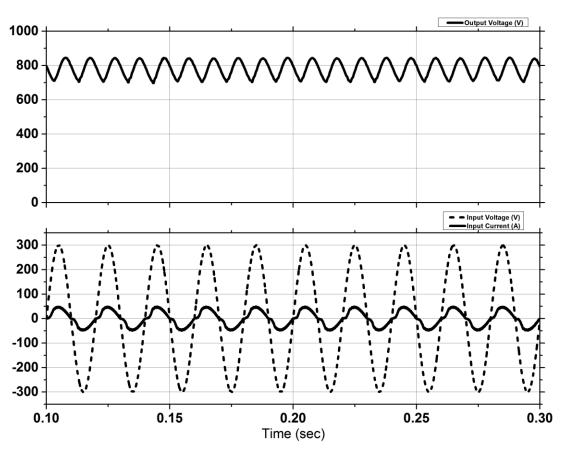

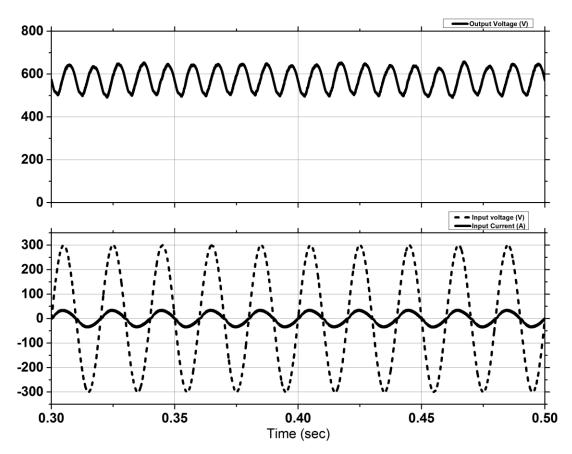

|     | 6.1.2    | Dynamic Response                                           | 216 |

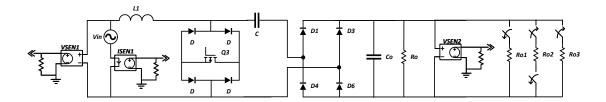

| 6.  | .2       | Capacitor Assisted Input switched Full-Bridge AC to DC     | 219 |

|     |          | SEPIC converter                                            |     |

|     | 6.2.1    | Feedback Analysis                                          | 219 |

|     | 6.2.2    | Dynamic Response                                           | 222 |

| 6.  | .3       | Capacitor Assisted Output Switched Half-Bridge AC to DC    | 224 |

|     |          | SEPIC converter                                            |     |

|     | 6.3.1    | Feedback Analysis                                          | 224 |

|     | 6.3.2    | Dynamic Response                                           | 227 |

| 6.  | .4       | Capacitor Assisted Input switched Half-Bridge AC to DC     | 229 |

|     |          | SEPIC converter                                            |     |

|     | 6.4.1    | Feedback Analysis                                          | 229 |

|     | 6.4.2    | Dynamic Response                                           | 232 |

| 6.  | .5       | Diode-Capacitor Assisted Output Switched Full-bridge AC to | 234 |

|     |          | DC SEPIC converter                                         |     |

|     | 6.5.1    | Feedback Analysis                                          | 234 |

|     | 6.5.2    | Dynamic Response                                           | 237 |

| 6.6         | Discussions                                                 | 239 |

|-------------|-------------------------------------------------------------|-----|

| Chapter 7   | Design of Feedback Control                                  | 240 |

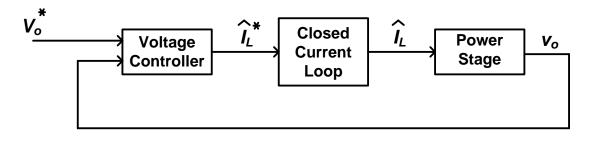

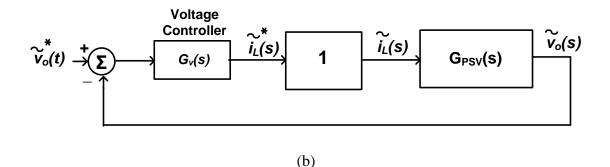

| 7.1         | The Operating Principle of PFC                              | 240 |

| 7.2         | Control of PFCs                                             | 245 |

| 7.3         | AC Equivalent Circuit Modelling of Proposed Boost           | 246 |

|             | Converter                                                   |     |

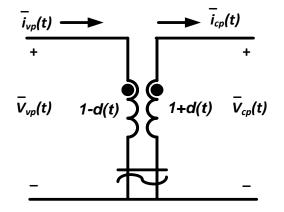

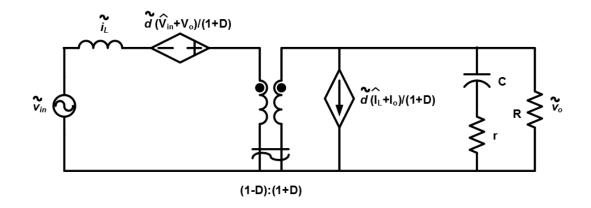

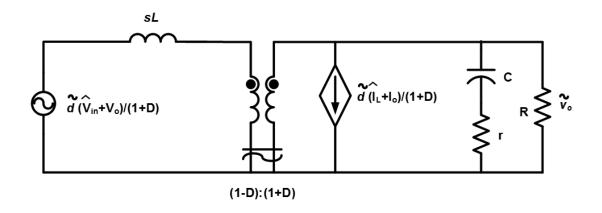

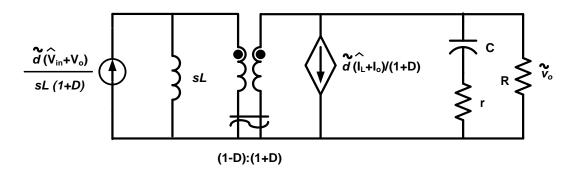

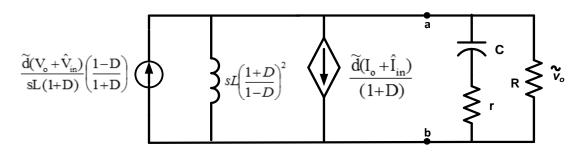

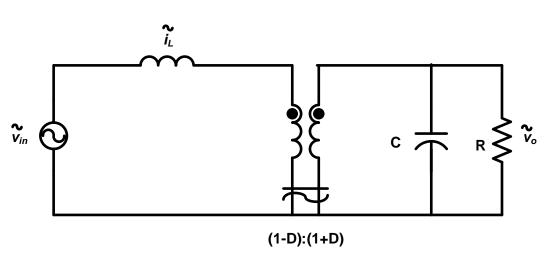

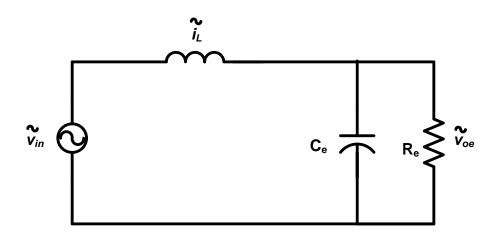

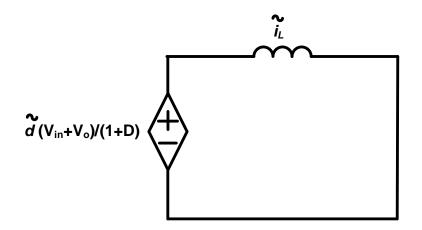

| 7.3.1       | Small-Signal Model of Proposed Boost Converter              | 246 |

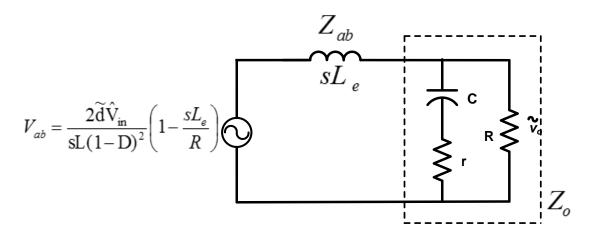

| 7.3.2       | The Control-to-Output Transfer Function                     | 249 |

| 7.3.3       | Line-to-Output Transfer Function (Power Stage Transfer      | 254 |

|             | Function for Voltage Control Loop)                          |     |

| 7.3.4       | Power Stage Transfer Function for Current Control loop      | 257 |

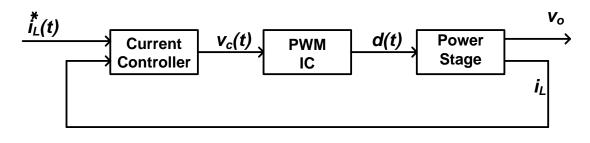

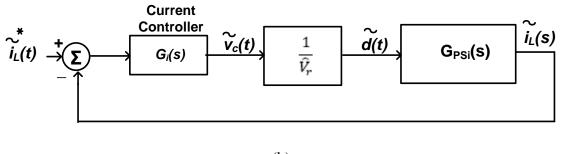

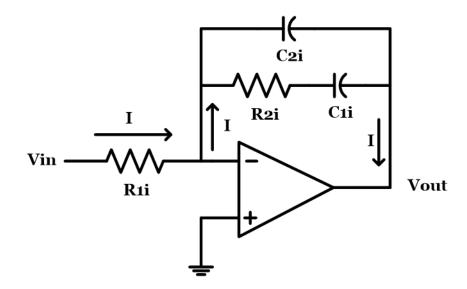

| 7.4         | Design of Inner Average Current Control Loop                | 258 |

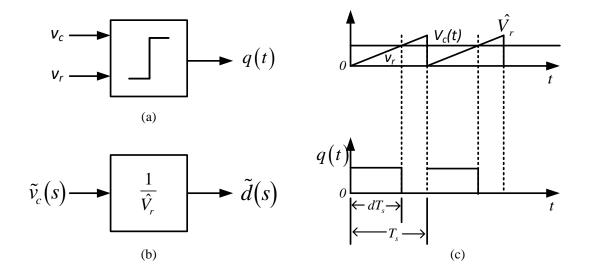

| 7.4.1       | PWM Controller Transfer Function                            | 259 |

| 7.4.2       | Transfer Function of the Converter for Current Control Loop | 260 |

| 7.4.3       | Designing the Current Controller                            | 260 |

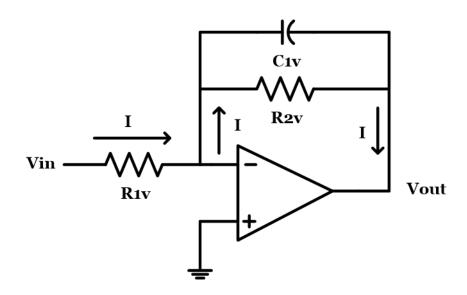

| 7.5         | Design of Outer Voltage Control Loop                        | 261 |

| 7.6         | Controller Design                                           | 263 |

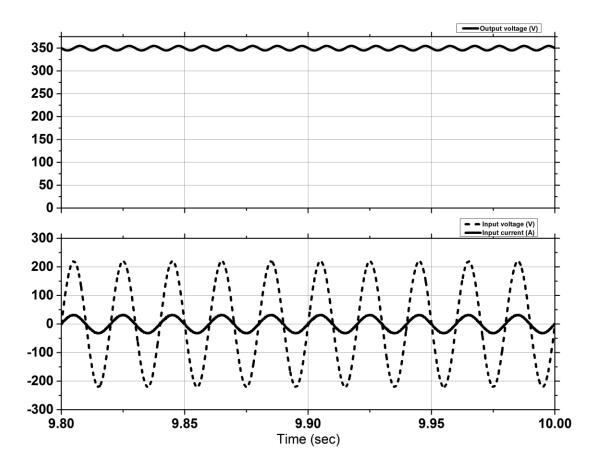

| 7.2         | Simulation with Designed Controller                         | 275 |

| 7.3         | Discussions                                                 | 277 |

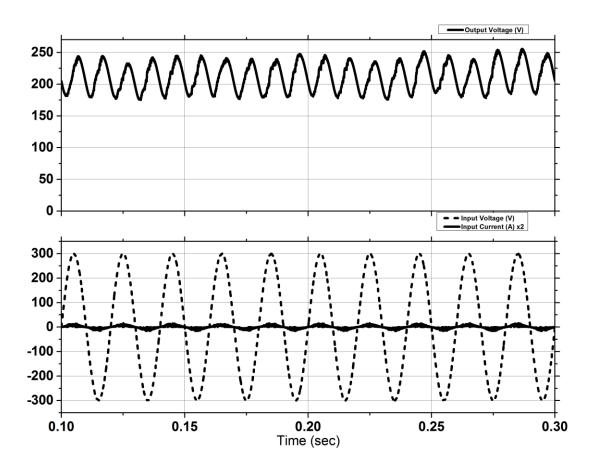

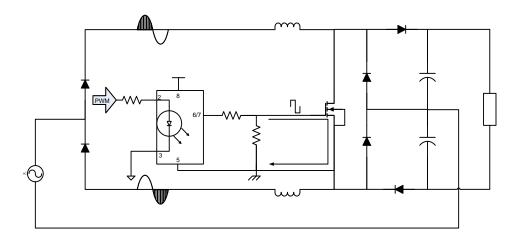

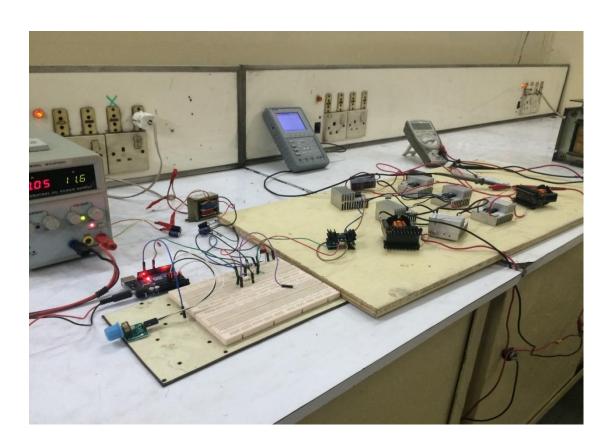

| Chapter 8   | Experimental Results                                        | 278 |

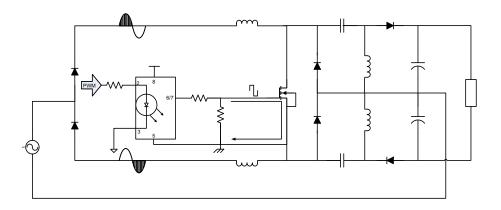

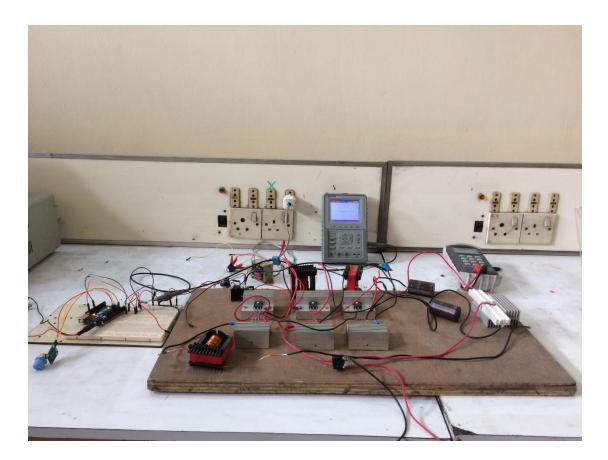

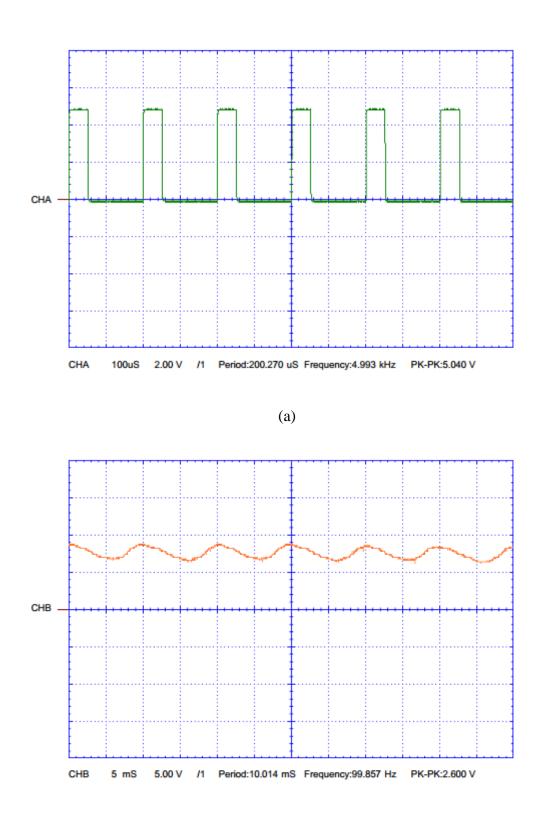

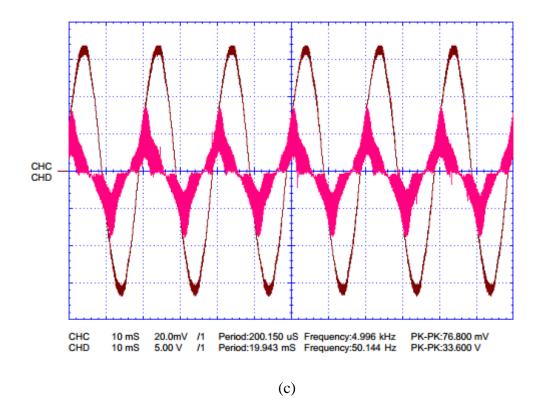

| 8.1         | Experimental Results for Modified Input Switched AC to DC   | 278 |

|             | Boost Converter                                             |     |

| 8.2         | Experimental Results for Modified Input Switched AC to DC   | 286 |

|             | SEPIC Converter                                             |     |

| 8.3         | Discussions                                                 | 294 |

| Chapter 9   | Summary and Conclusion                                      | 295 |

| 9.1         | Major Contributions of the Thesis                           | 297 |

| 9.2         | Conclusion                                                  | 298 |

| 9.3         | Future Work                                                 | 299 |

| References  |                                                             | 300 |

| Published V | Published Works                                             |     |

# **List of Figures**

| Figure 1.1  | General AC to DC Converter topologies.                        | 5  |

|-------------|---------------------------------------------------------------|----|

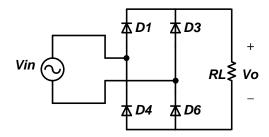

| Figure 2.1  | Schematic diagram of single phase bridge rectifier.           | 14 |

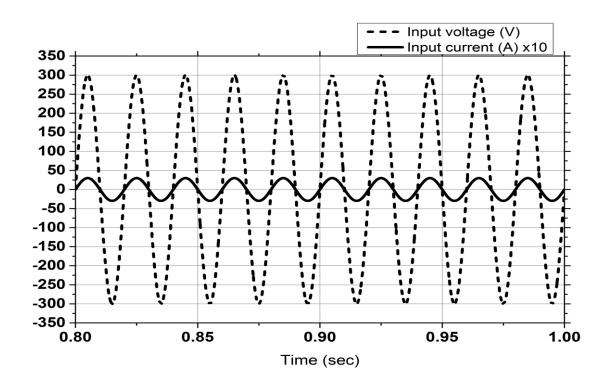

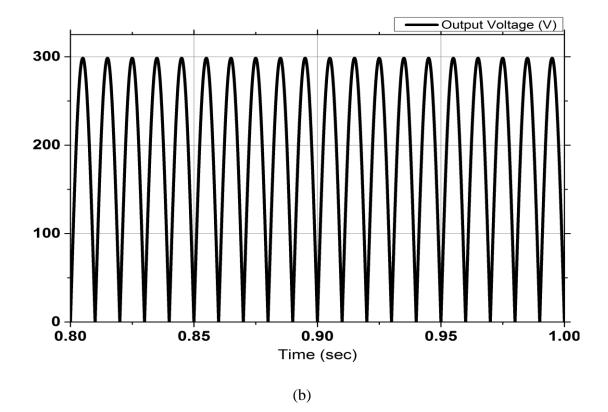

| Figure 2.2  | Waveforms of circuit of Figure 2.1. (a) Input voltage-current | 15 |

|             | and (b) output voltage.                                       |    |

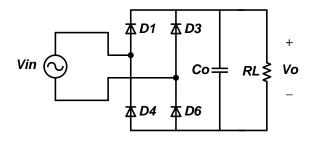

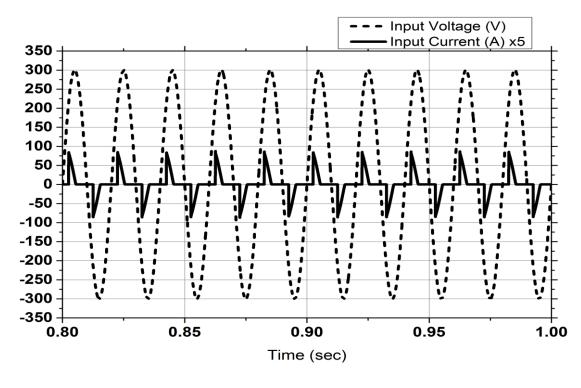

| Figure 2.3  | Single phase bridge rectifier with output filter capacitor.   | 16 |

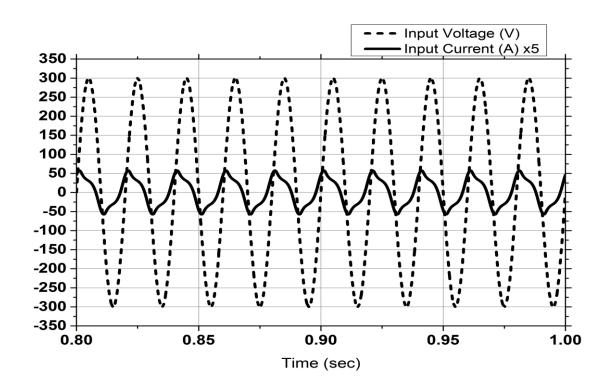

| Figure 2.4  | Waveforms of circuit of Figure 2.3. (a) Input voltage-current | 17 |

|             | and (b) output voltage.                                       |    |

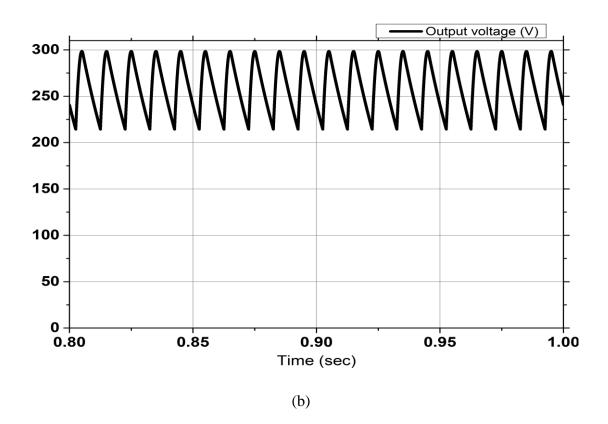

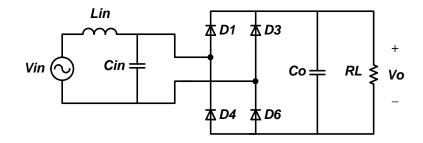

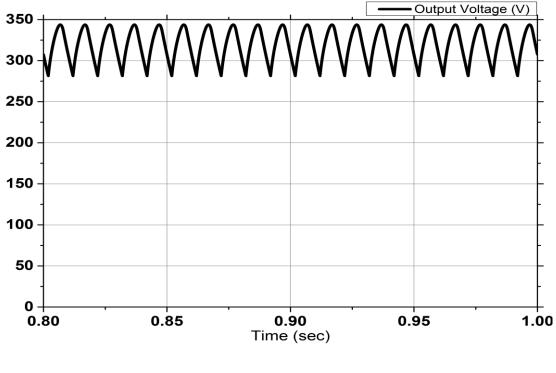

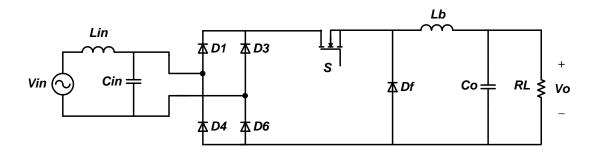

| Figure 2.5  | Bridge rectifier with input and output filter.                | 17 |

| Figure 2.6  | Waveforms of circuit of Figure 2.5. (a) Input voltage-current | 18 |

|             | and (b) output voltage.                                       |    |

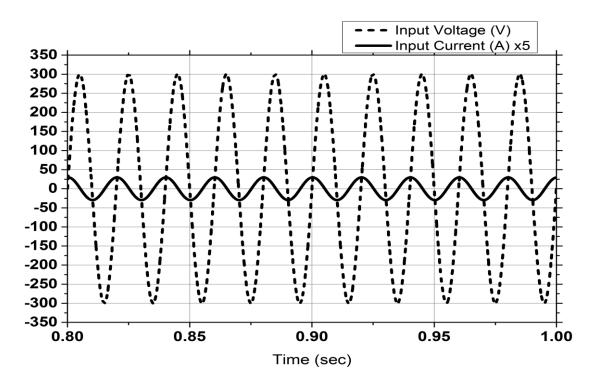

| Figure 2.7  | Two-stage AC to DC buck converter.                            | 19 |

| Figure 2.8  | Waveforms of circuit of Figure 2.7. (a) Input voltage-current | 20 |

|             | and (b) output voltage.                                       |    |

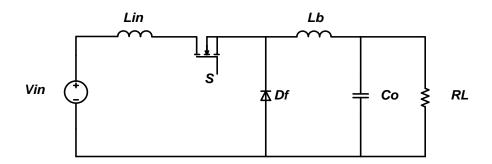

| Figure 2.9  | Conventional DC to DC buck converter.                         | 23 |

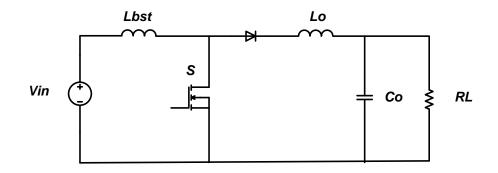

| Figure 2.10 | Hybrid DC to DC buck converter.                               | 24 |

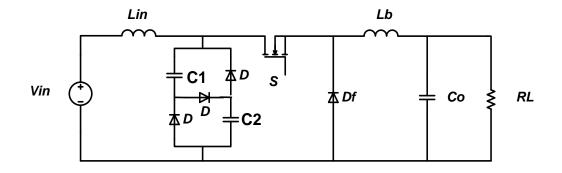

| Figure 2.11 | Efficiency vs duty cycle of conventional and hybrid buck      | 25 |

|             | converter.                                                    |    |

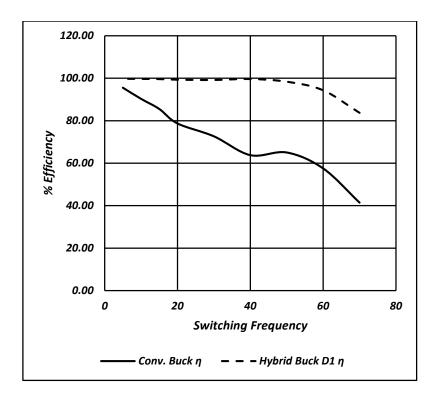

| Figure 2.12 | Efficiency vs switching frequency of convention and hybrid    | 26 |

|             | buck converter.                                               |    |

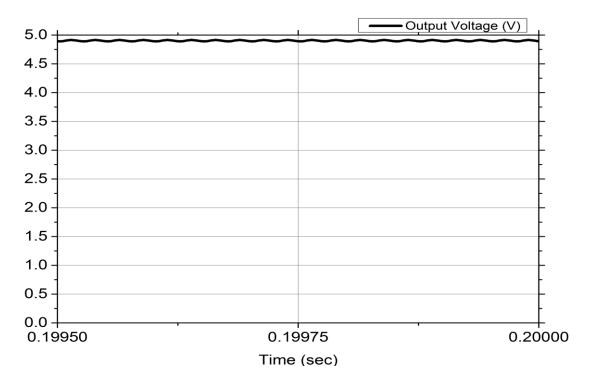

| Figure 2.13 | Output voltage of conventional buck converter at $D = 0.3$ .  | 26 |

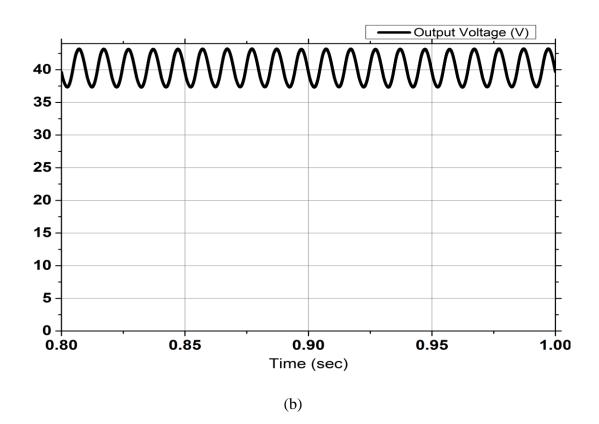

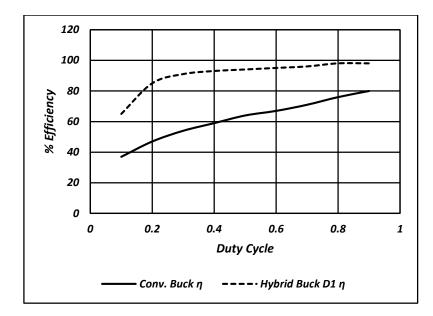

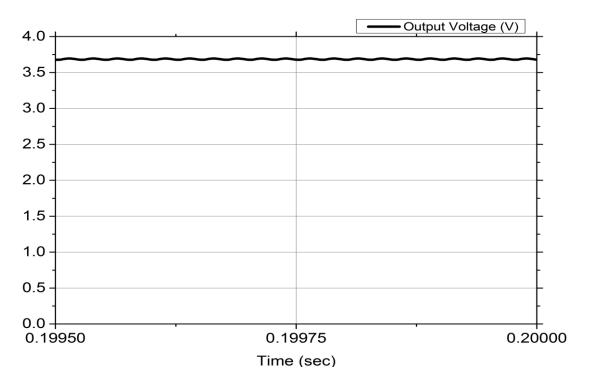

| Figure 2.14 | Output voltage of hybrid buck converter at $D = 0.3$ .        | 27 |

| Figure 2.15 | Conventional DC to DC boost converter.                        | 27 |

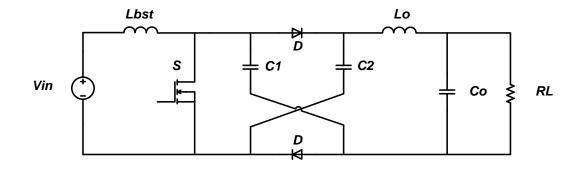

| Figure 2.16 | Hybrid DC to DC boost converter.                              | 28 |

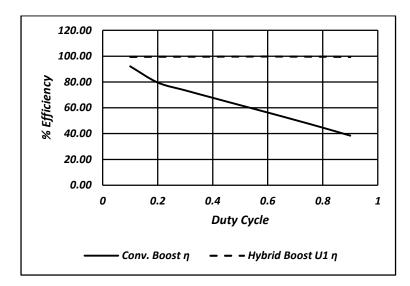

| Figure 2.17 | Efficiency vs duty cycle of conventional and hybrid boost     | 29 |

|             | converter.                                                    |    |

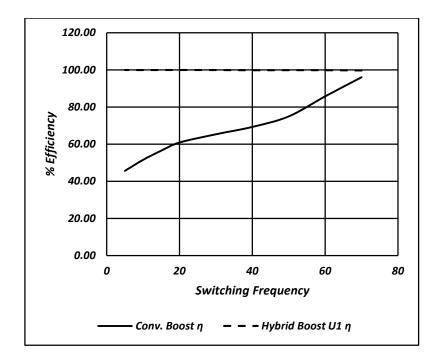

| Figure 2.18 | Efficiency vs switching frequency of conventional and         | 30 |

|             | hybrid boost converter.                                       |    |

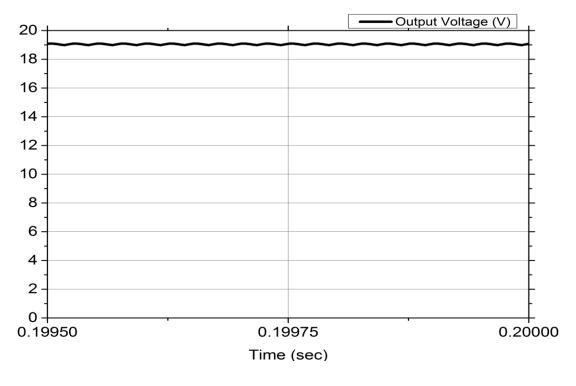

| Figure 2.19 | Output voltage of conventional boost converter at $D = 0.7$ . | 30 |

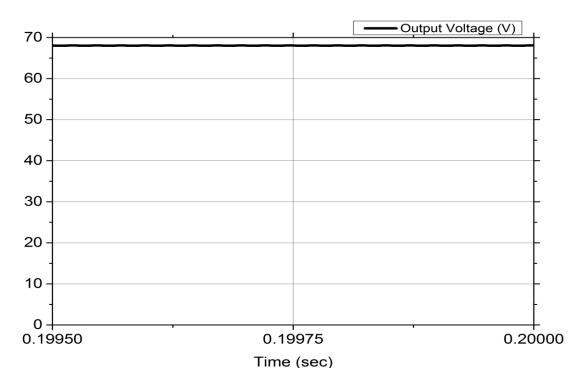

| Figure 2.20 | Output voltage of hybrid boost converter at $D = 0.7$ .       | 31 |

| Figure 2.21 | Conventional DC to DC buck-boost converter.                   | 31 |

| Figure 2.22 | Hybrid DC to DC buck-boost down converter.                    | 32 |

| Figure 2.23 | Hybrid DC to DC buck-boost up converter.                      | 32 |

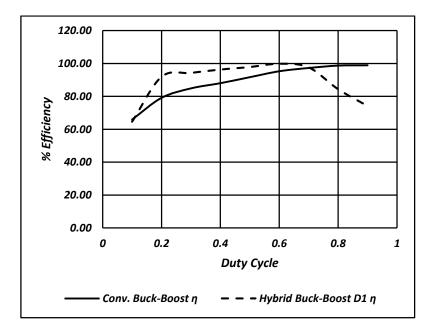

| Figure 2.24 | Efficiency vs duty cycle of conventional and hybrid buck-     | 33 |

|             | boost down converter.                                         |    |

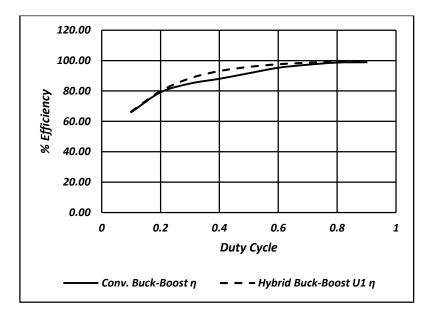

| Figure 2.25 | Efficiency vs duty cycle of conventional and hybrid buck-     | 34 |

|             | boost up converter.                                           |    |

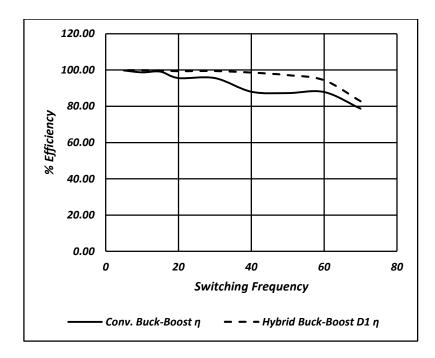

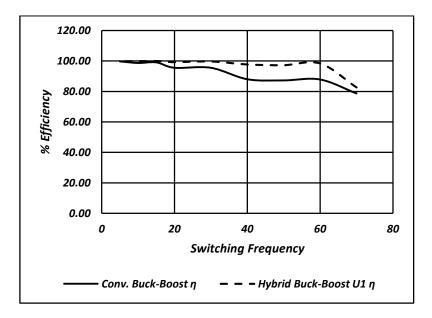

| Figure 2.26 | Efficiency vs switching frequency of conventional and         | 36 |

|             | hybrid buck-boost down converter.                             |    |

| Figure 2.27 | Output voltage of conventional buck-boost converter at        | 36 |

|             | D = 0.3.                                                      |    |

| Figure 2.28 | Output voltage of hybrid buck-boost down converter at         | 37 |

|             | $\mathbf{D} = 0.3.$                                           | •  |

| Figure 2.29 | Efficiency vs switching frequency of conventional and         | 38 |

|             | hybrid buck-boost up converter.                               |    |

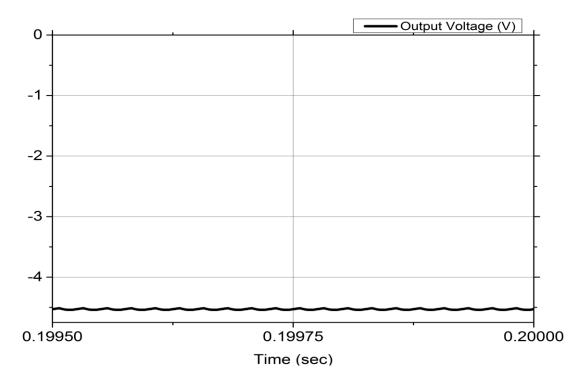

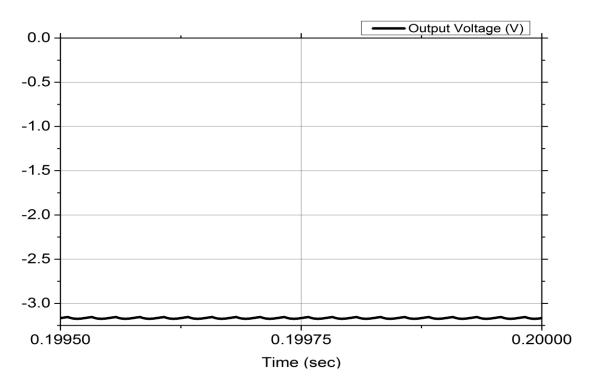

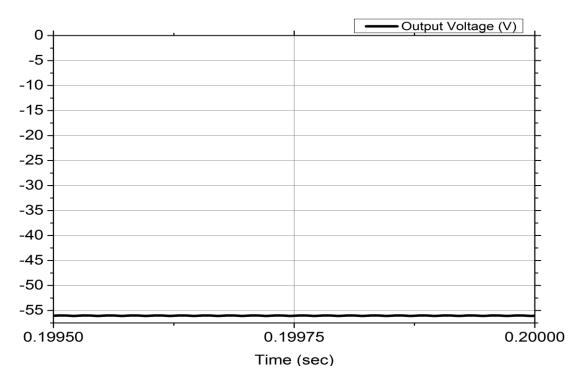

| Output voltage of conventional buck-boost converter at $D = 0.7$ . | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

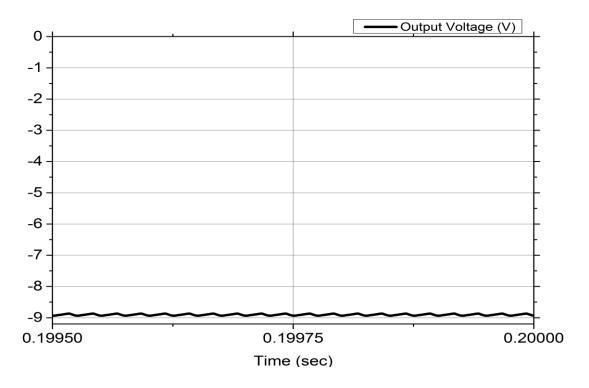

| Output voltage of hybrid buck-boost up converter at $D = 0.7$ .    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

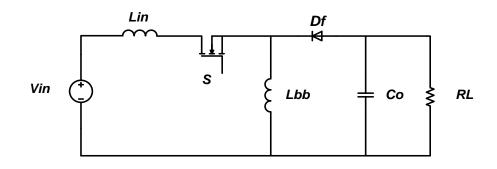

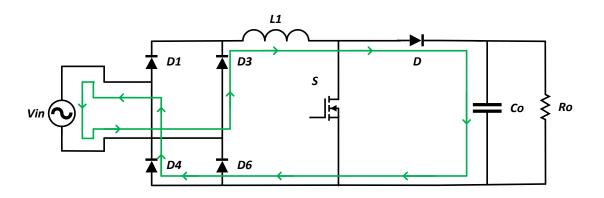

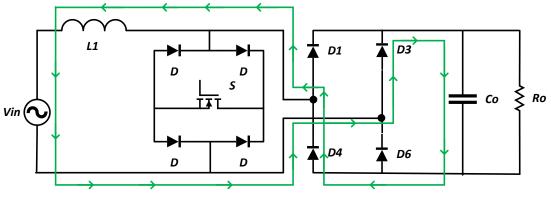

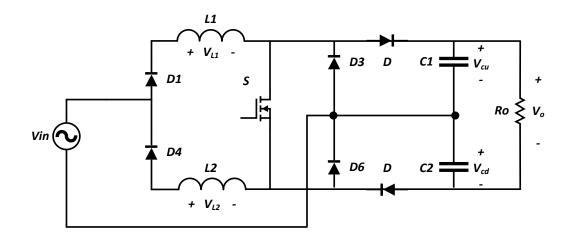

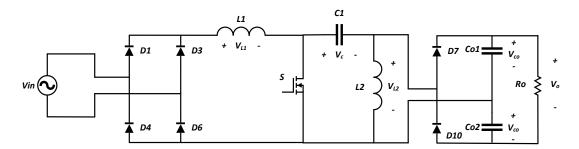

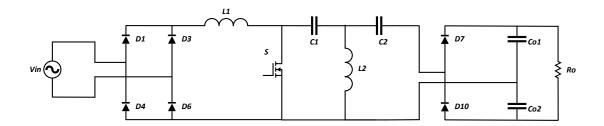

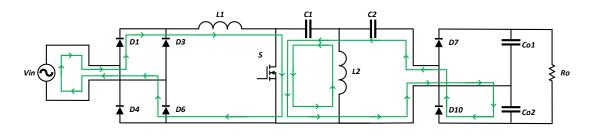

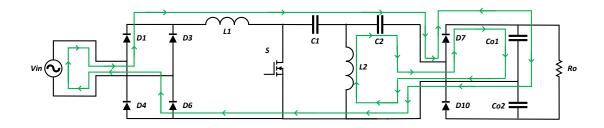

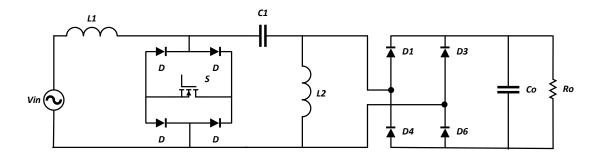

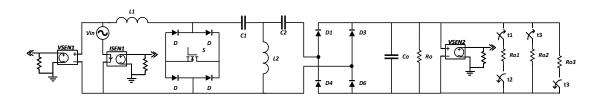

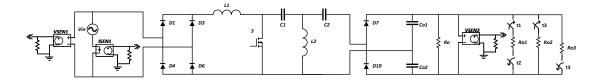

| Conventional output switched AC to DC boost converter.             | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Four steps of operation of the converter in Figure 3.1,            | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (a) circuit when the switch is ON during positive half cycle       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

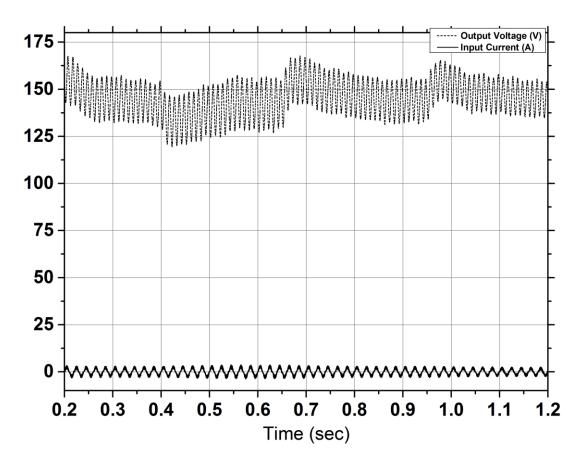

| 1 1                                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| =                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

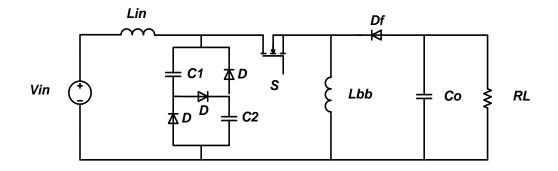

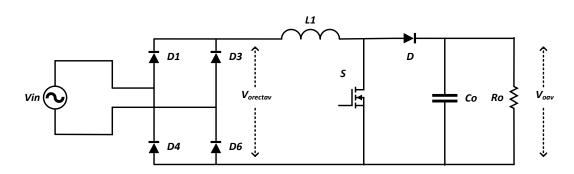

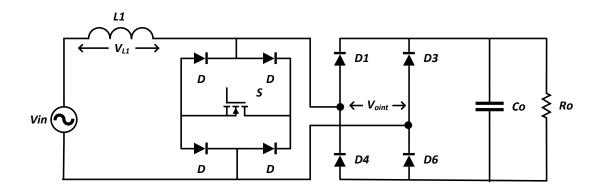

|                                                                    | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| boost converter.                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

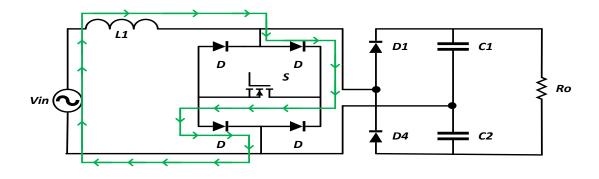

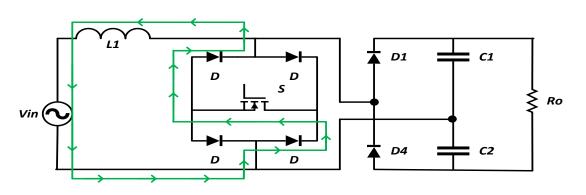

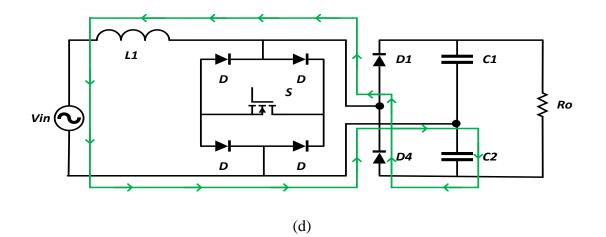

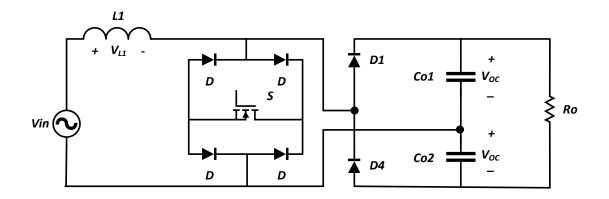

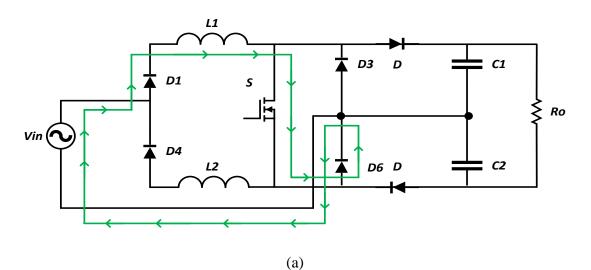

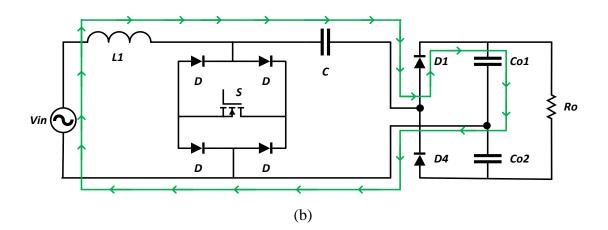

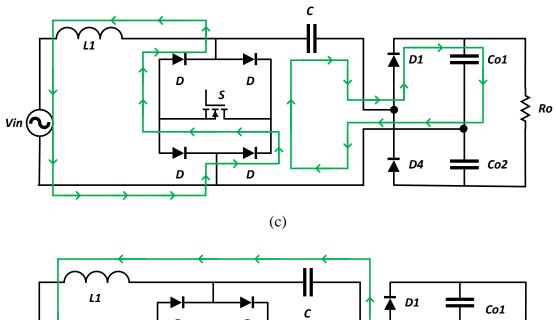

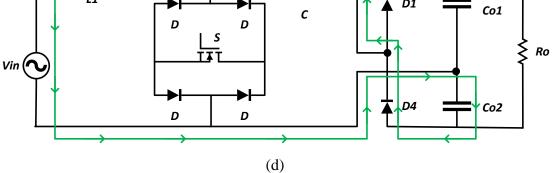

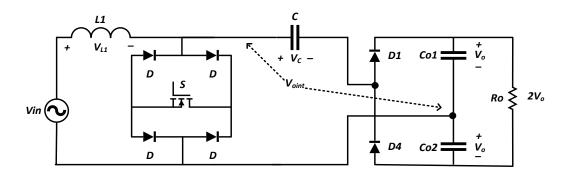

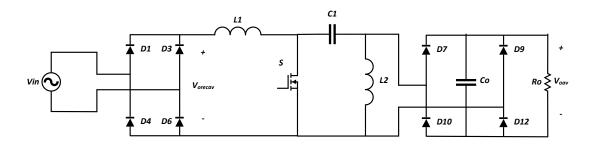

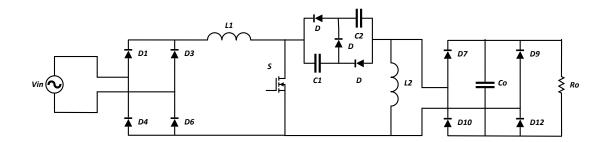

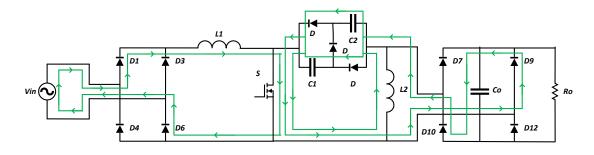

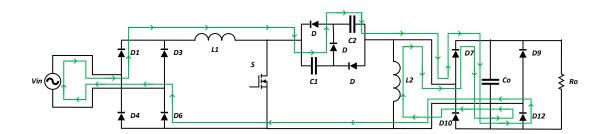

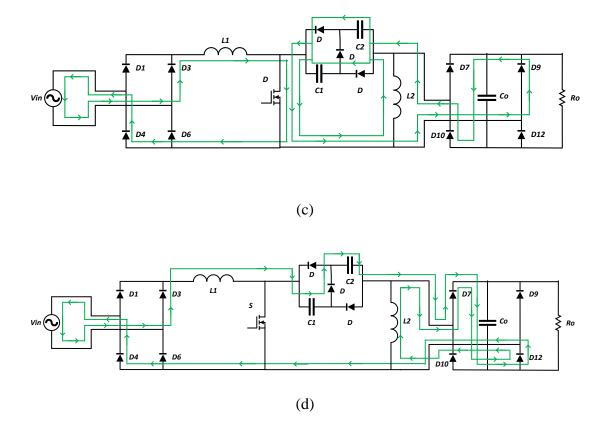

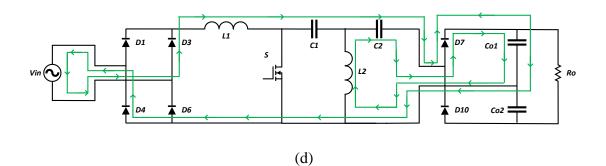

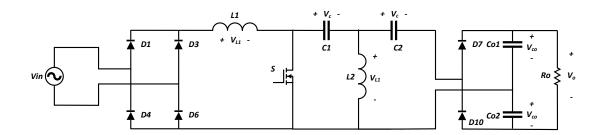

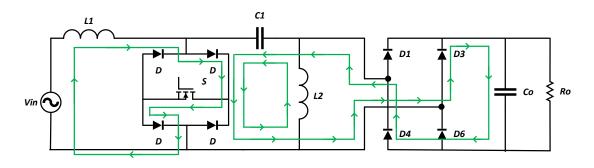

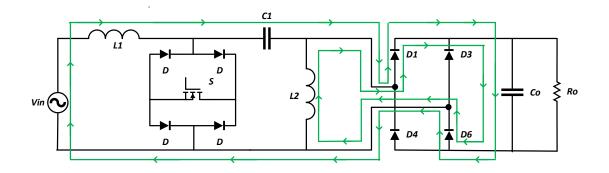

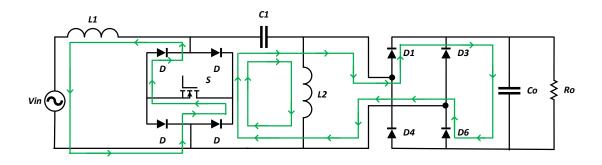

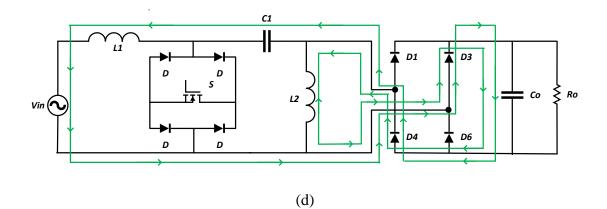

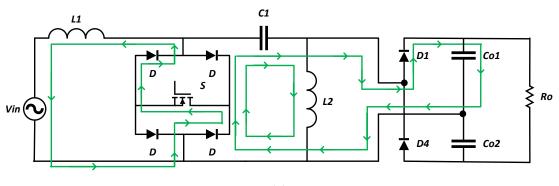

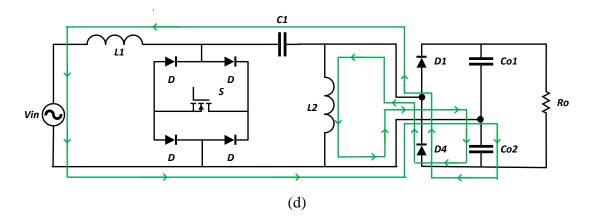

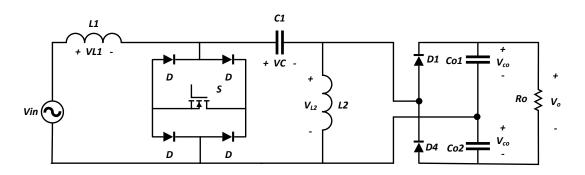

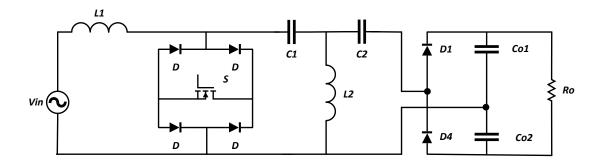

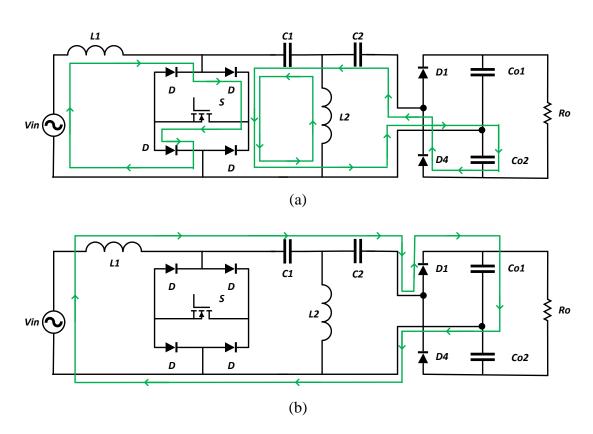

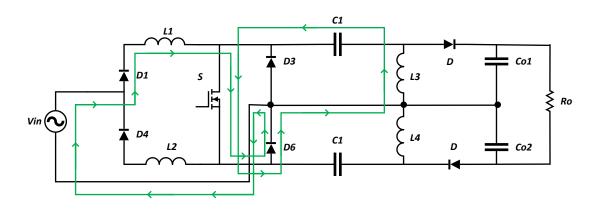

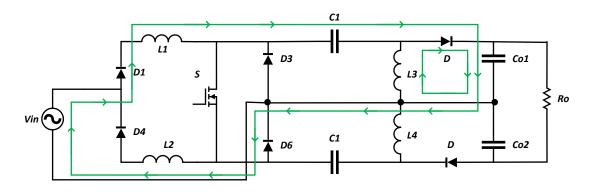

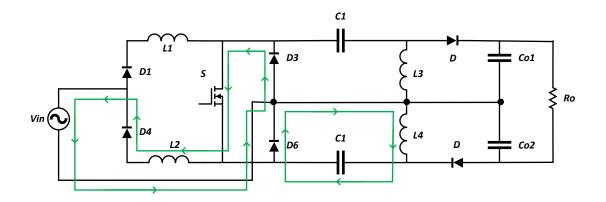

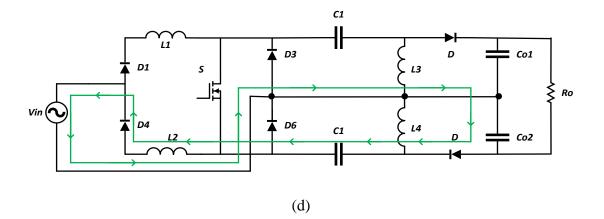

| Four steps of operation of the converter in Figure 3.4,            | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (a) circuit when the switch is ON during positive half cycle       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (b) circuit when the switch is OFF during positive half cycle      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

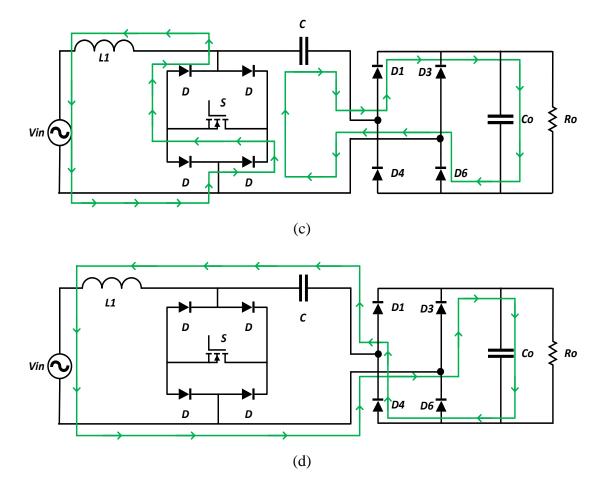

| (c) circuit when the switch is ON during negative half cycle       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

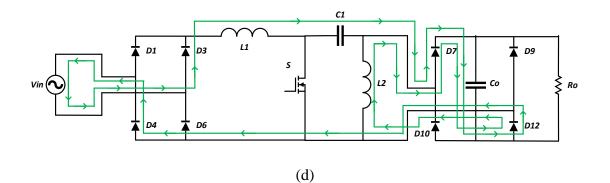

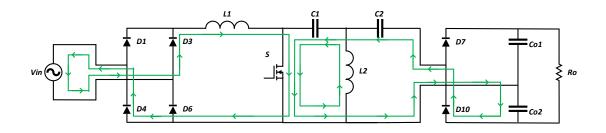

| (d) circuit when the switch is OFF during negative half cycle      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| of line frequency.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

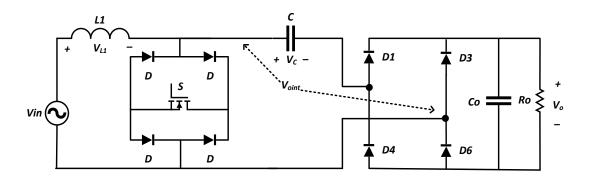

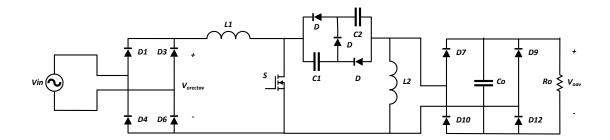

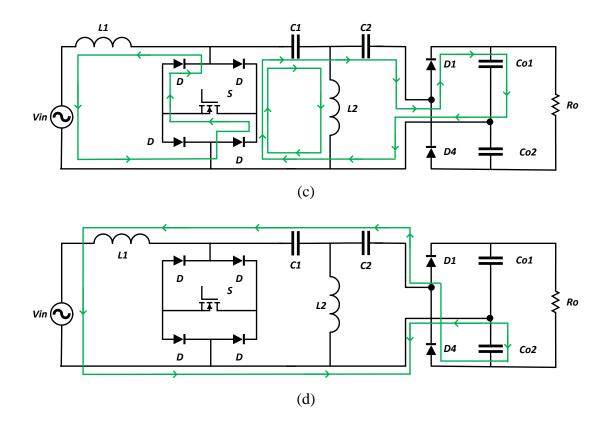

| Proposed diode-capacitor assisted output switched AC to DC         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| boost converter with voltage labels for positive half cycle of     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| operation.                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

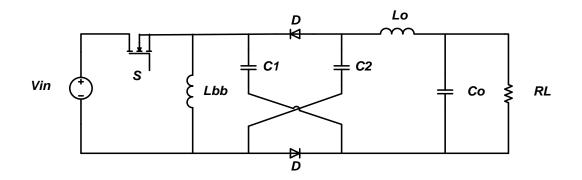

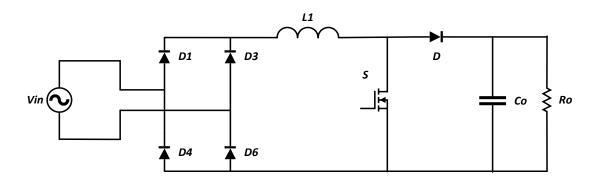

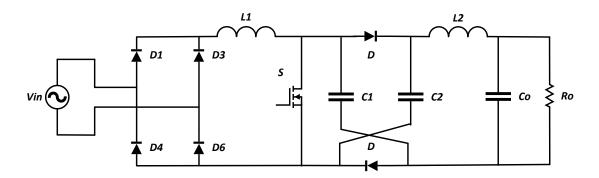

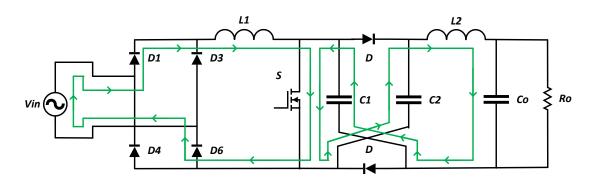

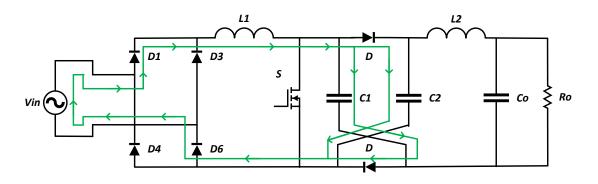

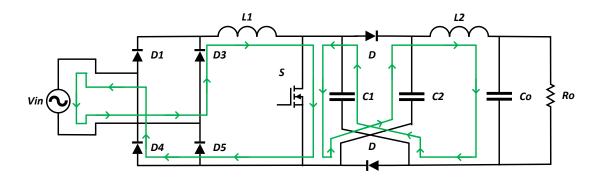

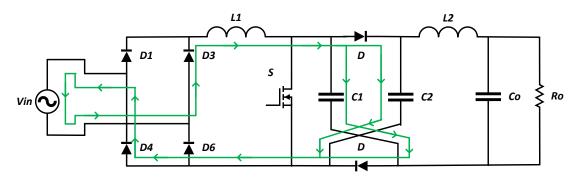

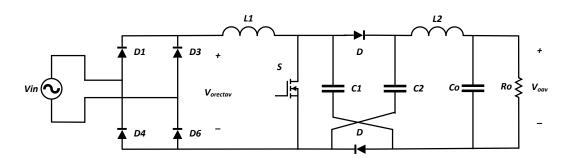

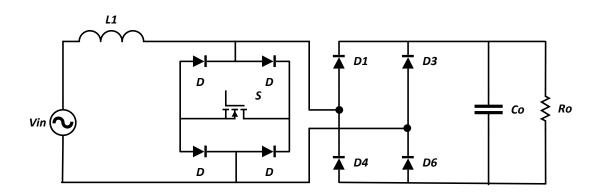

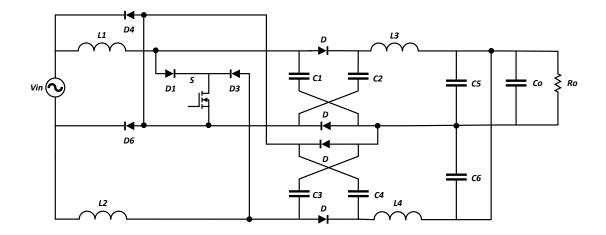

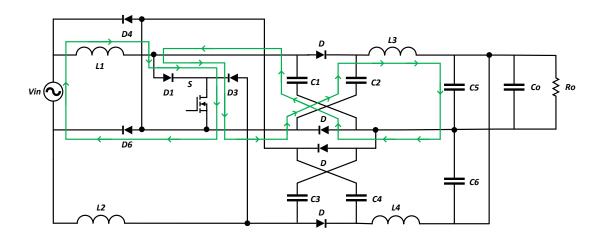

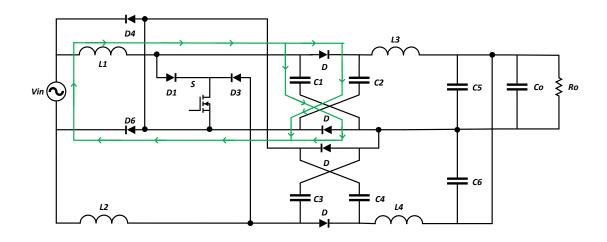

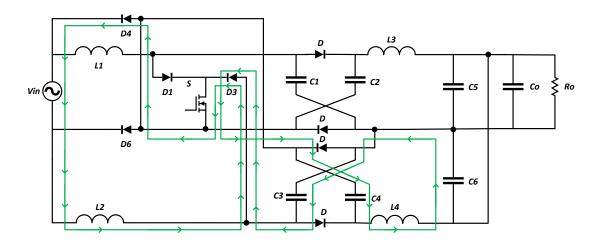

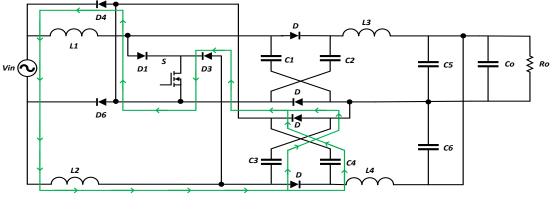

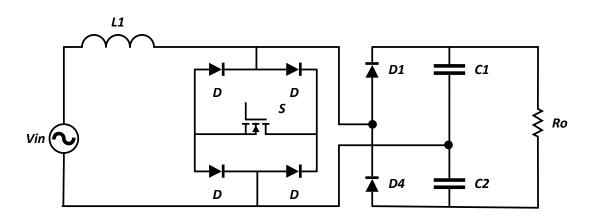

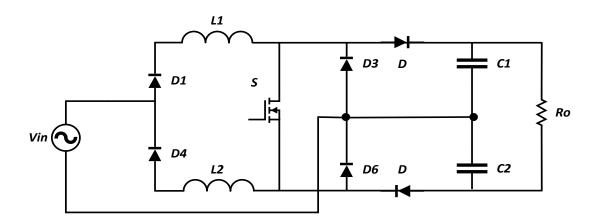

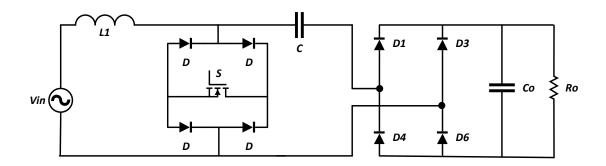

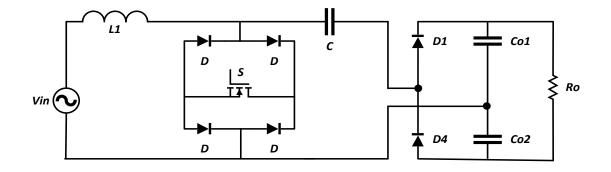

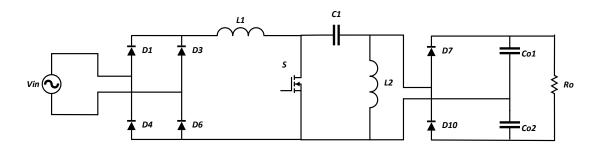

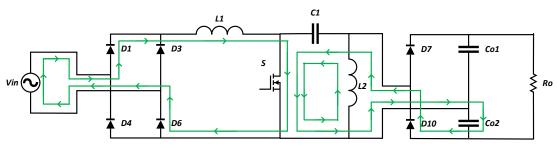

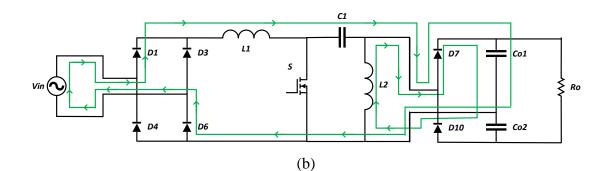

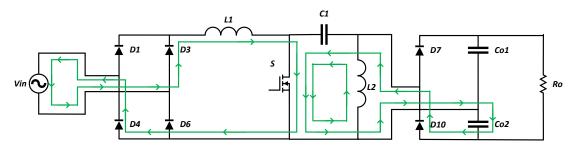

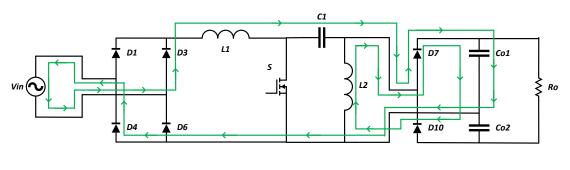

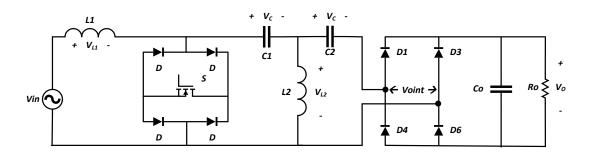

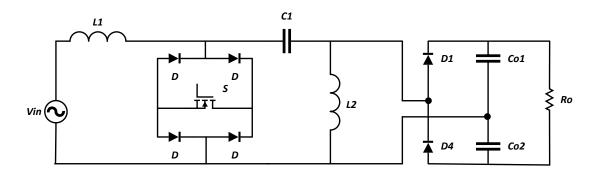

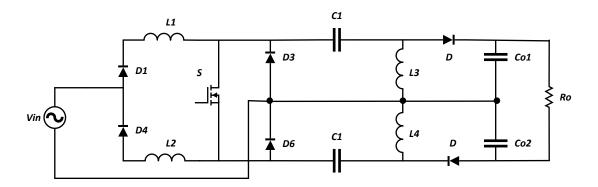

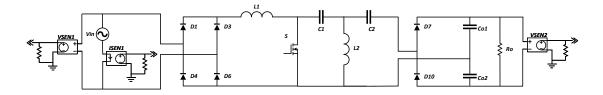

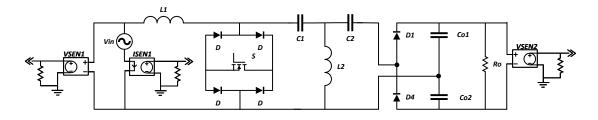

| Input switched full-bridge AC to DC boost converter.               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

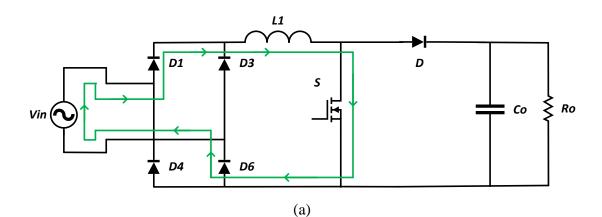

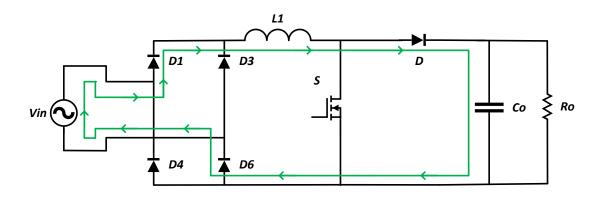

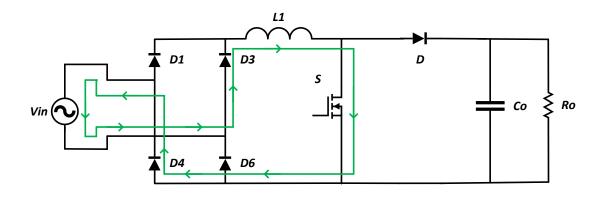

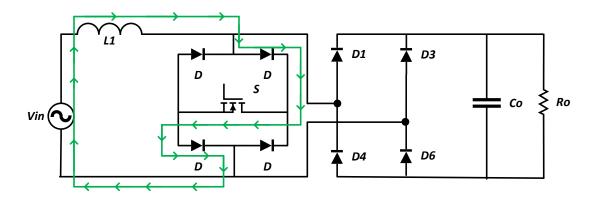

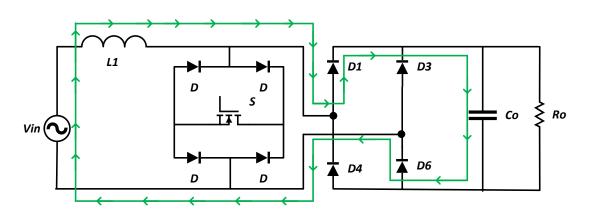

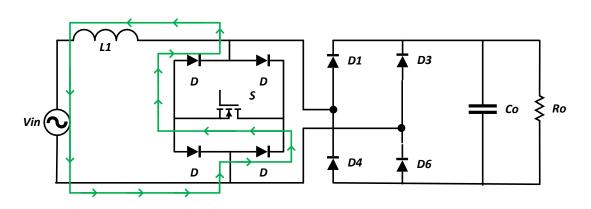

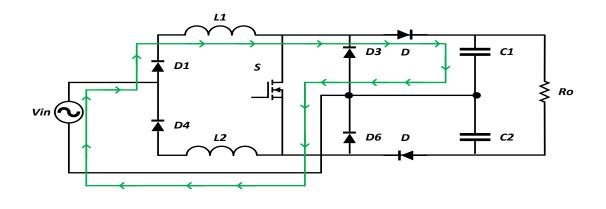

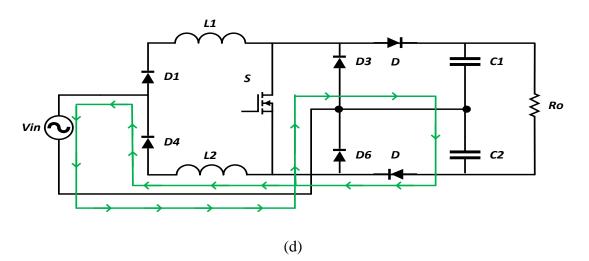

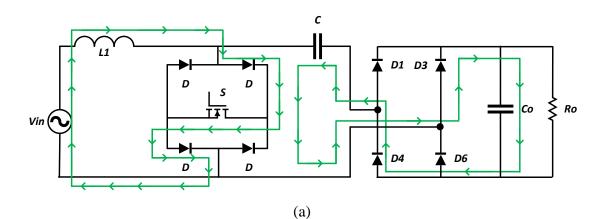

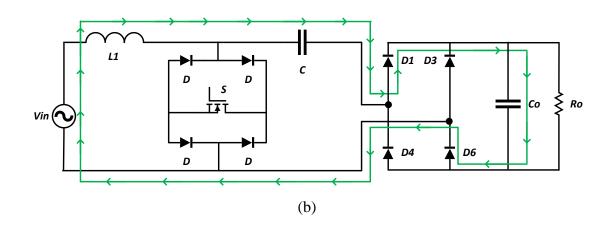

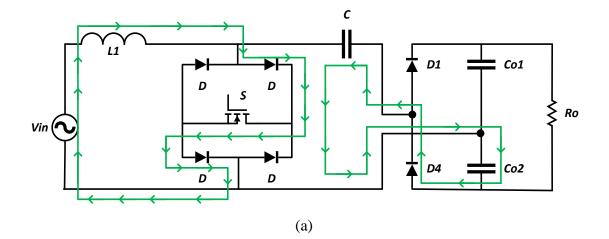

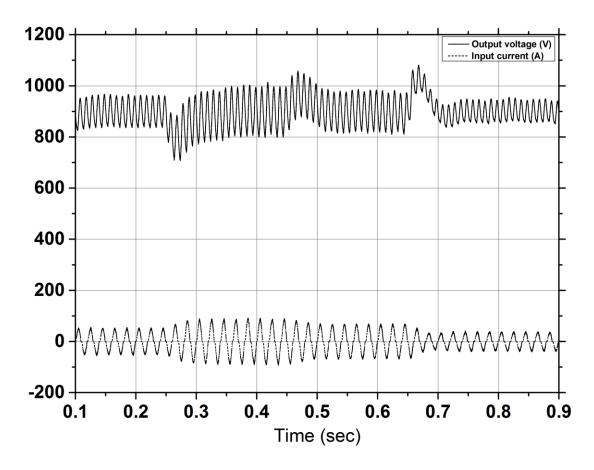

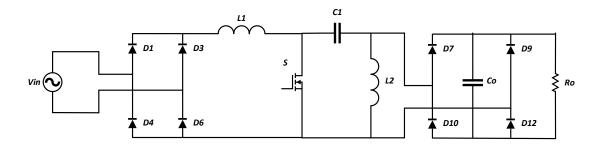

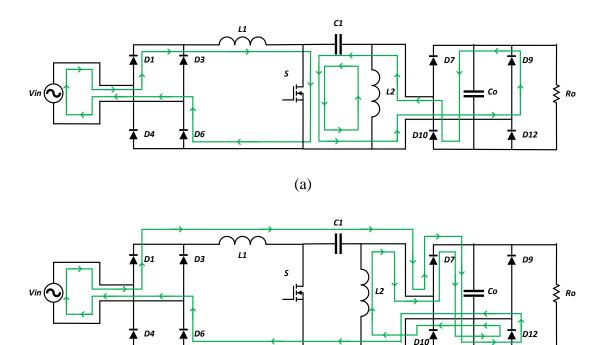

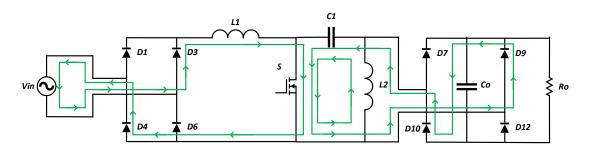

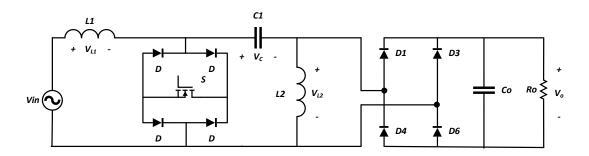

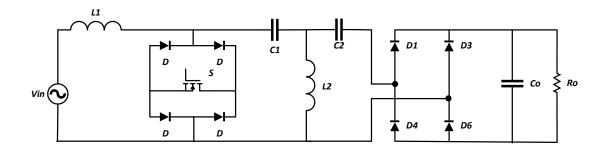

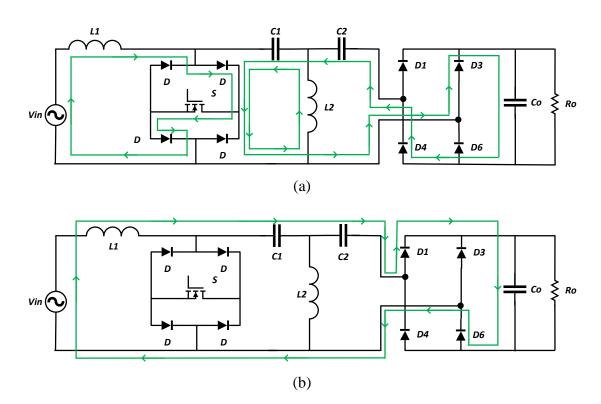

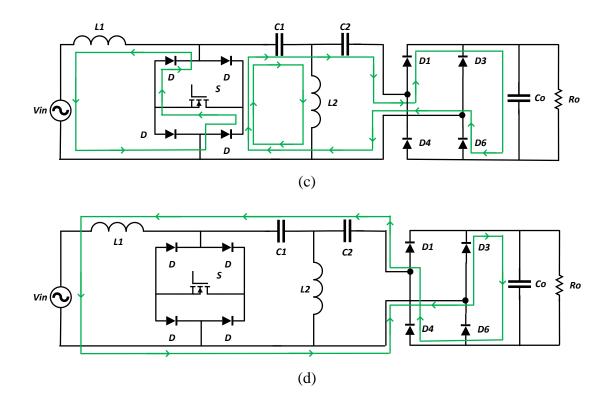

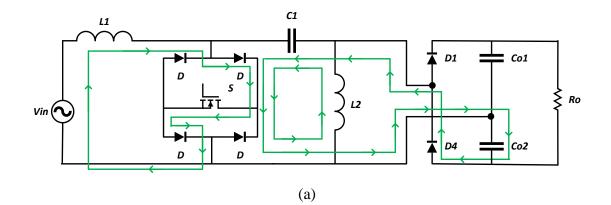

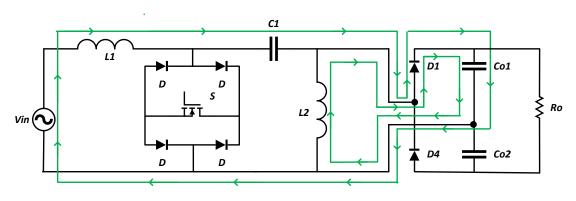

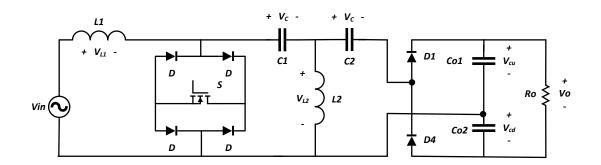

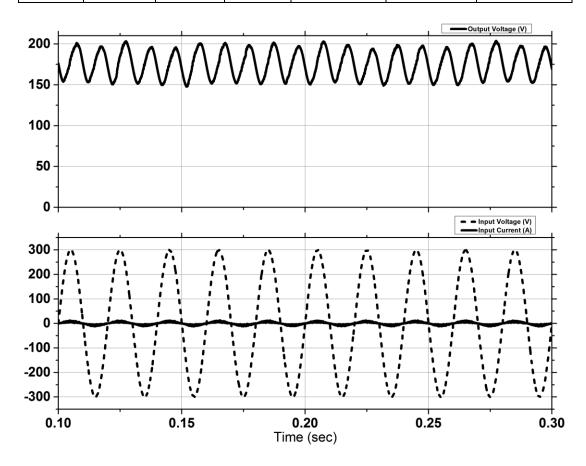

| Four steps of operation of the converter in Figure 3.7,            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |