# **Declaration of Authorship**

We, Ahmed Shariful Alam (092408), Abu Hena Md. Mustafa Kamal (092411) and Md. Abdur Rahman (092427), declare that this thesis titled, Structure and Operation of Single Electron Transistor (SET) and Its Circuit Implementation 'and the works presented in it are our own. We confirm that:

- This work has been done for the partial fulfillment of the Bachelor of Science in Electrical and Electronic Engineering degree at this university.

- Any part of this thesis has not been submitted anywhere else for obtaining any degree.

- Where we have consulted the published work of others, we have always clearly attributed the sources.

Submitted By:

Ahmed Shariful Alam (092408)

Abu Hena Md. Mustafa Kamal (092411)

Md. Abdur Rahman (092427)

# Structure and Operation of Single Electron Transistor and Its Circuit Implementation

Approved By:

Syed Iftekhar Ali Thesis Supervisor, Assistant Professor, Department of Electrical and Electronic Engineering, Islamic University of Technology.

Prof. Dr. Md. Shahid Ullah Head of the Department, Department of Electrical and Electronic Engineering, Islamic University of Technology.

### Structure and Operation of Single Electron Transistor and Its Circuit Implementation

A Thesis Presented to

The Academic Faculty

by

#### Ahmed Shariful Alam (092408) Abu Hena Md. Mustafa Kamal (092411) Md. Abdur Rahman (092427)

In Partial Fulfillment of the Requirements for the Degree B.Sc in Electrical and Electronic Engineering

#### Academic Year: 2012-2013

Islamic University Of Technology A Subsidiary Organ of the Organisation of Islamic Cooperation (OIC) Dhaka, Bangladesh.

October 2013

# Contents

| 1        | Intr | oduction To SET                                  | 11 |

|----------|------|--------------------------------------------------|----|

|          | 1.1  | Introduction                                     | 11 |

|          | 1.2  | History Of Single Electron Transistor            | 11 |

|          | 1.3  | Basic Physics of Single Electron Transistor      | 13 |

|          | 1.4  | Motivation                                       | 15 |

| <b>2</b> | SET  | <b>T</b> Structure And Operation                 | 17 |

|          | 2.1  | Introduction                                     | 17 |

|          | 2.2  | Physical Structure of Single Electron Transistor | 17 |

|          | 2.3  | Coulomb Blockade                                 | 22 |

|          | 2.4  | Theory of Operation                              | 25 |

|          | 2.5  | Stability Plot                                   | 28 |

|          | 2.6  | Regions of Operation and I-V characteristics     | 28 |

| 3        | Dua  | al Gate Single Electron Transistor               | 36 |

|          | 3.1  | Introduction                                     | 36 |

|          | 3.2  | Structure of Dual Gate SET (DGSET)               | 36 |

|          | 3.3  | DGSET operation                                  | 36 |

|          | 3.4  | Double Gate Single Electron Transistor Biasing   | 38 |

|          |      | 3.4.1 N-type DGSET                               | 40 |

|          |      | 3.4.2 P-type DGSET                               | 40 |

| <b>4</b> | Fab  | rication Techniques                              | 44 |

|          | 4.1  | Introduction                                     | 44 |

|          | 4.2  | SET Fabrication Techniques                       | 45 |

|          |      | 4.2.1 Shadow Mask Evaporation                    | 45 |

|          |      | 4.2.2 Step Edge Cut Off                          | 45 |

|          |      | 4.2.3 Planar Quantum Dots                        | 48 |

|          |      | 4.2.4 Poly Silicon Structures                    | 49 |

|          |      | 4.2.5 Gold Clusters                              | 50 |

|    | 4.3                | DGSET Fabrication Techniques                                   | 50              |

|----|--------------------|----------------------------------------------------------------|-----------------|

| 5  | <b>Im</b> p<br>5.1 | Dementation of SET in Simple Digital Circuits                  | <b>54</b><br>54 |

|    | $5.1 \\ 5.2$       |                                                                | $54 \\ 54$      |

|    |                    | SET Inverter                                                   |                 |

|    | 5.3                | Circuit Representation of SET Inverter                         | 54              |

|    | 5.4                | SET Inverter Operation                                         | 55              |

|    | 5.5                | Simple Digital Circuits using SET                              | 55              |

|    |                    | 5.5.1 2-input NAND Gate Using SET                              | 57              |

|    |                    | 5.5.2 2-input NOR Gate Using SET                               | 57              |

| 6  | The                | e model of SET                                                 | 62              |

|    | 6.1                | Introduction                                                   | 62              |

|    | 6.2                | The Model                                                      | 63              |

| 7  | Dig                | ital Circuits Using SET and Simulation Results                 | 67              |

|    | 7.1                | Introduction                                                   | 67              |

|    | 7.2                | SET Inverter                                                   | 67              |

|    |                    | 7.2.1 SET Inverter Siulation Not Considering Background Charge | 68              |

|    |                    | 7.2.2 SET Inverter Simulation Considering Background Charge .  | 74              |

|    |                    | 7.2.3 Best Biasing for SET Inverter                            | 81              |

|    | 7.3                | Some Digital Circuits Using SET                                | 82              |

|    |                    | 7.3.1 2-input NAND Gate                                        | 82              |

|    |                    | 7.3.2 2-input NOR Gate                                         | 83              |

|    |                    | 7.3.3 Half Adder                                               | 85              |

|    |                    | 7.3.4 Full Adder                                               | 87              |

| 8  | Cor                | clusion And Future Works                                       | 94              |

| 0  |                    |                                                                |                 |

|    | 8.1                | Summary And Conclusion                                         | 94<br>05        |

|    | 8.2                | Future Works                                                   | 95              |

| Bi | ibliog             | graphy                                                         | 97              |

# List of Figures

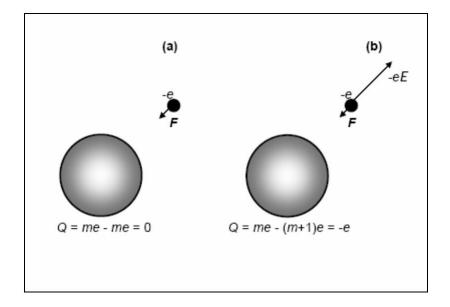

| 1.1 | The basic concept of single-electron control: a conducting island (a) |

|-----|-----------------------------------------------------------------------|

|     | before and (b) after the addition of a single electron. The addition  |

|     | of a single uncompensated electron charge creates an electric field   |

|     | E which may prevent the addition of the following electrons           |

|     | E which may prevent the addition of the following electrons                                   | 14 |

|-----|-----------------------------------------------------------------------------------------------|----|

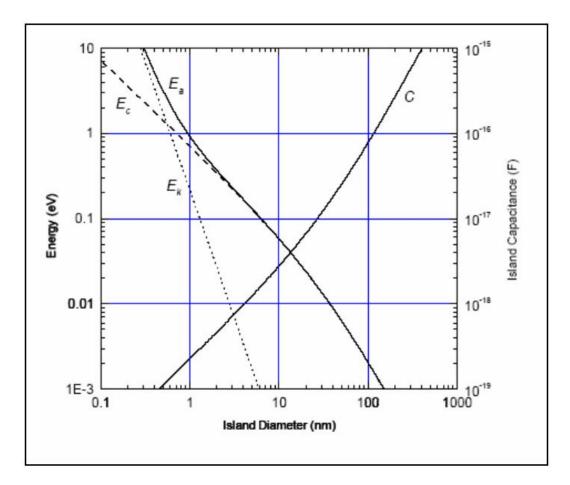

| 1.2 | Single-electron addition energy $E_a$ (solid line), and its components:                       |    |

|     | charging energy $E_c$ (dashed line) and electron kinetic energy $E_k$                         |    |

|     | (dotted line), as calculated using Eqs. $(1.1)$ and $(1.3)$ for a simple                      |    |

|     | model of a conducting island. In this model the island is a round                             |    |

|     | 3D ball with a free, degenerate electron gas (electron density $n =$                          |    |

|     | $1022 \ cm^3$ , electron effective mass $m = m_0$ ), embedded into a dielec-                  |    |

|     | tric matrix (dielectric constant, $\varepsilon_r = 4$ ), with 10 of its surface area          |    |

|     | occupied by tunnel junctions with a barrier thickness $\mathbf{d}=2$ nm. $% \mathbf{d}=2$ nm. | 16 |

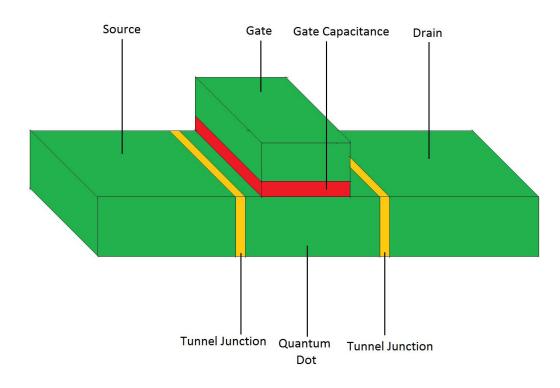

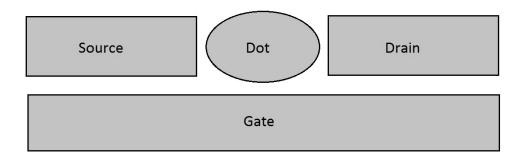

| 2.1 | Structural view of SET                                                                        | 18 |

| 2.2 | Schematic representation of SET                                                               | 19 |

| 2.3 | A 3-D representation of SET                                                                   | 20 |

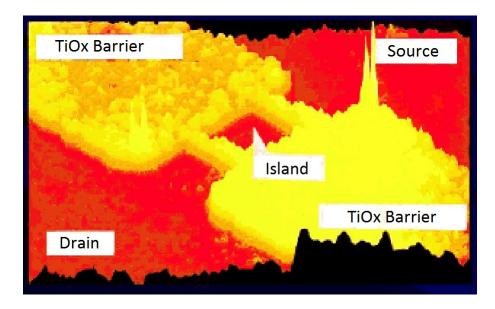

| 2.4 | An AFM (atomic force microscopy) image of a SET built by the                                  |    |

|     | STM (scanning tunneling microscope) nano-oxidation process. The                               |    |

|     | TiOx tunneling barrier shown here surrounds the quantum dot is-                               |    |

|     | land which is 35nm X 35nm in area, the width of the TiOx dielectric                           |    |

|     | is 20nm with a relative permittivity of $r=24$ and barrier height of                          |    |

|     | 285meV. With the 3-nm thick Ti blanket layer this structure ensures                           |    |

|     | small tunneling junction area and corresponding tunnel capacitance                            |    |

|     | becomes as small as 10-19 F, which allows the set to be operated at                           |    |

|     | room temperature                                                                              | 21 |

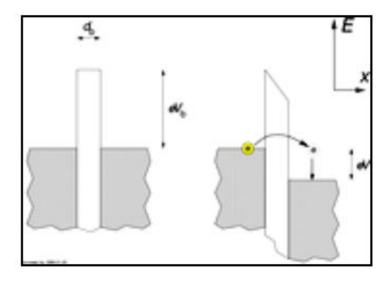

| 2.5 | Schematic representation of an electron tunneling through a barrier                           | 23 |

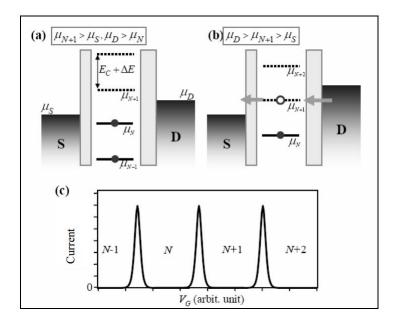

| 2.6 | Energy level of source, island and drain of a SET (left to right).                            |    |

|     | (Top) blocking stage and (Bottom) transmitting stage                                          | 23 |

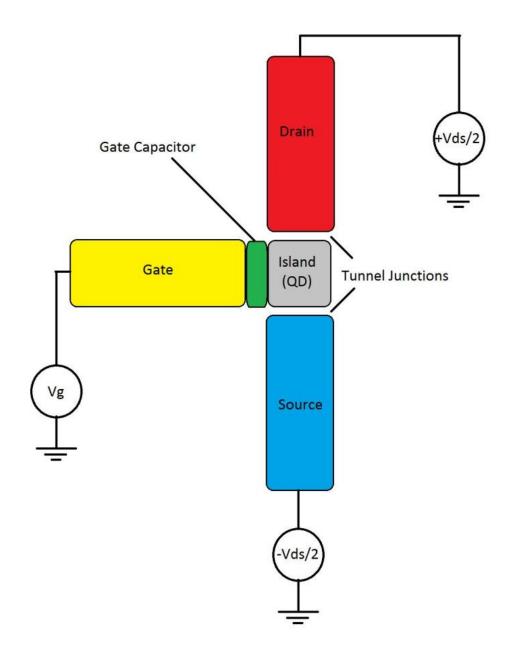

| 2.7        | The single electron transistor. A small dot is separated from the           |          |

|------------|-----------------------------------------------------------------------------|----------|

|            | source and drain electrodes by tunnel barriers. It is also coupled to       |          |

|            | the gate electrode capacitively.                                            | 26       |

| 2.8        | Electron transport in a single electron transistor and $I - V$ charac-      |          |

|            | teristics of SET                                                            | 26       |

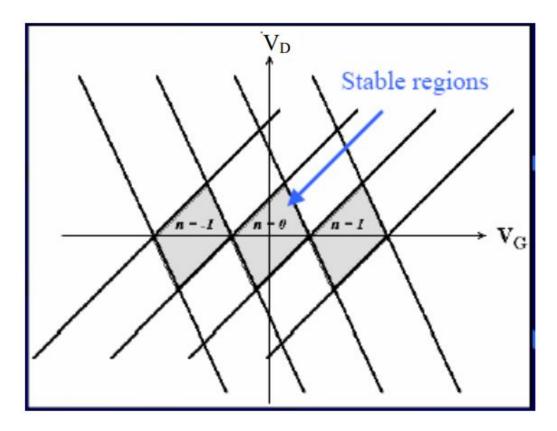

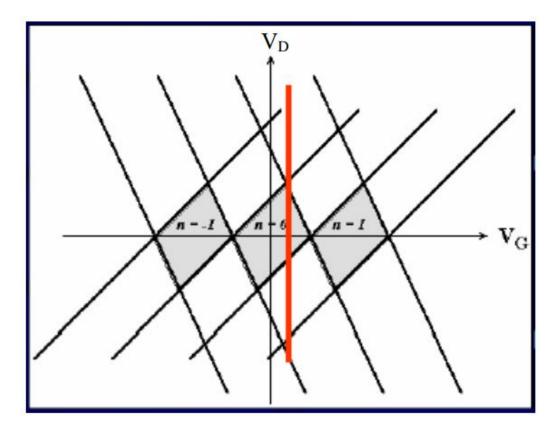

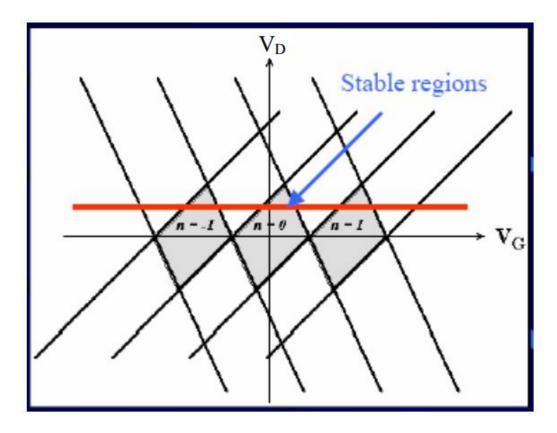

| 2.9        | Stability plot. Shaded diamonds corresponds to stable region where          |          |

|            | electron transportation is effectively suppressed by Coulomb blockade.      | 29       |

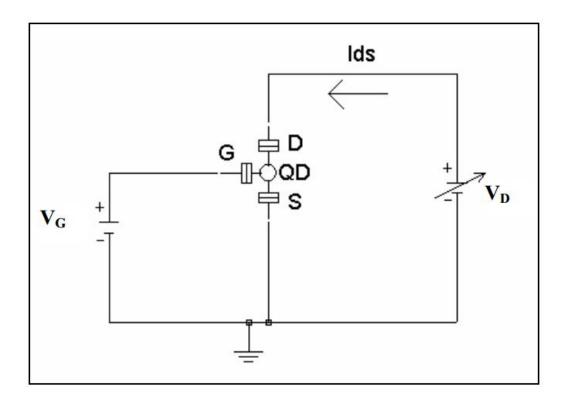

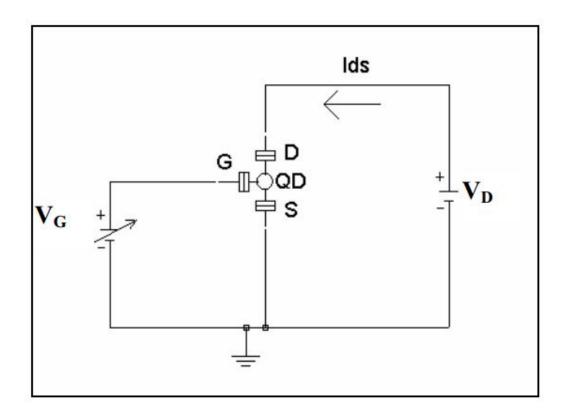

| 2.10       | A circuit setup for stability plot                                          | 30       |

| 2.11       | Stability plot. $V_D$ (connected to drain electrode) is being swept while   |          |

|            | gate bias is kept constant                                                  | 31       |

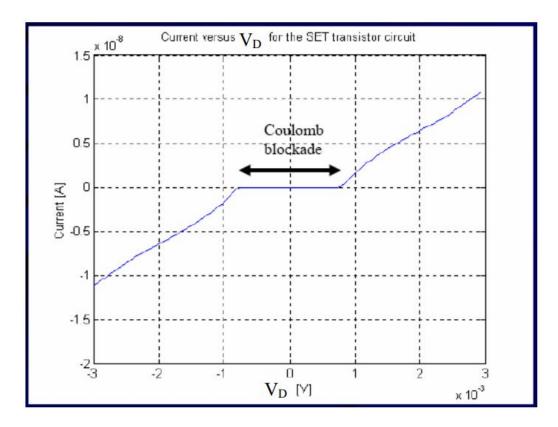

| 2.12       | $I_D$ vs $V_D$ characteristics for a fixed gate bias. Two unstable (tun-    |          |

|            | neling allowed) and stable (tunneling blocked) region are obvious           | 32       |

| 2.13       | Modified circuit setup for stability plot                                   | 33       |

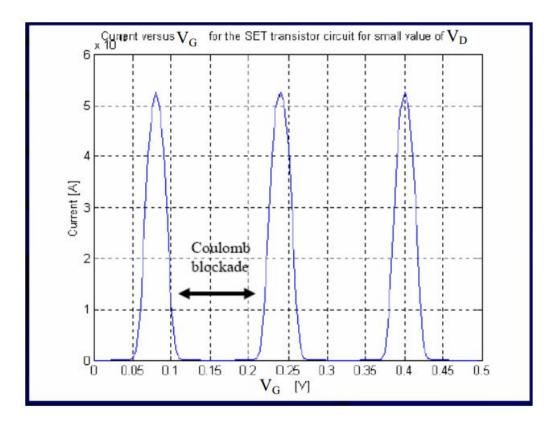

| 2.14       | Sweeping $V_G$ while $V_D$ is kept constant. The transistor undergoes       |          |

|            | repetitive stable and unstable regions resulting oscillation drain cur-     |          |

|            | rent                                                                        | 34       |

| 2.15       | I-V characteristics of SET. Coulomb oscillation with successive             |          |

|            | peaks and valleys resulting from the repetitive traversing of the           |          |

|            | transistor through unstable and stable regions                              | 35       |

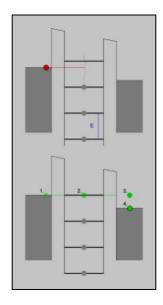

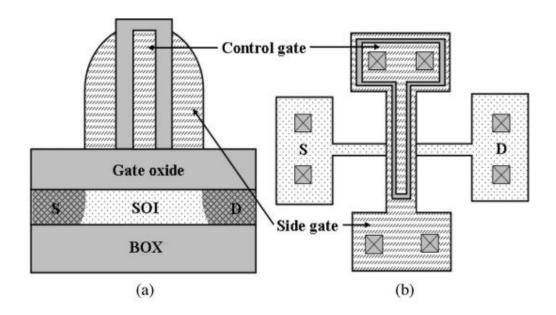

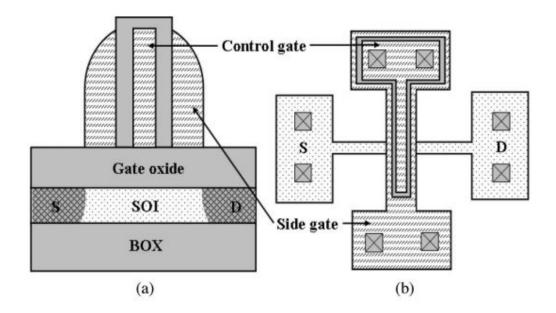

| 3.1        | (a) Structure and (b) top view of the fabricated device                     | 37       |

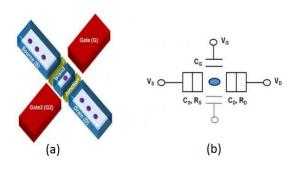

| 3.1<br>3.2 | (a) 3D structure and (b) circuit representation of DGSET                    | 37<br>37 |

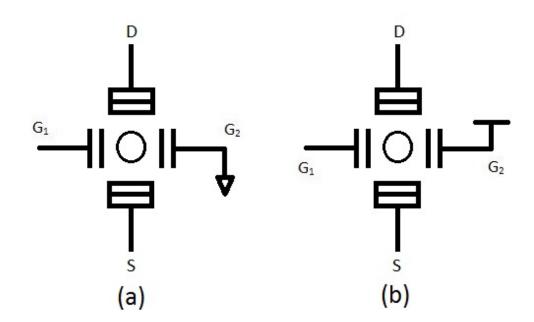

| 3.2<br>3.3 | (a) P-Type, (b) N-type SET configuration                                    | 39       |

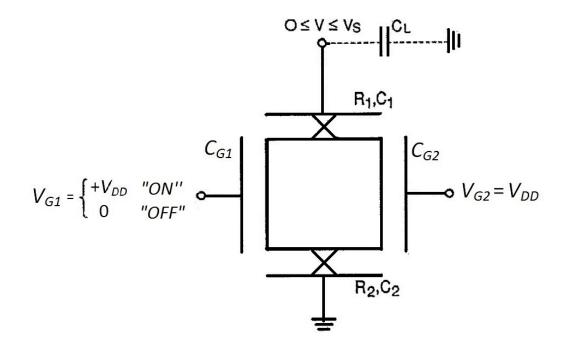

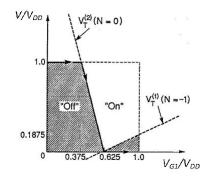

| 3.3<br>3.4 | Capacitively biased double-junction $n$ switch for digital logic appli-     | 39       |

| J.1        | cations. The switch is an open circuit for low gate voltage $V_{G1} = 0$ ,  |          |

|            | and drains charge off the output load capacitor $C_L$ when high gate        |          |

|            | voltage $V_{G1} = V_{DD}$ is applied                                        | 41       |

| 3.5        | Output voltage appearing on the load capacitor $C_L$ of the n switch        |          |

|            | in Fig. 3.4 as the gate voltage is swept quasistatically from off to        |          |

|            | on, $V_{G1} = [V_{DD}, 0]$                                                  | 41       |

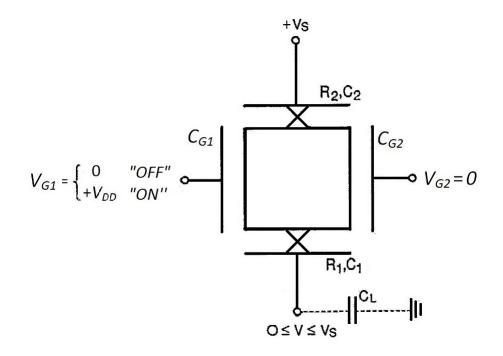

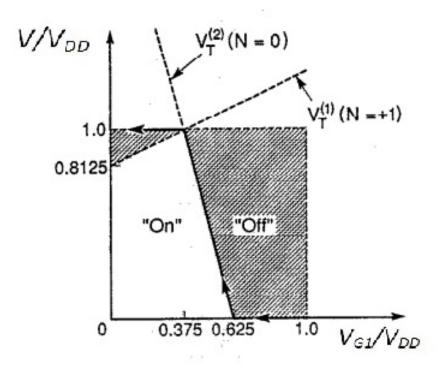

| 3.6        | Capacitively biased double-junction p switch for digital logic ap-          |          |

|            | plications. The switch is an open circuit for high gate voltage             |          |

|            | $V_{G1} = V_{DD}$ , and drains charge off the output load capacitor $C_L$   |          |

|            | when low gate voltage $V_{G1} = 0$ is applied $\ldots \ldots \ldots \ldots$ | 42       |

| 3.7        | Output voltage appearing on the load capacitor $C_L$ of the n switch        |          |

|            | in Fig. 3.6 as the gate voltage is swept quasistatically from off to        |          |

|            | on, $V_{G1} = [V_{DD}, 0]$                                                  | 43       |

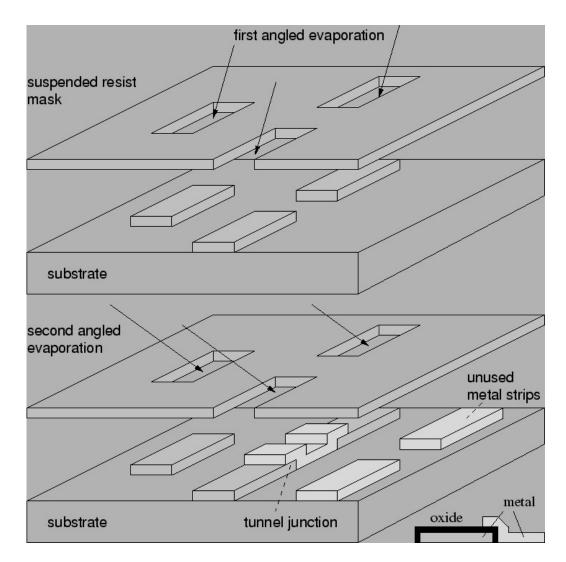

| 4.1 | Shadow mask evaporation. Two metal depositions followed by an oxidation and a further metal deposition from a different angle form |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

|     | an overlap of two stripes; a tunnel junction.                                                                                      | 46 |

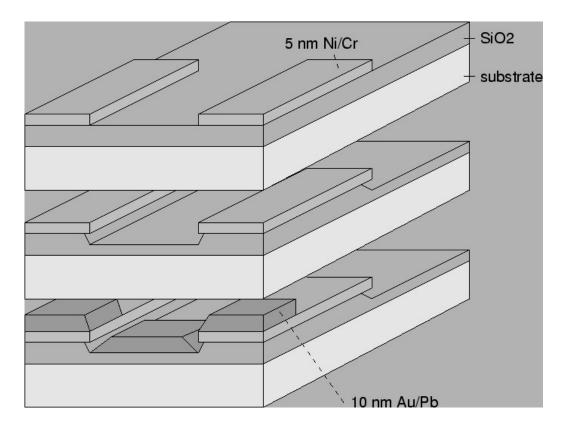

| 4.2 | Step edge cut-off method. A metal line is evaporated over a step edge                                                              | 47 |

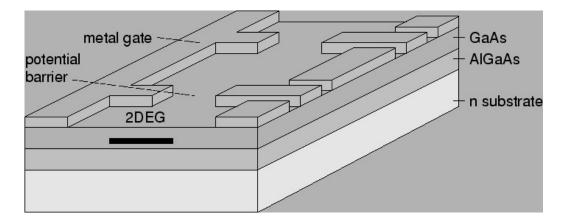

| 4.3 | Laterally patterned two-dimensional electron gas in a semiconduc-                                                                  |    |

|     | tor heterostructure. The fingers can be biased individually, which                                                                 |    |

|     | allows an independent change of barrier heights                                                                                    | 48 |

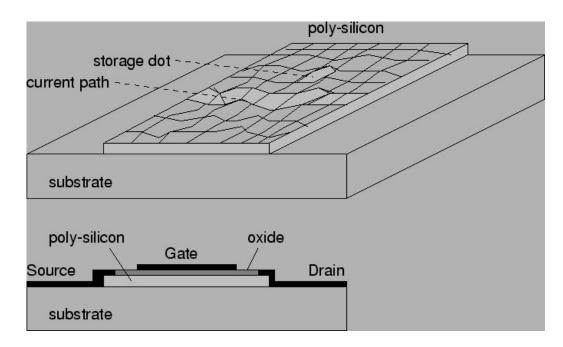

| 4.4 | Poly-silicon batch contacted with a source, drain, and gate elec-                                                                  |    |

|     | trode. In the upper part the electrodes and oxide are left out.                                                                    |    |

|     | This structure behaves like a flash memory, where one electron is                                                                  |    |

|     | stored/trapped on a grain that lies close enough                                                                                   | 49 |

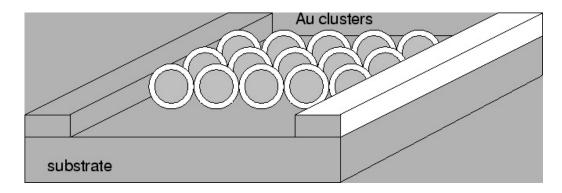

| 4.5 | Array of linked gold clusters. The gold clusters are grown as aerosol                                                              |    |

|     | particles, annealed, spread on a surface and linked with molecular                                                                 |    |

|     | wires                                                                                                                              | 50 |

| 4.6 | (a) Structure and (b) top view of the fabricated device                                                                            | 51 |

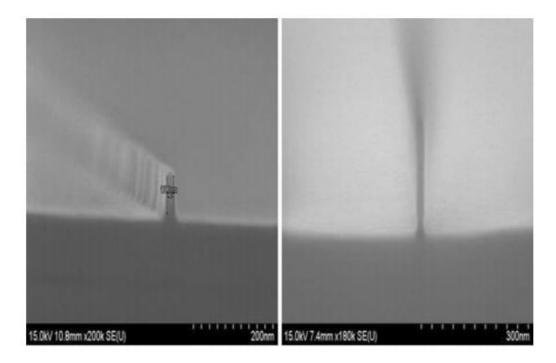

| 4.7 | Cross-sectional SEM images of e-beam lithography test wafer for (a)                                                                |    |

|     | active region (silicon) and (b) control gate (amorphous silicon). The                                                              |    |

|     | width of the defined active is 17 nm and the length of the control                                                                 |    |

|     | gate is 20 nm                                                                                                                      | 52 |

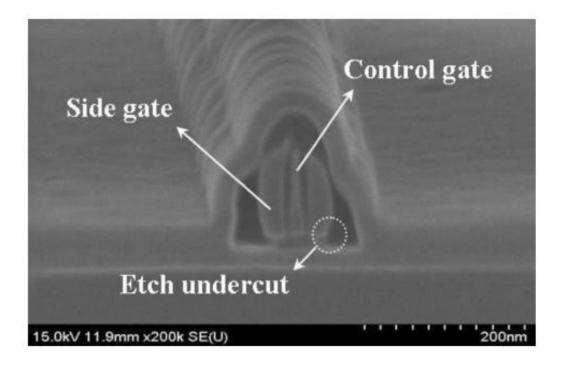

| 4.8 | Cross-sectional SEM image of test wafer for side gate formation.                                                                   |    |

|     | Due to over-etch, etch undercut effect makes the length of the side                                                                |    |

|     | gate bottom (25 nm) smaller than deposition thickness (30 nm).                                                                     |    |

|     | This result is advantageous for SET operation by reducing the tun-                                                                 |    |

|     | neling barrier width and decreasing the capacitance between the                                                                    |    |

|     | side gate and the quantum dot $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     | 53 |

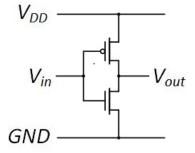

| 5.1 | Schematic diagram of a CMOS inverter                                                                                               | 55 |

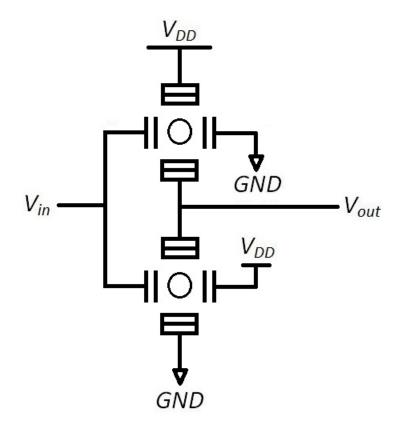

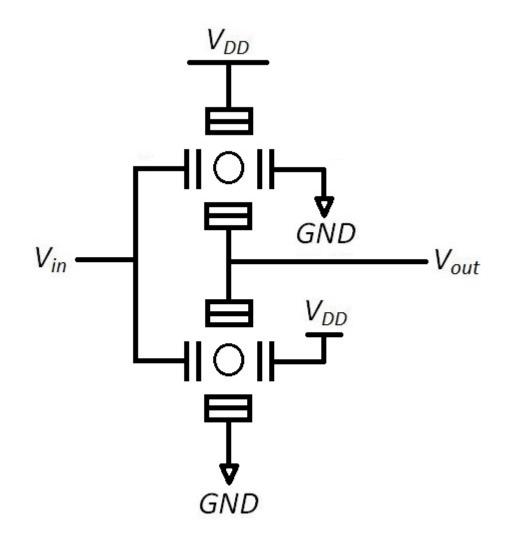

| 5.2 | Schematic diagram of CSET inverter                                                                                                 | 56 |

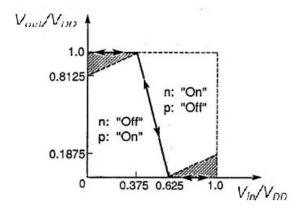

| 5.3 | Transfer characteristic of the inverter circuit in Fig. 5.2, calculated                                                            |    |

|     | for the example parameters given in Eq. 3.1                                                                                        | 57 |

| 5.4 | 2-input CMOS NAND gate                                                                                                             | 58 |

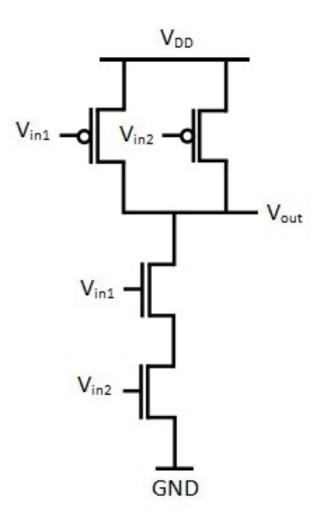

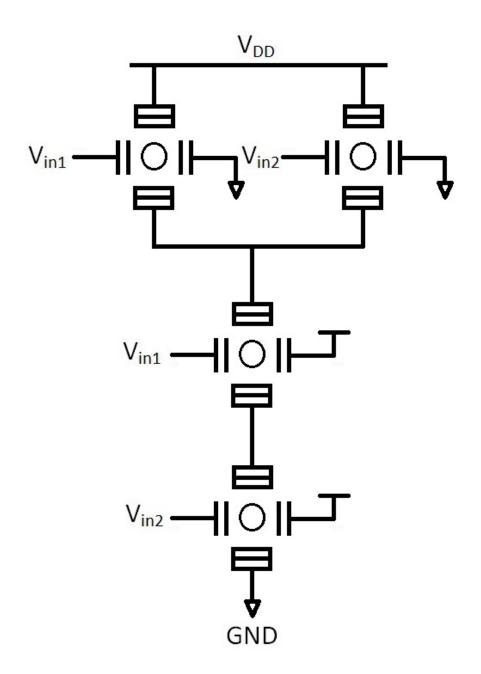

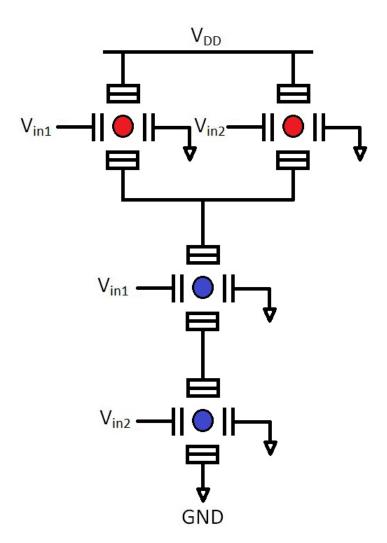

| 5.5 | 2-input CSET NAND gate                                                                                                             | 59 |

| 5.6 | 2-input CMOS NOR gate                                                                                                              | 60 |

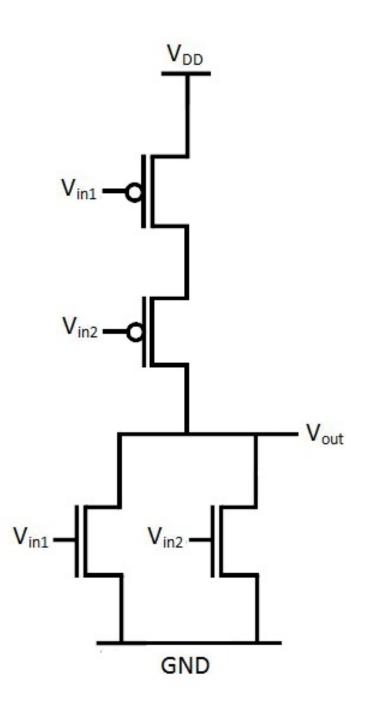

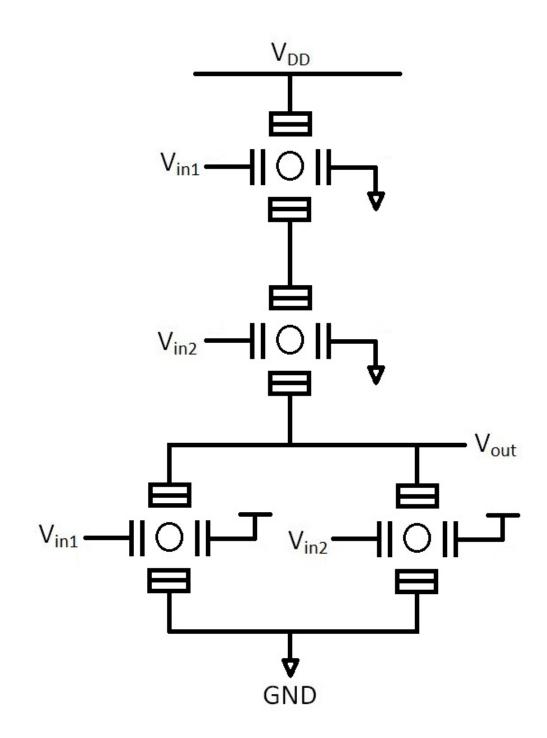

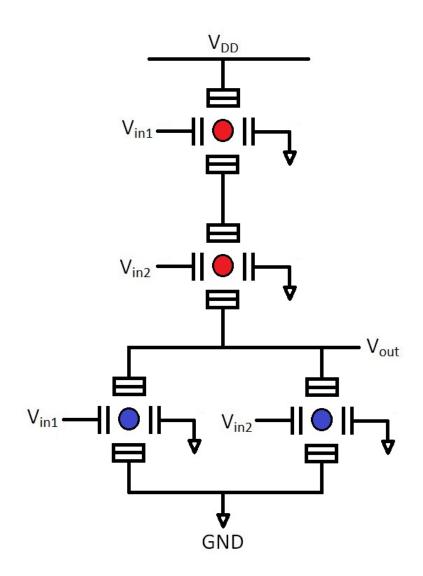

| 5.7 | 2-input CSET NOR gate                                                                                                              | 61 |

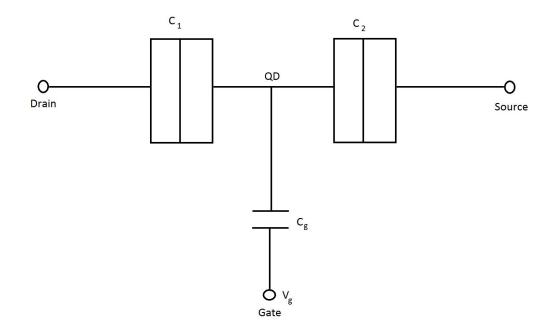

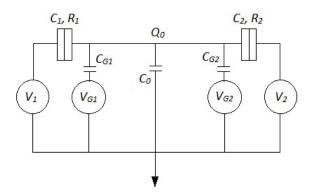

| 6.1 | A schematic diagram of a single-electron transistor showing the two                                                                |    |

|     | tunnel junctions, two gates, the stray capacitance $C_0$ , and the back-                                                           |    |

|     | ground charge $Q_0$                                                                                                                | 63 |

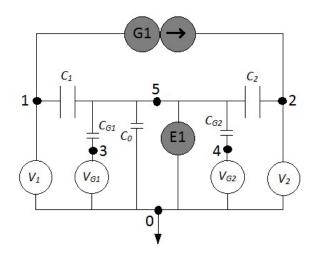

| 6.2   | The model of a SET in SPICE. The white voltage sources are ex-<br>ternal to the SET model and the gray sources are internal to the<br>model. E1 is a voltage source that fixes the voltage of the island of<br>the SET (node 5) using eq. (6.7) and G1 is a current source that<br>specifies the source - drain current using eq. (6.6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

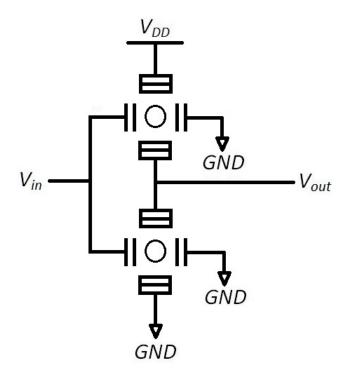

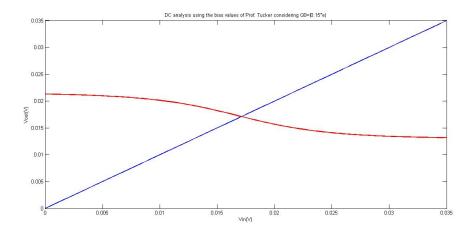

| 7.1   | SET Inverter using the bias value of <i>Professor Tucker</i> considering $Q_0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69       |

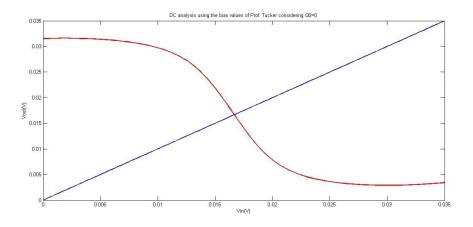

| 7.2   | $Q_0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 09<br>70 |

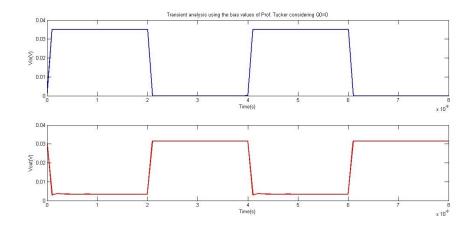

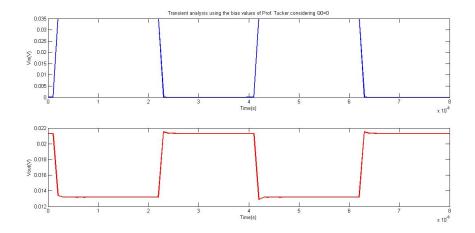

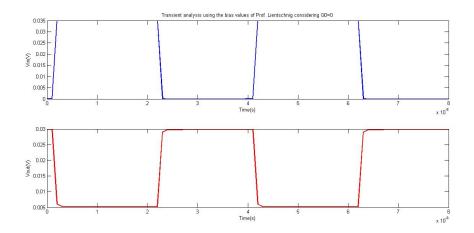

| 7.3   | Transient analysis using the bias values of <i>Professor Tucker</i> consid-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

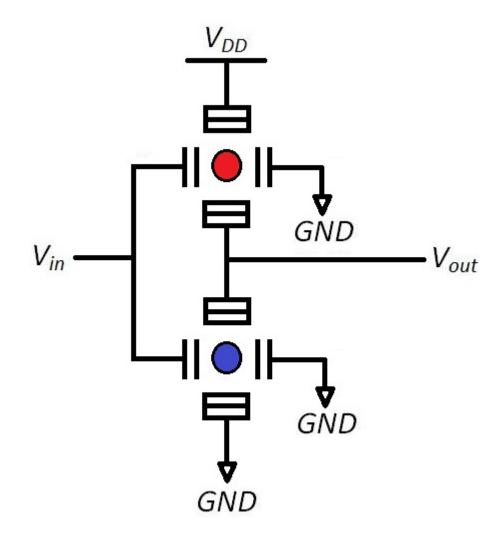

| 7.4   | ering $Q_0 = 0$<br>SET Inverter using the bias value of Professor Gather Lientschnig,<br>Professor Irek Weymann and Professor Peter Hadley considering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71       |

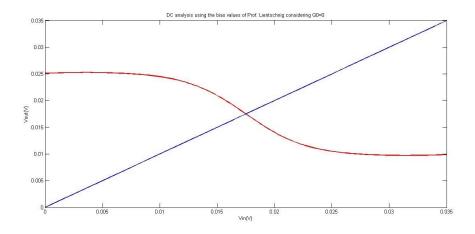

| 7.5   | $Q_0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72       |

|       | $Q_0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73       |

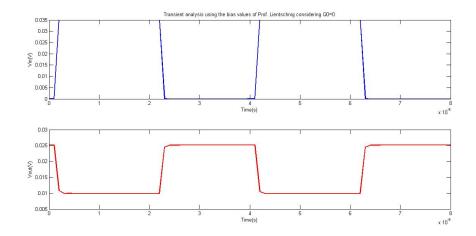

| 7.6   | Transient analysis using the bias values of Professor Gnther Lientschne<br>Professor Irek Weymann and Professor Peter Hadley considering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0,       |

| 7.7   | $Q_0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74       |

| 7.8   | $Q_0 =  1.5e $ DC analysis using the bias values of <i>Professor Tucker</i> considering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76       |

| 1.0   | $Q_0 =  1.5e $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77       |

| 7.9   | Transient analysis using the bias values of <i>Professor Tucker</i> consid-<br>sing $O_{1} = \frac{1}{2} \frac{5}{2} \frac{1}{2} $ | 77       |

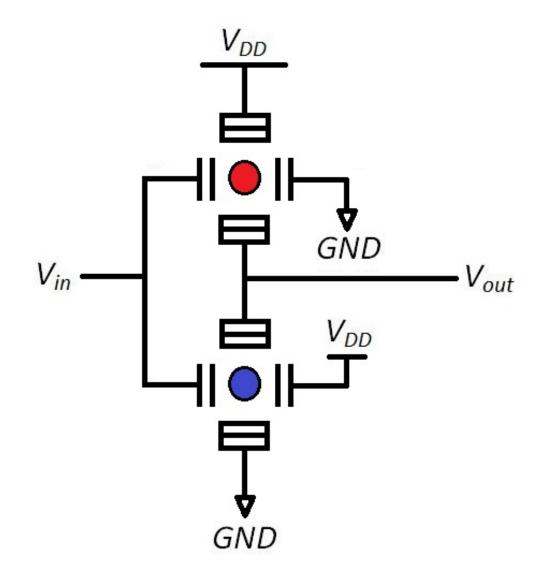

| 7.10  | ering $Q_0 =  1.5e $<br>SET Inverter using the bias value of <i>Professor Gather Lientschnig</i> ,<br><i>Professor Irek Weymann and Professor Peter Hadley</i> considering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77       |

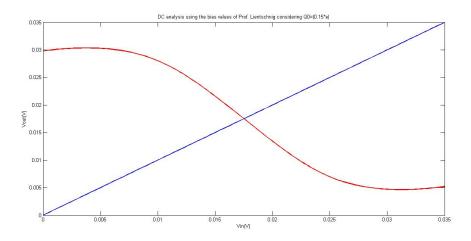

| 7.11  | $Q_0 =  1.5e $ DC analysis using the bias values of <i>Professor Gather Lientschnig</i> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79       |

|       | Professor Irek Weymann and Professor Peter Hadley considering<br>$Q_0 =  1.5e $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80       |

| 7.12  | Transient analysis using the bias values of Professor Gnther Lientschne<br>Professor Irek Weymann and Professor Peter Hadley considering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ig,      |

| = 10  | $Q_0 =  1.5e  \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80       |

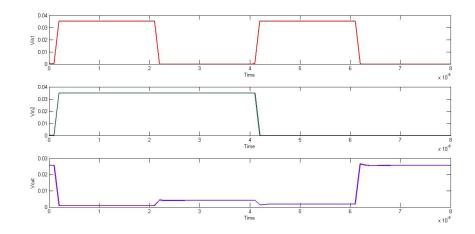

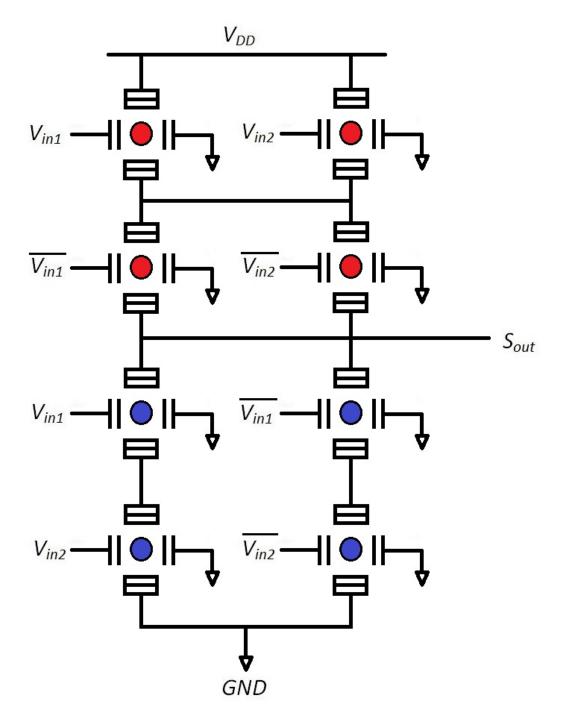

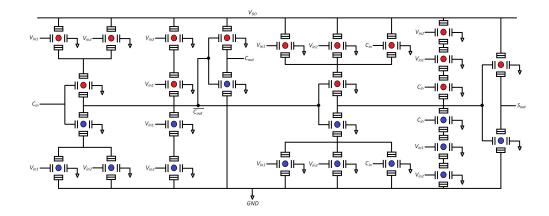

|       | 2-input NAND gate using SET with preferred bias values Transient Analysis of 2-input NAND gate using the preferred bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84       |

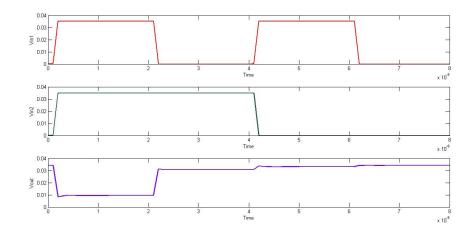

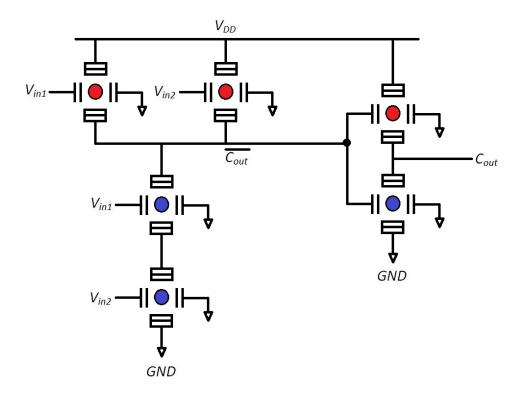

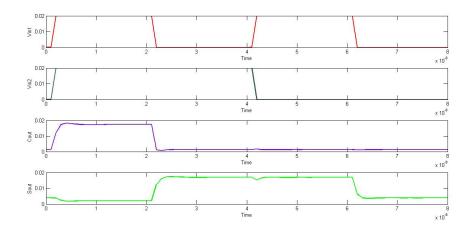

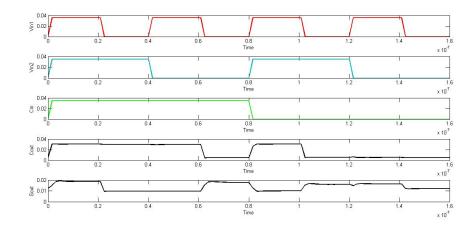

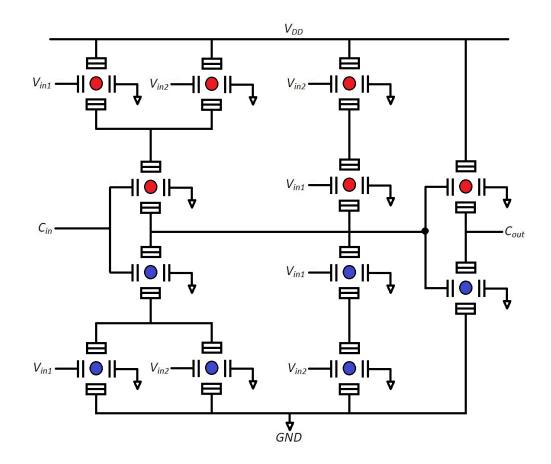

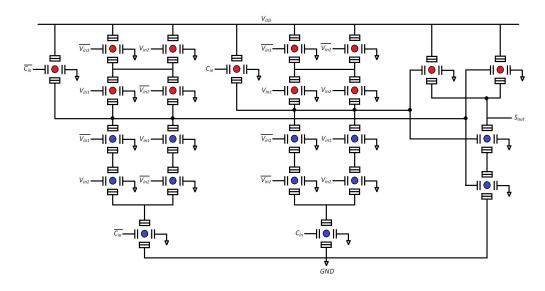

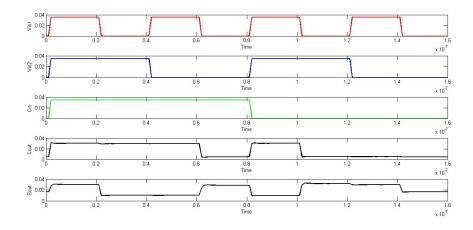

| 1.1.4 | values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85       |