# ISLAMIC UNIVERSITY OF TECHNOLOGY (IUT)

# **RESEARCH TREND AND POTENTIAL APPLICATION OF SPIN BASED DEVICE**

# BY

Mehedi Hasan

Shomi Ahmed

M. A. Aziz Jahan

A Dissertation

Submitted in Partial Fulfillment of the Requirement for the

**Bachelor of Science in Electrical and Electronic Engineering**

Academic Year: 2012-2013

Department of Electrical and Electronic Engineering. Islamic University of Technology (IUT) A Subsidiary Organ of OIC Dhaka, Bangladesh.

# A Dissertation on,

# **RESEARCH TREND AND POTENTIAL APPLICATION OF SPIN BASED DEVICE**

Submitted by

Mehedi Hasan(092402)

Shomi Ahmed (092474)

# Approved By

Prof. Dr. Md. Shahid Ullah Head of the Department Department of Electrical and Electronic Engineering Islamic University of Technology (IUT) Gazipur-1704, Bangladesh.

Supervised by

Syed Iftekhar Ali

Assistant Professor

Department of Electrical and Electronic Engineering

Islamic University of Technology (IUT)

Gazipur-1704, Bangladesh.

M. A. Aziz Jahan(092454)

## Abstract

This thesis is focused on the new technology evolved in the electronics field based on the spin property of electron that is Spintronics, at the interface between magnetism and electronics, which is a new field of research in considerable expansion. The basic concept of Spintronics is the manipulation of spin currents, in contrast to mainstream electronics in which the spin of the electron is ignored. Adding the spin degree of freedom provides new effects, new capabilities and new functionalities.

The article describes the development of Spintronics from the first studies of spin dependent transport in ferromagnetic materials to the discovery of the giant magnetoresistance and to the most recent advances. Everybody has already a spintronic device on their desktop, since the read heads of the hard disc drives of today use the giant magnetoresistance (GMR) phenomenon to read the magnetic information on the disc.

The GMR was the first step on the road of the utilization of the spin degree of freedom in magnetic nanostructures and triggered the development of an active field of research which has been called Spintronics. Today this field is extending considerably, with very promising new axes like the phenomena of spin transfer, Spintronics with semiconductors, molecular Spintronics or single-electron Spintronics etc.

In this review article we have tried to give an overall idea about the fundamentals of Spintronics, emergence of Spintronics in the field of data storage, Spintronics in the field of semiconductor and various Spintronic devices, their applications and future of Spintronics.

# Acknowledgements

At first every respect to the greatest Almighty Allah to give us the opportunity to do this work with patience for the last one year. This undergraduate thesis 'Research Trend and Potential application of Spin Based Device' is the result of our one year continuous hard work and effort and by far the most significant accomplishment in our life. This would be impossible without continuous support and appreciation of many people.

We would like to express our sincere gratitude to our supervisor "**Syed Iftekhar Ali**, Assistant Professor Department of Electrical and Electronic Engineering, Islamic University of Technology (IUT)" for his continuous guidance, support and enthusiasm for the last one year. Without the dedicated help of him this work would be impossible. He was always generous with his time, listening us carefully and criticizing us fairly.

We are also thankful to our departmental head Prof. Dr. Md. Shahid Ullah for his inspirations to complete the work. Finally we are grateful to all of our will-wishers, family members, friends and relatives for their support for this whole time to accomplish this task successfully.

# Contents

| Abstract |                                                                   | 3  |

|----------|-------------------------------------------------------------------|----|

| Acknowl  | edgements                                                         | 4  |

| Chapter  | 1 Introduction                                                    | 8  |

|          | 1.1 Spintronics Definition                                        | 8  |

|          | 1.2 Fundamentals of Spin                                          | 9  |

|          | 1.3 Basic Scheme                                                  | 10 |

|          | 1.4 Electronics vs. Spintronics                                   | 10 |

|          | 1.5 Brief History                                                 | 10 |

| Chapter  | 2 Emergence of Spintronics in the field of Data Storage           | 12 |

|          | 2.1. Anisotropic magnetoresistance (AMR)                          | 12 |

|          | 2.1.1 AMR Head Challenges                                         | 14 |

|          | 2.2 GMR Technology                                                | 15 |

|          | 2.2.1 How GMR Sensors Work                                        | 17 |

|          | 2.3 Spin Valve                                                    | 19 |

|          | 2.4 Magnetic Tunnel Junction (MTJ)                                | 21 |

|          | 2.5 Magnetoresistive Random-Access Memory (MRAM)                  | 22 |

|          | 2.5.1 MRAM: Reading and Writing process                           | 24 |

|          | 2.5.2 Application of MTJ Based MRAM                               | 25 |

|          | 2.5.3 Problems associated with MRAM                               | 26 |

| 4        | 2.6 Spin-Torque Transfer Magnetic RAM (STT MRAM)                  | 26 |

|          | 2.6.1 Operating Principle of STT MRAM                             | 28 |

|          | 2.6.2 STT-MRAM to Reduce Issues Associated with Conventional MRAM | 29 |

| Chapter  | 3 Spin Transistor                                                 | 30 |

|          | 3.1 Requirements for spin transistor                              | 32 |

|          | 3.2 Fundamental of spin transistor                                | 33 |

|          | 3.2.1 Two-Terminal Magnetoresistive Devices                       | 33 |

| 3.2.2 Spin Injection and the Conductivity Mismatch Problem                                                                                                                                                                                                                                                                                          | 36                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3.2.3 Spin Relaxation in Semiconductors                                                                                                                                                                                                                                                                                                             | 40                                                 |

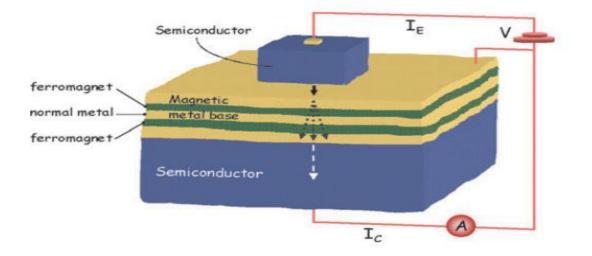

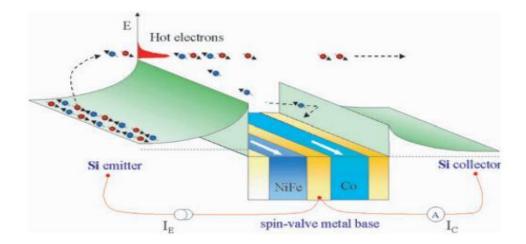

| 3.3 Spin Valve Transistor                                                                                                                                                                                                                                                                                                                           | 42                                                 |

| 3.3.1. Basic Device Structure and Properties                                                                                                                                                                                                                                                                                                        | 42                                                 |

| 3.3.2 The Operation of the SVT                                                                                                                                                                                                                                                                                                                      | 44                                                 |

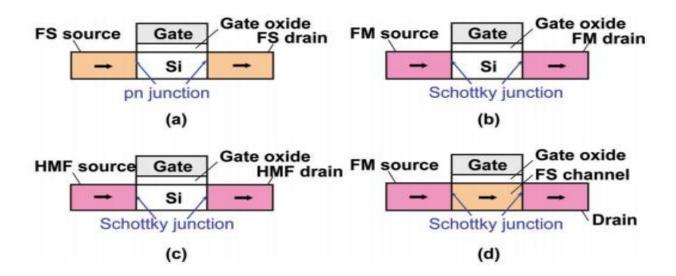

| Chapter 4 Spin MOSFET                                                                                                                                                                                                                                                                                                                               | 46                                                 |

| 4.1 Device Structures and Material Candidates                                                                                                                                                                                                                                                                                                       | 46                                                 |

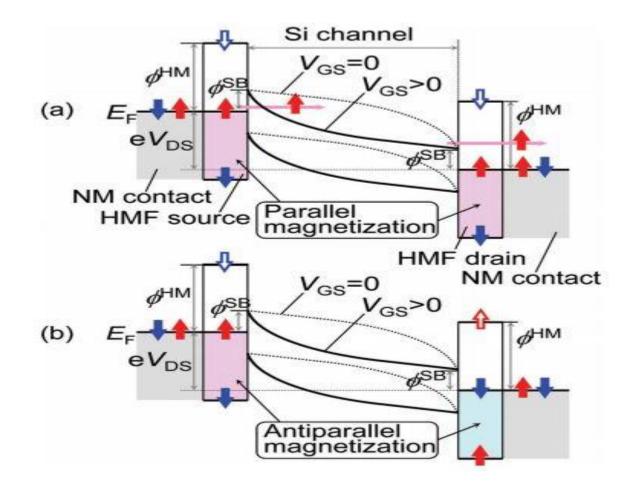

| 4.2 Operation Principle of the Spin MOSFET with HMF Contacts for the Source/Drain                                                                                                                                                                                                                                                                   | 48                                                 |

| 4.3. Operation Principle of the Spin MOSFET with an FS Channel                                                                                                                                                                                                                                                                                      | 50                                                 |

| 4.4. Reconfigurable Logic Gates Using Spin MOSFET                                                                                                                                                                                                                                                                                                   | 51                                                 |

| 4.4.1 Reconfigurable AND / OR Gate                                                                                                                                                                                                                                                                                                                  | 53                                                 |

| 4.4.2 Logic Operations of the Reconfigurable AND/OR Gate                                                                                                                                                                                                                                                                                            | 55                                                 |

|                                                                                                                                                                                                                                                                                                                                                     | = (                                                |

| Chapter 5 Spintronic Devices                                                                                                                                                                                                                                                                                                                        | 56                                                 |

| 5.1 Spin Transfer Nano-Oscillators (STNO)                                                                                                                                                                                                                                                                                                           | <b>56</b>                                          |

|                                                                                                                                                                                                                                                                                                                                                     |                                                    |

| 5.1 Spin Transfer Nano-Oscillators (STNO)                                                                                                                                                                                                                                                                                                           | 56                                                 |

| <ul><li>5.1 Spin Transfer Nano-Oscillators (STNO)</li><li>5.1.1 Operating Principle</li></ul>                                                                                                                                                                                                                                                       | 56<br>57                                           |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> </ul>                                                                                                                                                                                                          | 56<br>57<br>58                                     |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> </ul>                                                                                                                                                                            | 56<br>57<br>58<br>58                               |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> <li>5.1.22 Linewidth</li> </ul>                                                                                                                                                  | 56<br>57<br>58<br>58<br>60                         |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> <li>5.1.2.2 Linewidth</li> <li>5.1.3 Advantages of STNOs over Standard VCO</li> </ul>                                                                                            | 56<br>57<br>58<br>58<br>60<br>60                   |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> <li>5.1.2.2 Linewidth</li> <li>5.1.3 Advantages of STNOs over Standard VCO</li> <li>5.2 DMS-based Sensors</li> </ul>                                                             | 56<br>57<br>58<br>58<br>60<br>60<br>61             |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> <li>5.1.2.2 Linewidth</li> <li>5.1.3 Advantages of STNOs over Standard VCO</li> <li>5.2 DMS-based Sensors</li> <li>5.3 Spin Amplifier</li> </ul>                                 | 56<br>57<br>58<br>60<br>60<br>61<br>63             |

| <ul> <li>5.1 Spin Transfer Nano-Oscillators (STNO)</li> <li>5.1.1 Operating Principle</li> <li>5.1.2 Output Power and Linewidth</li> <li>5.1.2.1 Output Power</li> <li>5.1.2.2 Linewidth</li> <li>5.1.3 Advantages of STNOs over Standard VCO</li> <li>5.2 DMS-based Sensors</li> <li>5.3 Spin Amplifier</li> </ul> Chapter 6 Future of Spintronics | 56<br>57<br>58<br>58<br>60<br>60<br>61<br>63<br>64 |

|           | 6.4 The Spin Diode                                                             | 65 |

|-----------|--------------------------------------------------------------------------------|----|

|           | 6.5 Spin-split Insulator as a Polarizing Injector—Application to Semiconductor | 65 |

| Injection | n                                                                              |    |

|           | 6.6 Novel Fast Switching MRAM Storage Element                                  | 66 |

|           | 6.7 Quantum–coherent Spin Electronics                                          | 66 |

|           | 6.8 The Tunnel-grid Spin Triode                                                | 67 |

| Summa     | ry and Outlook                                                                 | 68 |

| Referen   | ces                                                                            | 69 |

# **Chapter 1**

## Introduction

Back in 1965 Intel co-founder Gordon E Moore predicted (which famously known as Moore's Law) that "The number of transistors on a chip will double in every two years." That means more number of transistors are integrated on a smaller chip as days pass. But Moore's Law will run out of momentum very soon as the size of transistors approaches the dimension of atoms—this has been called the end of the silicon road map. Researchers are now seeking new concepts of electronics that sustain the growth of computing power. One promising solution is called "Spintronics", which is based on the "spin" property of electrons as they are being transmitted. It also enhance the multi functionality of devices i.e. carrying out processing and data storage on the same chip. The spin orientation of conduction electrons survives for a relatively long time (nanosecond). This property of spin based system makes Spintronics devices particularly attractive for memory storage, magnetic sensor applications, and potentially for quantum computing, where electron spin would present as a bit of information.

There have been many other reviews written on Spintronics, most focusing on a particular aspect of the field.

We divide them here, for an easier orientation, the spin based field into two main categoriesnamely

- 1. Spin based memory devices.

- 2. Spin based semiconductor.

We found enormous development in first category. And only theoretical success in second category. Let us first define the term Spintronics and logic behind spin based devices.

#### **1.1 Spintronics Definition**

The word "Spintronics" refers to the devices that take advantage of electrons' quantum property called "spin". It is a new branch of electronics in which electron spin, in addition to charge, is

manipulated to yield a desired outcome. It is an emerging field that exploits the fact that current flowing through transistors, that are made of certain materials, can store data not only as charge but as magnetic moment.

## **1.2 Fundamentals of Spin**

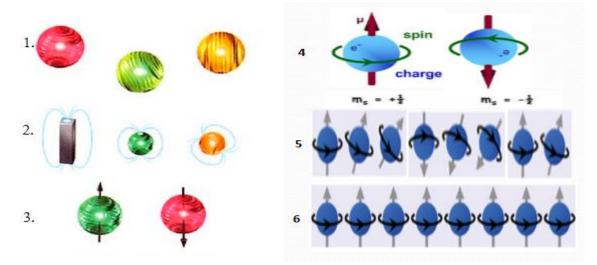

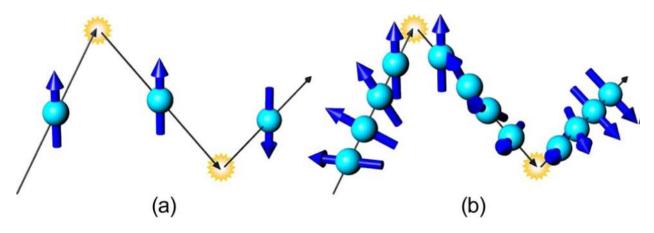

- 1) In addition to their mass and electric charge, electrons have an intrinsic quantity of angular momentum called spin, almost as if they were tiny spinning balls.

- 2) Associated with the spin is a magnetic field like that of a tiny bar magnet lined up with the spin axis.

- 3) Scientists represent the spin with a vector. For a sphere spinning "west to east" the vector points "north" or "up". It points "down" for the opposite spin.

- 4) In a magnetic field, electrons with "spin up" and "spin down" have different energies.

- 5) In an ordinary electric circuit the spins are oriented at random and have no effect on current flow.

- 6) Spintronic devices create spin-polarized currents and use the spin to control current flow

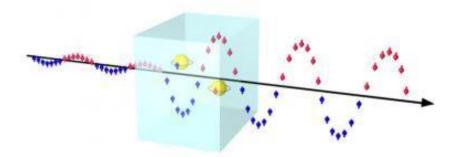

Figure 1.1 Fundamentals of Spin [1].

### **1.3 Basic Scheme**

A spintronic device has a basic scheme-

- > First, information is stored into spins as an orientation (i.e. up or down).

- Then, the spins that are attached to mobile electrons carry information along a path or wire.

- > The information is then read at a terminal point.

### **1.4 Electronics vs. Spintronics**

The movement of spin, like the flow of charge, can also carry information among devices.

So, what is the advantage of spin property of electrons?

One advantage of spin over charge is that spin can be easily manipulated by externally applied magnetic fields, a property already in use in magnetic storage technology (GMR).

Another more subtle (but potentially significant) property of spin is its relaxation time—once created it tends to stay that way for a long time, unlike charge states, which are easily destroyed by scattering or collision with defects, impurities or other charges.

These characteristics open the possibility of developing devices that could be much smaller, consume less electricity and be more powerful for certain types of computations than is possible with electron-charge-based systems (Electronics).

### **1.5 Brief History**

Spintronics emerged from discoveries in the 1980s concerning spin-dependent electron transport phenomena in solid-state devices. These includes-

**1985:** The observation of spin-polarized electron injection from a ferromagnetic metal to a normal metal by Johnson and Silsbee.

**1988:** Discovery of Giant Magneto Resistance (GMR) independently by Albert Fert and Peter Grünberg opened the way to efficient control of charge transport through magnetization. And for

their work they had been awarded Nobel Prize in Physics in 2007 and also the field of spintronics was recognized. The recent expansion of hard-disk recording owes much to this development. Mainly scientists began developing new spin-based electronics, beginning with this discovery.

**1990:** The theoretical proposal of a spin field-effect-transistor by Datta and Das. The idea of semiconductor spintronics came from this proposal.

**2012:** In the study published in *Nature*, IBM Research and the Solid State Physics Laboratory at ETH Zurich announced they had found a way to synchronize electrons, which could extend their spin lifetime by 30 times to 1.1 nanoseconds, the time it takes for a 1 GHz processor to cycle [2].

# **Chapter 2**

## Emergence of Spintronics in the field of Data Storage (Spin Based Memory Devices)

In the information era, a new promising science (Spintronics) has been strongly addressed which has produced a breakthrough and diffusion in technological products (mainly in memory) based on the spin property of electron. We are only habituated with the charge property of electrons, but electrons have both charge and spin, which were considered separately until very recently. In classical electronics, charges are moved by electric fields to transmit information and are stored in a capacitor to save it. For more than thirty years physicists and engineers devoted their researches and efforts mostly to charge-transfer devices, developing the actual semiconductor industry and granting to it a tremendous growth rate, witnessed by the well-known Moore law: the doubling of computation speed (proportional to the transistor number per chip1) every 18 months [27]. However scientist faced a lot of problem in scaling of such devices. Spintronic devices come as a revolution to face those problems. Now a days the principal application of spintronic devices is in the field of magnetic data storage which can have information density growth rate faster than the corresponding Moore law. The discovery of Giant magnetoresistance (GMR) causes a revolutionary change in the field of data storage, which opened the way to efficient control of charge transport through magnetization. The recent expansion of hard-disk recording owes much to this development. We are starting to see a new paradigm where magnetization dynamics and charge currents act on each other in nanostructured artificial materials. In the following articles we have tried to give some idea about the spintronic devices in the field of data storage.

#### 2.1 Anisotropic magnetoresistance (AMR)

The interdependence between magnetization and charge transport is not a new story. For instance, anisotropic magnetoresistance (AMR), which links the value of the resistance to the respective orientation of magnetization and current, was first observed in 1856 by William Thomson, but its amplitude was weak (up to a few per cent variation in resistance on changing the relative orientation of magnetization and current). Nevertheless, the introduction by IBM in 1991 of a magnetoresistive read head based on AMR was a major technological step forward [28].

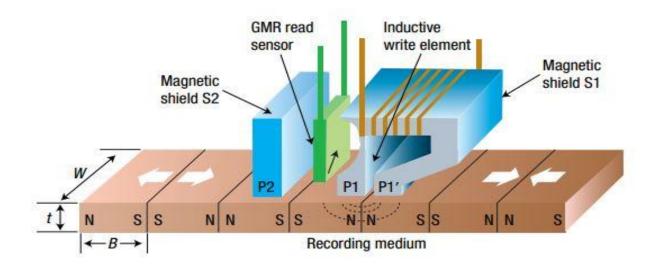

**Fig 2.1:** Schematic structure of the magnetoresistive head for hard-disk recording introduced by IBM for its hard disk drives in 1991. A magnetic sensor based on anisotropic magnetoresistance (left) is added to the inductive 'ring-type' head (right) still used for writing. The distances  $p_1-p_1$ ' and  $p_1-p_2$  between the pole pieces of the magnetic shields s1 and s2 define respectively the 'write' and 'read' gaps, on which depends the minimum length 'B' of the magnetic domains. 'W' is the track width and 't' is the thickness of the recording medium. Note that in today's hard disk recording, 'W' and 'B' are of the order of 100 nm and 30 nm respectively, but with a different arrangement of head and domains in 'perpendicular recording'.

IBM developed AMR technology, based on the principle that certain metals undergo changes in electrical resistance in the presence of a magnetic field. AMR heads allowed IBM to store 1 gigabit on one square inch of magnetic recording media, and areal densities have increased to over 3 gigabits per square inch.

In hard disk drives (HDD), the head flies at constant height above the magnetic domains that define the 'bits' in the recording medium, and senses the spatial variations of the stray magnetic field of these domains. Error rate, the number of data bits correctly decoded by the recording head and fly height, the distance between the read/write elements of the head and the magnetic layer of the media are key design parameters in the quest for higher areal density. Designers strive to keep error rate and fly height as large as possible. Error rate for performance reasons and fly height for reliability. For a given head technology, however, these are mutually exclusive goals. To achieve higher areal densities with thin film inductive (TFI) heads, fly heights had to decrease in order to maintain acceptable error rates. Increasing the ability of the head to detect magnetic signals (i.e. head sensitivity) and slow the rate at which fly height decreased was possible for a time. Eventually, new technologies were needed. Hence the development and introduction of Magneto-Resistive (MR), both anisotropic and giant magnetoresistive, technology. Anisotropic Magnetoresistive (AMR) head technology is currently the primary read/write head technology used in hard drives, replacing TFI heads. AMR heads were introduced first in mobile drives around 1994 and in desktop drives around 1995. Today, all of Western Digital's current desktop and enterprise class (workstations, servers, RAID systems) of hard drives incorporate AMR heads to meet ever increasing capacity requirements. Unlike TFI heads, where the read and write elements are the same, read and write elements in the AMR head are separate in order to optimize read and write capabilities. The write element is a conventional TFI head, while the read element in an AMR head is composed of a thin stripe of magnetic material. The stripe's resistance changes in the presence of a magnetic field, producing a strong signal with low noise amplification and permitting significant increases in areal densities. As the disk passes by the read element, the disk drive circuitry senses and decodes changes in electrical resistance caused by the reversing magnetic polarities. The AMR read element's greater sensitivity provides a higher signal output per unit of recording track width on the disk surface. Not only does magnetoresistive technology permit more data to be placed on disks, but it also uses fewer components than other head technologies to achieve a given capacity point. The AMR read element is smaller than the TFI write element. In fact, the AMR read element can be made smaller than the data track so that if the head were slightly off-track or misaligned, it would still remain over the track and able to read the written data on the track. Its small element size also precludes the AMR read element from picking up interference from outside the data track, which accounts for the AMR head's desirable high signal-to-noise ratio. The AMR head had a relative 'magnetoresistance' (hereafter referred to as  $\Delta R/R = (R_{max} - R_{min})/R_{min}$ ) of the order of only 1%, but this was enough to increase the growth rate of HDD storage areal density from 25% per year, its value since nearly the introduction of HDD in 1957, up to 60% per year.

AMR heads offer a higher signal-to-noise ratio than TFI heads, resulting in superior error rates in drives using them. However, the most important advantage of AMR heads is that they can read from areal densities about four times denser than TFI heads at higher flying heights. The result is markedly improved hard drive performance.

#### 2.1.1 AMR Head Challenges

Manufacturing AMR heads can present difficulties. AMR thin film elements are extremely sensitive to electrostatic discharge, which means special care and precautions must be taken when handling these heads. The AMR thin film stripe is also sensitive to contamination and, because of the materials used in its design, subject to corrosion.

AMR heads also introduced a new challenge not present with TFI heads: thermal asperities—i.e., the instantaneous temperature rise that causes the data signal to spike and momentarily disrupt the recovery of data from the drive. Thermal asperities are transient electrical events, usually associated with a particle, and normally do not result in mechanical damage to the head. Although they can lead to misreading data in a large portion of a sector, new design features can detect these events. A thermal asperity detector determines when the read input signal exceeds a predetermined threshold, discounts that data value and signals the controller to re-read the sector.

#### 2.2 GMR Technology

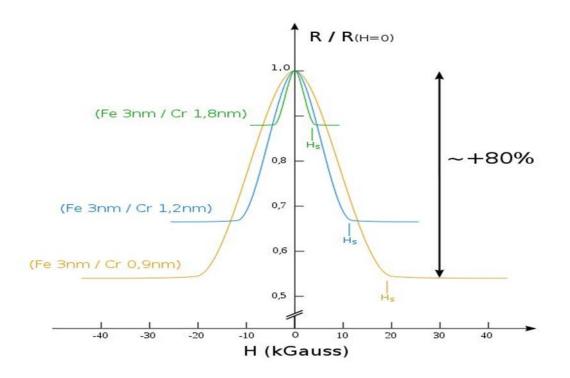

The founding step of spin electronics has been triggered by the discovery of the giant magnetoresistance (GMR) was actually to build magnetic multilayers with individual thicknesses comparable to the mean free paths, so that evidence could be seen for spin-dependent electron transport. In 1988, a group led by Peter Grünberg and Albert Fert independently reported magneto resistive effects in anti-Ferro magnetically coupled multilayers of Fe/Cr up to 50% at low temperature in "giant" multilayer structures. This effect was named the Giant Magneto resistance (GMR).

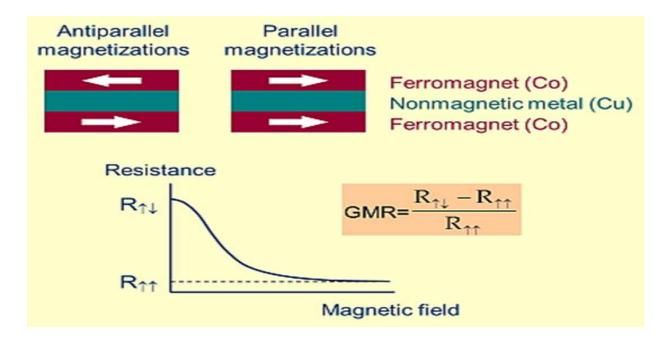

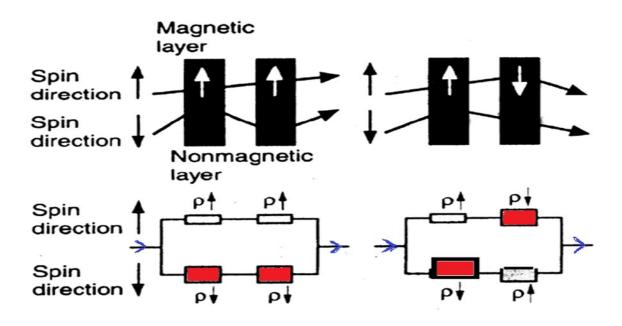

**Fig 2.2:** Schematic of Giant Magnetoresistance (GMR), showing parallel and anti-parallel effect of magnetization in Ferromagnets.

GMR is composed of two ferromagnetic material separated by a nonmagnetic metal layer. Parallel magnetization in the ferromagnets allow very low resistance while anti-parallel magnetization in the ferromagnets give very high resistance, which provide a great magnetoresistance (MR) value even at room temperature, as the magnetoresistance can be found by the following equation,

$MR = (R_{anti-parallel} - R_{parallel})/R_{parallel}$

**Fig 2.3:** The founding results of Albert Fert and Peter Grünberg (1988): change in the resistance of Fe/Cr super lattices at 4.2 K in external magnetic field H. The current and magnetic field were parallel to the axis. The arrow to the right shows maximum resistance change. Hs is saturation field [29].

GMR technology has brought a major technological advance over AMR technology. GMR are the most sensitive sensors yet developed for reading computer data on hard drives. Based on the "giant magnetoresistive effect," a discovery in magnetism made almost 15 years ago in Europe, IBM's further research transformed the effect into a practical reality. IBM's commercial production of

GMR heads is well underway. In 1998 Western Digital entered into an agreement with IBM to purchase advanced GMR heads for its EIDE desktop hard drives. Read-Rite Corp., TDK/SAE Corp. and others continue to supply Western Digital with AMR and GMR heads for its enterprise class as well as some of the EIDE desktop hard drives.

Like AMR heads, GMR heads incorporate separate MR read and TFI write elements. However, the GMR read elements are formed from more complex structures with a higher sensitivity to the changing magnetization on the disk. While in AMR sensors, a single film changes resistance in response to a change in magnetic field on the disk, in GMR sensors, two films, separated by a very thin electrically conductive layer, perform this function. The result is that GMR heads achieve even higher areal densities and performance levels than AMR heads.

AMR heads can read areal densities over 3 gigabits per square inch, on the other hand the newer GMR heads can be scaled to very small dimensions to read areal densities in excess of 10 gigabits per square inch while still maintaining good signal amplitude. Looked at another way, GMR heads can read data on hard drives that can pack over three times more data into the same space.

## 2.2.1 How GMR Sensors Work

GMR sensors work by exploiting the quantum nature of electrons. Electrons have two spin directions: up and down. Electrons with spin direction parallel to a film's magnetic orientation move freely, thereby producing low electrical resistance. When electrons move in the opposite spin direction, they are hampered by more frequent collisions with atoms in the film, thereby producing higher resistance.

Fig 2.4: Representation of the flow of spin up and down electron through the multilayer structure of GMR.

When the magnetization in both the layers are parallel, then one spin polarization experiences  $\rho\uparrow$  through both layers, the other spin polarization  $\rho\downarrow$  in both layers. Let us consider,

$\rho \uparrow = \rho(1-B)$  and  $\rho \downarrow = \rho(1+B)$ , where  $\rho$  is the resistivity and *B* is a constant of coefficient. Then the effective resistivity is,

$$\rho\uparrow\uparrow=\rho\downarrow\downarrow=(2\rho\uparrow\rho\downarrow)/(\rho\uparrow+\rho\downarrow)=\rho(1-B^2)$$

In anti-parallel magnetization in the ferromagnetic layers, each spin channel experiences  $\rho\uparrow$  and  $\rho\downarrow$  in series. The effective resistivity is,

$$\rho \uparrow \downarrow = (\rho \uparrow + \rho \uparrow)/2 = \rho$$

So, parallel magnetization in the ferromagnets gives much lower resistivity than in the case of antiparallel magnetization.

$$\rho$$

(parallel)= $\rho$ (1- $B^2$ ) <  $\rho$ = $\rho$ (anti-parallel)

Changes in the magnetic field originating from the disk cause a rotation of the sensor film's magnetic orientation, which in turn, increases or decreases the resistance of the entire structure. Low resistance occurs when the sensor and pinned films are magnetically oriented in the same

direction, since electrons with parallel spin direction move freely in both films. Higher resistance occurs when the magnetic orientations of the sensor and pinned films oppose each other, since the movement of electrons of either spin direction is restrained by one or the other of these magnetic films.

Where the resistance changes in AMR heads are approximately 2 percent, in GMR heads, they are typically 7 to 8 percent. Because their percent change in resistance is as much as four times greater than in AMR sensors, GMR sensors can operate at significantly higher areal densities as they are more sensitive to magnetic fields from the disk.

GMR heads' greater sensitivity makes it possible to detect smaller recorded bits and read them at higher data rates. Larger signals from GMR heads also help to overcome electronic noise.

Beyond GMR, the next step in hard drive technology will be "Synthetic Spin Valve" GMR or Colossal MR (CMR). This development is underway utilizing materials and layers yet being proven in research labs.

## 2.3 Spin Valve

The GMR is an outstanding example of how structuring materials at the nanoscale can bring to light fundamental effects that provide new functionalities. And indeed the amplitude of the GMR immediately triggered intense research, soon achieving the definition of the spin-valve sensor [29-31].

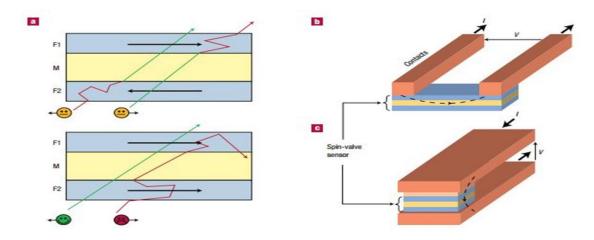

The spin valve is just a tri layer film in which one layer (for example, F2) has its magnetization pinned along one orientation. The rotation of the free F1 layer magnetization then 'opens' (in P configuration) or 'closes' (in AP configuration) the flow of electrons, acting as a sort of valve.

**Fig 2.5:** The spin valve. a. Schematic representation of the spin-valve effect in a tri layer film of two identical ferromagnetic layers F1 and F2 sandwiching a non-magnetic metal spacer layer m, the current circulating in plane. b. Schematic arrangement of the 'current in plane' spin-valve sensor in a read head. c. schematic arrangement of the 'current perpendicular to plane' spin-valve sensor in a read head. In both configurations, the recording medium travels parallel to the front face of the sensor.

When the two magnetic layers are magnetized parallel (lower scheme in Fig), the spin-up electrons (spin antiparallel to the magnetization) can travel through the sandwich nearly un-scattered, providing a conductivity shortcut and a low resistance. In contrast, in the antiparallel case (top scheme) both spin-up and spin-down electrons undergo collisions in either F1 or F2, giving rise to a higher overall resistance.

The introduction of the spin-valve sensor by IBM in 1997 to replace the AMR sensor in magnetoresistive HDD read heads, has increased the growth rate for storage areal density immediately up to 100% per year. Together, the sequential introduction of the magnetoresistance and spin-valve head, by providing a sensitive and scalable read technique, contributed to increase the raw HDD areal recording density by three orders of magnitude (from ~0.1 to ~100 Gbit in–2) between 1991 and 2003. This jump forward opened the way both to smaller HDD form factors (down to 0.85-inch disk diameter) for mobile appliances such as ultra-light laptops or portable multimedia players, and to unprecedented drive capacities (up to a remarkable 1 terabyte) for video recording or backup. HDDs are now replacing tape in at least the first tiers of data archival strategies, for which they provide faster random access and higher data rates.

However, the areal density growth rate started to slow down after 2003, when other problems joined the now limiting spin-valve head.

#### 2.4 Magnetic Tunnel Junction (MTJ)

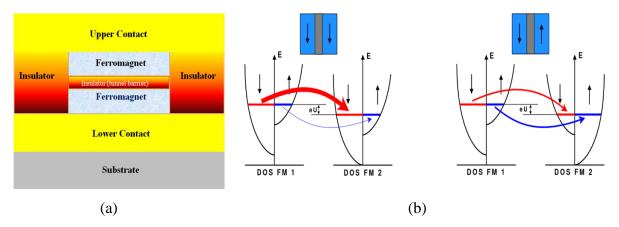

A big revolutionary change came from replacing the non-magnetic metallic spacer layer M of the spin valve by a thin (~1–2 nm) non-magnetic insulating layer, thus creating a magnetic tunnel junction (MTJ). In that configuration the electrons travel from one ferromagnetic layer to the other by a tunnel effect, which conserves the spin. Again, this is not a new story, as it was proposed by Jullière24 in 1975, but its practical realization with a high magnetoresistance (up to 30% at 4.2 K) had to wait until 1995 once considerable progress had been made in deposition and Nano patterning techniques [33,34]. The first MTJs used an amorphous of  $Al_2O_3$  insulating layer between ferromagnetic metal layers. The tunnel magnetoresistance (TMR) of such stacks reached a limit around 70% at room temperature. Much higher effects were later obtained with a single-crystal MgO barrier [35,36].

**Fig 2.6:** a. Schematic of a Magnetic tunnel junction. b. Schematic representation of the tunnel magneto resistance in the case of two identical ferromagnetic metal layers separated by a non-magnetic amorphous insulating barrier such as  $Al_2O_3$ , the tunneling process conserves the spin. When electron states on each side of the barrier are spin-polarized, then electrons will more easily find free states to tunnel to when the magnetizations are parallel than when they are anti-parallel.

The magnetic tunnel junction is clearly a CPP (Current perpendicular to the plane) 'vertical' device, with a magnetic behavior similar to a spin valve but magnetoresistance values up to two orders of magnitude higher. It is stable up to reasonable breakdown voltages (above 1 V), and the equipment suppliers rapidly developed reliable techniques to scale down its dimensions to well below 100 nm. So its development had an immediate impact on storage applications.

MTJs have an intrinsic high resistance (with resistance–area products above 1  $\Omega$  cm<sup>2</sup>), and with further downscaling it will become difficult to maintain a high signal-to-noise ratio with an increasing sensor resistance. Then CPP spin valves or degenerate MTJs could become more favourable.

## 2.5 Magnetoresistive Random-Access Memory (MRAM)

Magnetoresistive random-access memory (MRAM) technology combines a magnetic tunnel junction (MTJ) device with standard silicon-based microelectronics to obtain a combination of qualities not found in any other memory technology. MRAM is a high-speed, nonvolatile memory with unlimited read and write endurance. Because the data is stored in the magnetic state of the bit and is read out by sensing the resistance of the bit, MRAM is fundamentally different from commonly available commercial memories, such as dynamic RAM and flash memory, those are based on stored charge. Table 2.1 shows a qualitative comparison of MRAM and four other commercial memories.

| Table 2.1: Comparison of Memory Technologies. |           |           |         |           |                   |  |  |  |

|-----------------------------------------------|-----------|-----------|---------|-----------|-------------------|--|--|--|

| Property                                      | SRAM      | DRAM      | Flash   | FeRAM     | MRAM              |  |  |  |

| Read                                          | Fast      | Moderate  | Fast    | Moderate  | Moderate-<br>Fast |  |  |  |

| Write                                         | Fast      | Moderate  | Slow    | Moderate  | Moderate-<br>Fast |  |  |  |

| Nonvolatile                                   | No        | No        | Yes     | Partially | Yes               |  |  |  |

| Endurance                                     | Unlimited | Unlimited | Limited | Limited   | Unlimited         |  |  |  |

| Refresh                                       | No        | Yes       | No      | No        | No                |  |  |  |

| Cell Size                                     | Large     | Small     | Small   | Medium    | Small             |  |  |  |

| Low voltage                                   | Yes       | Limited   | No      | Limited   | Yes               |  |  |  |

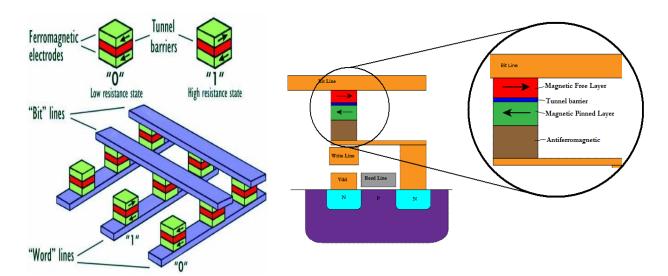

Since only MRAM combines non-volatility, read/write endurance, speed, and density, it has the potential to displace other memory technologies, particularly in applications that would otherwise require multiple memory types. An analysis of expected density and reduced system complexity shows that MRAM will also be cost-competitive, overall system costs are reduced by eliminating the need for integrating multiple types of memory. MTJ-based MRAM makes use of quantum mechanical tunneling of spin-polarized electrons through a very thin (15 Å) di-electric. The relative orientation of the magnetization in the two ferromagnetic layers determines the resistance of the MTJ structure. MRAM devices are designed to have two stable magnetic states that correspond to high- and low-resistance states. Low resistance occurs when the two layers have the same magnetization orientation; high resistance occurs when the orientations are opposed to each other.

**Fig 2.7:** Magnetoresistive random-access memory (MRAM) technology combining a magnetic tunnel junction (MTJ) device with standard silicon-based microelectronics.

Unlike most other semiconductor memory technologies, the data is stored as a magnetic state rather than a charge, and sensed by measuring the resistance without disturbing the magnetic state. Using a magnetic state for storage has two main benefits.

First, the magnetic polarization does not leak away over time like charge does, so the information is stored even when the power is turned off. Second, switching the magnetic polarization between the two states does not involve actual movement of electrons or atoms, and thus no known wearout mechanism exists.

## 2.5.1 MRAM: Reading and Writing process

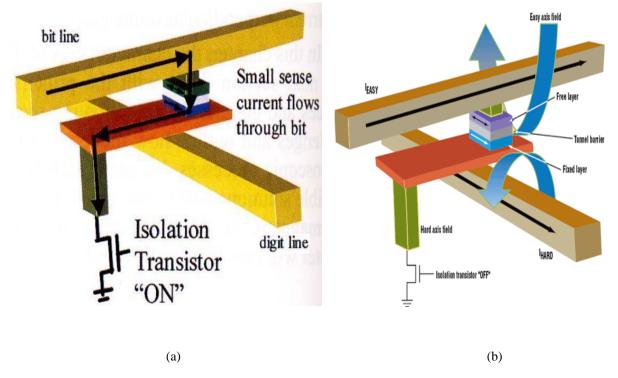

From the cross point architecture we can see that MRAM has two bit lines and in between them there is MTJs which are coupled with silicon based microelectronics. To sense, or read, the bit, the isolation transistor is turned on and a current ( $I_{sense}$ ) is passed through the magnetic

**Fig 2.8:** Cross point architecture of a MRAM showing Read and Write process in MARAM showing reading (a) and writing process (b).

tunnel junction (MTJ). Measuring the electrical resistance of a small sense current from a supply line through the cell to the ground and comparing it with the reference value give the required read states. If the measured resistance is found to be higher than the reference value, then the read logic level will be high (1) and on the other hand if the resistance measured is found to be lower than the reference value then the read logic level will be low (0).

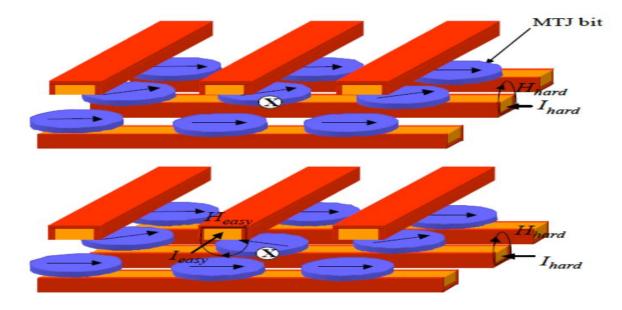

Writing, or programming, the bit involves applying currents (I) to each of the write lines so that field is generated at the bit from both lines simultaneously. When current is passed through the write lines, an induced magnetic field is created at the junction, which alters the polarity of the free layer. In order to change the polarity of the free layer, both fields are necessary. Only the bit in which current is applied in both hard and easy axis will be written. The other bits will remain half-select.

For conventional MRAM bits, a write operation consists of sending pulses of current down each of the two programming lines (write lines 1 and 2), so that they simultaneously apply both easy and hard axis magnetic fields to the bit. The system is engineered so that the field from a single pulse on either programming line is not sufficient to switch the bit, but the field generated by the combination of both programming lines is enough for switching to occur.

Fig 2.9: Writing process in a MRAM showing Easy and Hard axis.

### 2.5.2 Application of MTJ Based MRAM

MRAM devices are ideal replacement for battery-backed SRAM (BBSRAM). MRAM is a fast, non-volatile memory with unlimited endurance—a combination of characteristics not available in any other individual semiconductor memory product. MRAM is much faster—35 ns compared to BBSRAM at 70 ns read/write speed. It is a more reliable replacement of BBSRAM because it is a single-chip solution, compared to BBSRAM's complex multi-component system (including SRAM, battery and control chip). MRAM is directly swappable with BBSRAM since it has a standard JEDEC SRAM pin out and the ability to be written in a byte-wise configuration similar to BBSRAM.

Additionally, MRAM is priced competitively with BBSRAM. In addition to BBSRAM replacement, MRAM offers other significant performance advantages over existing memory technologies. For instance, nonvolatile memories, such as hard disk and flash, store instructions

and data from operating systems and individual programs, and transfer them to the processor when needed. This transfer can become a bottleneck and hinder processor performance. MRAM stores this same information, but with the capability to deliver it directly to the microprocessor without creating a bottleneck. These characteristics make MRAM a perfect nonvolatile memory for RAID servers, data streaming, system configuration and black-box applications.

MRAM is a revolutionary memory product that provides the highest density, the best price/performance and highest reliability of all non-volatile RAM product alternatives. MRAM technology is well positioned to supply high density, low-cost embedded memory capable of replacing Flash, SRAM and EEPROM with a single unified memory in many future microcontroller and system-on-chip products.

#### 2.5.3 Problems Associated with MRAM

The use of a magnetic field to write the information still remained a considerable limitation. This can easily be understood. Let us assume that information is stored in the form of the magnetization orientation of a nanoparticle of volume V. The energy barrier fighting the thermal excitations is given by KV, where K is the anisotropy constant per unit volume. Non-volatility — usually defined by a maximum error rate, for example 10–9, over a 10-year period — is obtained when  $KV > 50-60k_BT$ , where  $k_B$  is the Boltzmann constant and T is the temperature. So reducing V requires a corresponding increase in K, but then the writing field increases proportionally with K, whereas the power available to create it decreases as the dimensions are downscaled. So conventional MRAM has two main drawbacks: i) Poor scalability and ii) High write current. To solve these problems a new technology has evolved ad it is Spin-Torque Transfer Magnetic RAM (STT MRAM).

#### 2.6 Spin-Torque Transfer Magnetic RAM (STT MRAM)

Spin-torque transfer magnetic RAM (STT MRAM) is a promising candidate for future embedded applications. It combines the desirable attributes of current memory technologies such as SRAM, DRAM, and flash memories (fast access time, low cost, high density, and non-volatility). It also solves the critical drawbacks of conventional MRAM technology: poor scalability and high write current. The demand for on-chip embedded memories has grown significantly over the last few decades. On-chip memories can be accessed fast (contrary to large miss penalty associated with off-chip memories) and hence, increases the bandwidth of high performance processors. Several

memory technologies have been explored by researchers in the past. Static-RAM (SRAM) provides excellent read and write proper-ties but the cell size is relatively large (6-T structure) [T-transistor] and limits the amount of memory that can be integrated within the die. On-chip DRAMs have been explored as a possible alternative to SRAMs due to its small cell size (1-T or 3-T structures). However, leakage of information is severe in such memories and periodic refresh rates make them undesirable for portable electronics with limited battery life. In contrast to SRAMs and DRAMs, flash memories do not require external power to store data due to their nonvolatile nature. However, high-voltage and slow-write operations with limited read/write endurance overshadow the inherent advantages such as high integration density and simple architecture.

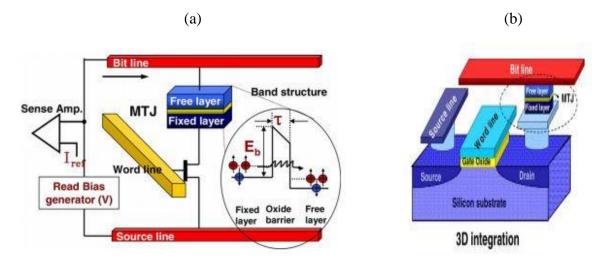

Spin-torque transfer magnetic random access memory (STT MRAM), derived from the cutting edge of research on Spintronics, is orthogonal to all previous memory technologies [37]. It combines all desirable memory attributes, e.g., nonvolatility, unlimited endurance, low power, high speed, and high memory density. Therefore, STT MRAM has gained lots of attention in today's memory community. Fig.{} shows the structure of a typical STT MRAM bit-cell. It consists of a transistor, a spintronic device (magnetic tunneling junction), word line (WL), bit line (BL) and source line (SL).

**Fig 2.10:** STT MRAM bit cell in 1-transistor-1-MTJ (1T1M) configuration includes: 1) Spintronic device: MTJ; 2) bit line; 3) source line; 4) word line; 5) nMOS; and 6) read driver. b. Cross section of an STT MRAM bit cell. MTJ is integrated with nMOS (dominating cell area) using 3-D technology

The basic building block of STT MRAM cell is the magnetic tunneling junction (MTJ). The MTJ is integrated with CMOS circuitry using 3-D technology [37]. When a sufficient current density passes through the MTJ, the spin polarized current will exert a spin transfer torque to switch the magnetization of free layer. This is the fundamental mechanism of STT MRAM. It allows STT-RAM to have a smaller cell size and write current than MRAM.

## 2.6.1 Operating Principle of STT MRAM

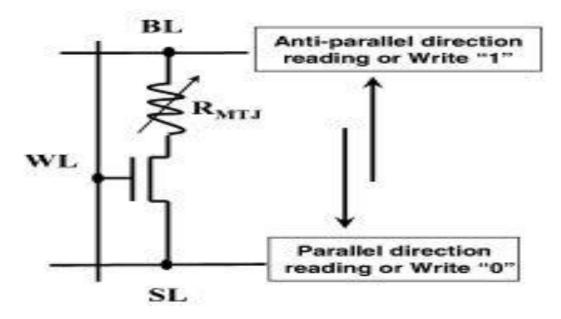

The equivalent circuit for an STT MRAM bit cell in read and write operations is shown in Fig (2.11).

Fig 2.11: Equivalent circuit diagram of an STT MRAM bit cell in read and write operation.

There are two ways of reading a cell, namely parallel direction reading and anti-parallel direction reading. In parallel direction reading, we apply a small bias to BL and SL is grounded. After activating WL, cur-rent flows from BL to SL. In anti-parallel direction reading, the voltage polarity applied to BL and SL is switched and current flows in the reverse direction (from SL to BL).

In contrast to read operation, writing data to a cell requires much higher current. Due to the hysteresis nature of MTJ bi-directional current flow is required. For example, when writing a "0" to a cell storing "1", BL is precharged to  $V_{DD}$  and SL is grounded. If the cell current is above the switching threshold current of MTJ, the magnetization direction of the free layer begins to rotate from anti-parallel (high resistance state) to parallel direction (low resistance state).

#### 2.6.2 STT-MRAM to Reduce Issues Associated with Conventional MRAM

Two major issues associated with conventional MRAM are: 1) high write current and 2) poor scalability [37], [38]. Conventional MRAM uses external current induced magnetic field to switch the magnetization direction of free layer from one direction to the other during write operation [28]. As MRAM scales, the magnetic field strength required for switching magnetization increases, resulting in dramatically increased write current and high power dissipation. In contrast to conventional MRAM, STT MRAM uses the direct injection of spin polarized current by spintronic device (MTJ) itself to switch the magnetization of the free layer and hence requires much less write current. More importantly, in STT MRAM, switching threshold current reduces with MTJ scaling, making it low power and highly scalable.

# **Chapter 3**

# Spin Transistor

## (Spin Based Semiconductor)

Dramatic progress in the present integrated electronics has been powered by the miniaturization of transistors and the high degree of device integration, since the size reduction and large-scale integration of transistors provide improvements in integrated circuit performance including reliability and production cost. Metal-oxide-semiconductor field-effect transistors (MOSFETs) and complementary MOS (CMOS) devices (hereafter, both are referred to as MOS devices) based on sophisticated Si technology are a fundamental building block for mainstream integrated circuits, and they play an essential role as Btechnology drivers [in the current electronics. This is, of course, due to the excellent scalability and integration ability of MOS devices. The rapid and continual progress in the scaled down technology of MOS devices (that is, the so-called scaling) is known as Moore's law [43]-[45]. However, the scaling of preproduction MOS devices has already reached a physical limit of several nanometers, indicating the end of scaling in the near future. In such extremely scaled-down devices, leakage currents induced by quantum mechanical phenomena, various parasitic elements, and variability in device characteristics give raise to serious performance degradation problems. In addition, the production cost including facility investment becomes huge. These mean that the effect of scaling weakens for nanometer-scale MOS devices. Therefore, scaling in dependent technologies for improving device/circuit performance has attracted considerable attention.

In highly interconnected integrated circuits, the high current drivability of the transistors is very important for the circuit performance, since the circuit speed is dominated by charging/discharging of the load capacitance.

Therefore, the operating speed and operating principle of the individual transistors hardly affect the circuit speed, as long as they exhibit high current drivability. In addition, the high current drivability is also indispensable for other performance indices of the integrated circuits, such as low (dynamic) power dissipation. From these viewpoints, a great deal of effort has been made to achieve much higher current drivability for MOS devices so far. Therefore, it has been explored that new channel structures, such as fin, nanowire, and other three-dimensional structures, and new channel materials with high carrier mobility, such as strained Si, Ge, III-V compound semiconductors, and grapheme, are introduced into MOS devices. An effect equivalent to scaling can be substantially achieved by introducing new channel structures/materials without scaling, which is sometimes called the Bmore Moore [approach or the Bextended CMOS] concept [46]. It should be noted that the operating principle of extended CMOS devices is the same as that of ordinary MOS devices, although the channel structure and material of extended CMOS devices are replacing conventional ones. Introduction of new functionality, such as quantum effects and spin-related phenomena, into integrated circuits is also expected to be an alternative approach instead of the scaling. By introducing new functionality, the transistor performance itself would not become superior to conventional MOS devices. However, there exists a possibility for improving the circuit performance by employing new circuit architectures based on newly added functionality. In order to achieve such new architectures, a new MOS device with the desired functionalities must be realized. One approach is a combination of a MOS device with a so-called functional device at the circuit level. In many cases, functional devices have no characteristics (in particular, high current drivability) suitable to integrated circuits, except for new functionalities. Therefore, they should be used in combination with MOS devices. For example, this approach was examined in quantum effect devices. A quantum effect transistor consisting of an ordinary fieldeffect transistor (FET) and a resonant tunnel device was demonstrated. Another approach is the device-level integration of a MOS device and a functional device with a hybrid structure. Several functional MOS devices that contain the structure of two-terminal functional devices in their device structure have been proposed so far, such as a Josephson junction [47], [48], a Esaki diode [49], a resonant tunnel device and a magnetic tunnel junction. The important features of functional MOS devices, except for newly added functionalities, could be high current drivability and exponentially steep on/off switching of MOS devices, which would be inaccessible to any other functional device. The paradigm shift from device scaling to the introduction of new functionalities to MOS devices could become an important route to future integrated electronics technology. Note that an electronic device based on new physical phenomena and/or new state variables is called a beyond-CMOS device, and new devices uniting a beyond-CMOS element with an ordinary MOS device are referred to as the Bnonconventional extended CMOS [46].

The aim of recently emerging spintronics (spin electronics) research is to manipulate spin degrees of freedom in solid state devices and provide new concepts for future electronics and photonics employing spin degrees of freedom. One of the most attractive research directions is to control charge and spin transport phenomena in active electronic devices, i.e., spin transistors. Spin transistors are a new type of concept device that unites an ordinary transistor with the useful functions of a spin (magneto resistive) device. The interesting features of spin transistors are nonvolatile information storage and reconfigurable output characteristics, which are very useful and suitable functionalities for future high performance integrated circuit architectures such as

nonvolatile logic (e.g., nonvolatile power-gating systems) and reconfigurable logic (e.g., nonvolatile field programmable gate arrays). Following the first proposal of the spin transistor concept by Datta and Das and Johnson, a wide variety of spin transistors based on various operating principles have been proposed so far.

In this article, we present the current status and outlook of spin transistors. After a brief review of the fundamental and key phenomena/technologies for spin transistors in Section II, the device structure, operating principle, and features of various spin transistors are described in Sections III, IV, and V, in which we focus on potential-effect spin transistors in the Section III and field effect spin transistors in Sections IV and V. Finally, integrated circuit applications of spin transistors, including nonvolatile logic and reconfigurable logic systems that are the most suitable applications of spin transistors, are presented in Section VI.

#### 3.1 Requirements for Spin Transistor [3]

Spin transistors, which generally have two ferromagnetic layers as a spin injector and a spin detector, can be active three-terminal devices. Ideally, spin transistors exhibit ordinary transistor actions with variable output characteristics which can be controlled by the relative magnetization configuration of the two ferromagnetic layers. In many cases, the trans-conductance, gm (the output-current drive capability for the input voltage) of spin transistors can be switched by the relative magnetization configuration. This feature is often referred to as magnetization configuration-dependent output characteristics. To express qualitatively magnetization configuration dependent output characteristics, the magneto-current ratio defined by

#### $\gamma MC = (IC_P - IC_{AP})/IC_{AP}$

where P and AP refer to the parallel and antiparallel magnetic state of the base spin valve, respectively. Furthermore, the magnetization configuration can be also used as nonvolatile binary data. Owing to these useful features, spin transistors are potentially applicable to integrated circuits for ultrahigh-density nonvolatile memory whose memory cell is made up of a single spin transistor and for nonvolatile reconfigurable logic based on multifunctional spin transistor gates. Although magnetization-configuration dependent output characteristics are needed to realize such "spin-electronic" integrated circuits, device performance as a "transistor" is still important. In order to be used in integrated circuits as active devices, spin transistors must satisfy the following requirements-

1) Large magnetocurrent ratio ( $\gamma$ MC) for nonvolatile memory and logic functions.

2) High transconductance (gm) for high-speed operation.

3) High amplification capability (voltage, current, and/or power gains) to restore propagating signals between transistors and to be applied for analog circuits.

4) Small power-delay product and small OFF-current for low-power dissipation.

5) Excellent scalability and simple device structure for high degree of integration and high process yield.

Thus, it is important to explore spin transistors that simultaneously satisfy all the requirements noted above [items 1)–5)].

#### 3.2 Fundamental of Spin Transistor

#### **3.2.1 Two-Terminal Magnetoresistive Devices**

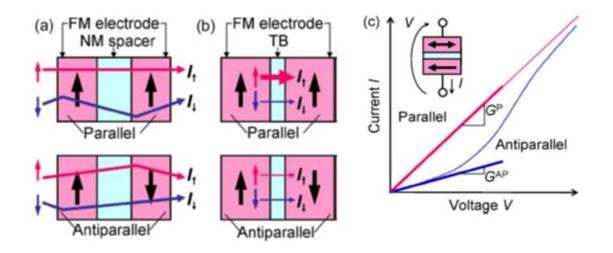

Two-terminal magneto resistive devices are a basic building block of spin transistors. After the discovery of the giant magneto resistance (GMR) effect in ferromagnetic/ nonmagnetic metal multilayers, magneto resistive devices have received considerable attention. Here, we briefly review two-terminal magneto resistive devices from the viewpoint of their application to spin transistors. Their magneto resistive memory (MRAM) applications were reviewed in. Fig. 3.1 schematically shows the structures and typical current–voltage ðI\_VP characteristics of two-terminal magneto resistive devices. Spin valve (SV) devices consist of at least two ferromagnetic metal (FM) layers separated by an ultrathin nonmagnetic metal (NM) spacer layer, as shown in Fig. 3.1(a). They are classified into current-in-plane (CIP) and current-perpendicular-to-plane (CPP) geometries, and CPP-SVs have been applied to spin transistors. Ferromagnetic transition metals and their related alloys, including full-Heusler alloys, have been applied to the ferromagnetic layers and nonmagnetic transition metals and other nonmagnetic metals have been used for the spacer layer. Magnetic tunnel junctions (MTJs) have a device structure

**Fig 3.1:** Schematic representations of (a) CPP-SV and (b) MTJ devices. (c) current–voltage characteristics of these devices. FM, NM, and TB represent ferromagnetic metal, nonmagnetic metal, and tunnel barrier, respectively.

similar to SVs, however the metallic spacer in the SVs is replaced by an insulating tunnel barrier (TB) layer, as shown in Fig. 3.1(b). The MTJ technology was initially developed by the invention of the  $AlO_x$  tunnel barrier, and its subsequent dramatic progress has been due to the development of MgO tunnel barriers.

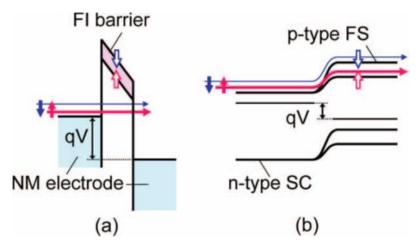

Furthermore, half-metallic ferromagnet electrodes using full-Heusler alloys have also had a great impact on the MTJ technology [50]. SVs and MTJs are designed to establish two relative magnetization configurations of parallel and antiparallel alignments. The electrical conductance of both the devices depends on the magnetization configuration. SVs and MTJs exhibit qualitatively the same features in spite of different mechanisms, i.e., a high conductance is achieved in parallel magnetization and it becomes low in antiparallel magnetization, as schematically shown by solid lines in Fig. 3.1(c). This phenomenon can be attributed to spin dependent scattering for SVs and to spin-dependent tunneling for MTJs, which is sometimes called the spin valve effect for SVs and the tunneling magnetoresistance (TMR) effect for MTJs. The magnetoresistance ratio is defined by \_MR 1/4 dog \_ GAPP=GAP that is a measure of magnetoresistive devices, where GP and GAP represent the electrical conductance in the parallel and antiparallel magnetization configurations, respectively. Note that the I\_V characteristics of the magnetoresistive devices well reflect the feature of their device structures, and the \_MR value often depends on a bias voltage. In the case of MTJs, it is known that the I V characteristics show a nonlinear behavior and MR decreases with increasing bias voltage, as schematically shown by the dashed curves in Fig. 1(c). The \_MR of MTJs is much higher than that of SVs. In contrast, the resistivity of SVs is much lower than that of MTJs, which is caused by a difference in the resistivity between the metallic spacer layer and the insulating tunnel barrier. The spin-filter effect that enables the selective propagation of carriers depending on their spin orientation is also useful for magnetoresistive devices. Fig. 3.2 shows the basic structure of two-terminal spin-filter devices. Ferromagnetic tunnel barriers [Fig. 3.2(a)], using a ferromagnetic insulator (FI), and ferromagnetic pn junctions [Fig. 3.2(b)], using a ferromagnetic semiconductor (FS), can act as spin filters based on the spin-dependent tunnel barrier and the spin-dependent built-in potential, respectively. By installing a ferromagnetic electrode as a spin injector or a spin detector to these spin-filter devices, magnetization configuration- dependent I\_V characteristics can be obtained, i.e., they act as a magnetoresistive device.

In order to establish the parallel and antiparallel magnetization configurations of magnetoresistive devices, exchange bias induced by anti-Ferro magnets is commonly used. When an anti-ferromagnetic/ferromagnetic layered structure is cooled with a magnetic field from a temperature above the Neel temperature of the anti-Ferro magnet layer (that is lower than the Curie temperature of the ferromagnetic layer), a magnetic anisotropy, the so called exchange bias, is induced in the structure. The resulting hysteresis loop of the anti-ferromagnetic/ferromagnetic system is shifted along the field axis (generally in the opposite direction to the applied field during the cooling) by the anisotropy, which is referred to as the spinning [of the Ferro magnet layer. When one of two ferromagnetic layers in a magnetoresistive device is sufficiently pinned (which is called the pinned layer), the parallel and antiparallel configurations can be easily formed by magnetization switching of the other ferromagnetic layer (which is called the free layer), since the magnetization of the pinned layer

**Fig. 3.2:** Schematic representations of the spin-filter effect in (a) ferromagnetic tunnel barrier and (b) ferromagnetic pn junction. FI, FS, and SC represent ferromagnetic insulator, ferromagnetic semiconductor, and semiconductor, respectively.

cannot be switched by the magnetic field for the magnetization reversal of the free layer. Note that a shape magnetic anisotropy of ferromagnetic films is often used in laboratory experiments for generating different cervicitis in ferromagnetic electrodes in magnetoresistive devices, which is also useful for achieving the formation of the parallel and antiparallel configurations.

Attractive functionalities of two-terminal magnetoresistive devices for integrated circuit applications are nonvolatile information storage based on the magnetization configuration and reconfigurable output characteristics depending on it. Therefore, these devices are promising not only for nonvolatile memory but also for new logic circuits using the nonvolatile and reconfigurable features. However, the two-terminal magnetoresistive devices would not be suitable for logic circuits when they used as logic elements, since they are a passive device. Of course, logic circuits can be configured by using two terminal passive devices. Nevertheless, these devices have no following functions that are strongly required for logic circuits: high current drivability for high-speed and low power operations and for sufficient fan-out, amplification capability for the restoration of attenuating signal, sufficient cutoff behavior for low standby power, and sufficient isolation behavior between input and output. (Note that the isolation behavior is required for logic devices, since the unidirectional propagation of a logic signal from input and output is crucial for logic circuits.) Therefore, three terminal transistor-type magnetoresistive devices, that is, spin transistors, are attractive. Spin transistors are a new concept device that unites an ordinary transistor with the useful functions of a two-terminal magnetoresistive device, which is realized by the device-level integration of these devices with a hybrid structure. Several ordinary potential effect transistors (PETs) and FETs are applied to spin transistors as their basic device structure, as described in this paper. It is worth noting that ordinary transistors (such as MOSFETs) used in present integrated electronics completely satisfy the above-described requirements.

Another way to use two-terminal passive magnetoresistive devices in logic circuits is in a circuitlevel combination of magnetoresistive devices with CMOS circuits. Although this method is not necessarily ideal, there is the advantage that the present MRAM technology can be applied to spin transistors, as also discussed in this paper.

#### 3.2.2 Spin Injection and the Conductivity Mismatch Problem

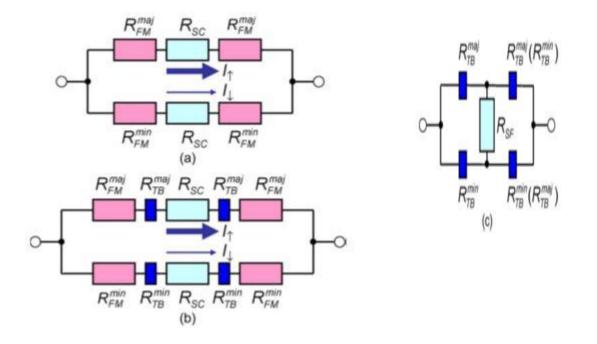

In the case of spin injection from an ordinary Ferro magnet (i.e., a ferromagnetic metal) to a semiconductor through the ohmic junction, a high efficiency spin injection can hardly be achieved, which is known as the conductivity (or impedance) mismatch problem [51]. This originates from the fact of the large difference in electrical conductivity between a ferromagnetic metal and a semiconductor, as shown below. Although the resistance of the spacer layer is not taken into account in CPP-SV devices as shown in Fig. 3.1(a), it becomes problematic when the spacer layer

belongs to a semiconductor. In general, the conductivity mismatch problem is treated by using electrochemical potential for spin-up and spin-down electrons. Here, we introduce a simple resistance network model for qualitative understanding. In the resistance network model, a ferromagnet can be expressed by a parallel circuit of two different resistances that represent the majority and minority spin channels of the ferromagnet. This circuit model can show the current spin-polarization of the ferromagnet. In a similar fashion, a semiconductor is expressible by a parallel circuit of two resistances of the same magnitude for spin-up and spin-down electrons. Fig. 3.3(a) shows the resistance network model of a ferromagnet (FM1)/semiconductor (SC)/ferromagnet (FM2) junction in the parallel magnetization configuration, where it is assumed that the FM1/SC and SC/FM2 junctions are ohmic, and that spin flip in the SC region can be eliminated. Rmaj FM and Rmin FM ð> Rmaj FMÞ represent the resistances for the majority and minority spin channels in FM1 and FM2, respectively, and RSC represent the resistance for the spin-up and spin-down channels in SC (both are equal). Here, the majority spin of FM1 is assumed to be the spin-up. The conductivity mismatch problem can be understood by treating the currents of the spin-up and spin-down channels in the parallel magnetization configuration. When the resistance of SC is comparable with that of FM1 and FM2, the combined resistances for the spinup and spin-down channels are different. The resulting current for the spin-up channel is higher than that for the spin-down channel. Therefore, the total current that flows in this structure is spinpolarized.

When RSC is much higher than Rmaj FM and Rmin FM, which is an actual case, the situation is quite different. In this case, Rmaj FM and Rmin FM can be neglected, and the voltage drop is caused entirely in the SC region. Therefore, the spin dependent resistances (Rmaj FM and Rmin FM) of FM1 and FM2 have no effect on the currents in the spin-up and spin down channels, i.e., the currents are determined by spin independent RSC, and thus the total current cannot be spin-polarized. This phenomenon is referred to as the conductivity mismatch problem.

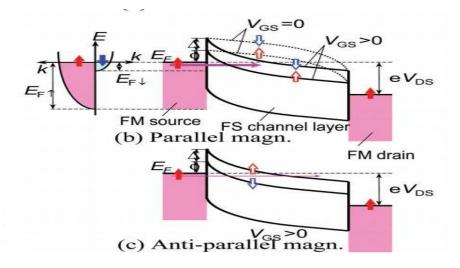

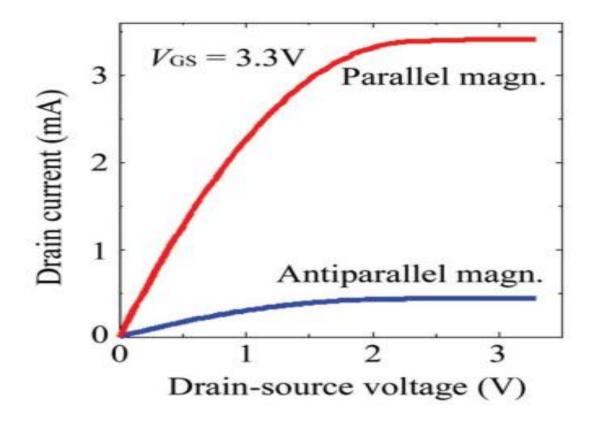

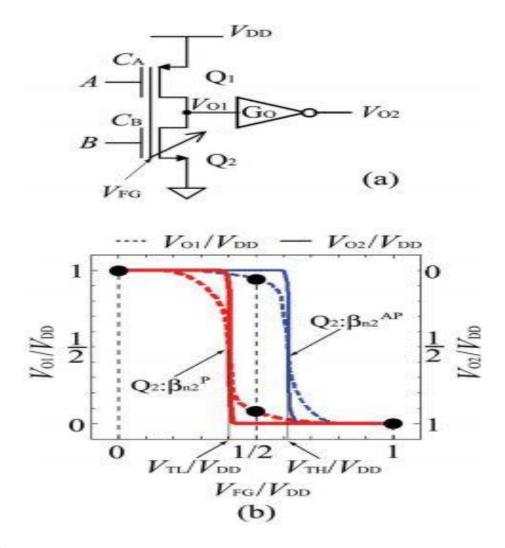

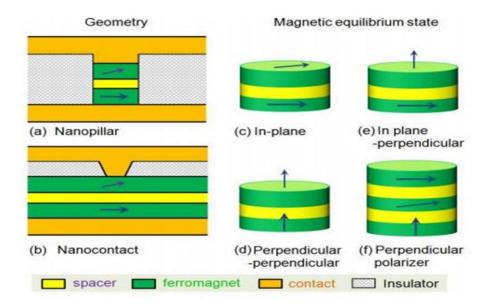

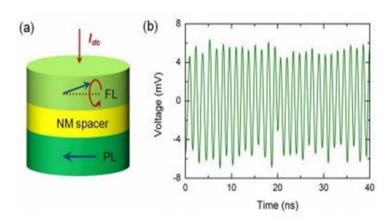

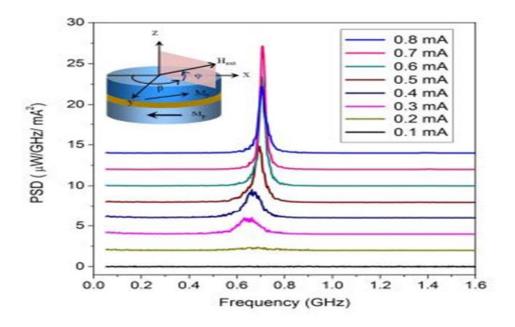

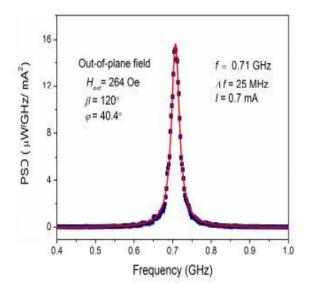

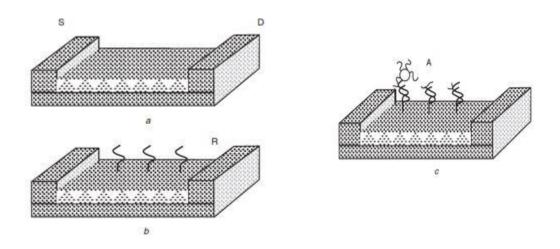

**Fig. 3.3:** Resistor network model for an FM/SC/FM junction. (a) Equivalent circuit for parallel magnetization. (b) Equivalent circuit with interface resistance for parallel magnetization. (c) Equivalent circuit for parallel magnetization in the case of high interface resistance. The parentheses represent the equivalent circuit for antiparallel magnetization.