حالله التحلن التجييم

Islamic University of Technology (IUT) Organization of Islamic Cooperation (OIC) Gazipur-1704, Dhaka, Bangladesh

## *" A COMPARATIVE STUDY OF LINEAR AND NON-LINEAR CONTROLLER DESIGN AND IMPLEMENTATION FOR DC-DC BUCK CONVERTER"*

**Prepared By:**

MAHBOOB ALI KHAN (student id:092475)

SALMAN KHAN (student id:092485)

MOHANAD A. A.MUAILEQ (student id:082489)

Supervised By:

**Prof. Dr. KAZI KHAIRUL ISLAM** Department Of Electrical And Electronic Engineering (EEE)

Department Of Electrical And Electronic Engineering (EEE) Islamic University of Technology (IUT) Organization of Islamic Cooperation (OIC)

OCTOBER 2013

### " A COMPARATIVE STUDY OF LINEAR AND NON-LINEAR CONTROLLER DESIGN AND IMPLEMENTATION FOR DC-DC BUCK CONVERTER"

#### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIRMENTS FOR THE AWARD OF DEGREE IN BACHELORS OF SCIENCE

in

**Electrical & Electronic Engineering** *by*

#### MAHBOOB ALI KHAN SALMAN KHAN MOHANAD A. A.MUAILEQ

Under the kind supervision of Prof. Dr. KAZI KHAIRUL ISLAM

Department Of Electrical And Electronic Engineering (EEE) Islamic University of Technology (IUT) Organization of Islamic Cooperation (OIC)

OCTOBER 2013

1

Certified that the project dissertation entitled

#### "A COMPARATIVE STUDY OF LINEAR AND NON-LINEAR CONTROLLER DESIGN AND IMPLEMENTATION FOR DC-DC BUCK CONVERTER"

Is submitted to the Department of Electrical and Electronic Engineering

Islamic University of Technology Dhaka(Bangladesh)

In the partial fulfillment of the requirements

For the award of Degree in

#### **BACHELORS OF SCIENCE IN**

#### ELECTRICAL & ELECTROINC ENGINEERING

In our opinion, the thesis is of standard required for the award of Bachelor Degree in Electrical & Electronic Engineering.

Supervised by:

2

Approved by:

**Prof. Dr. KAZI KHAIRUL ISLAM** Project Supervisor **Prof. Dr. MOHAMMAD SHAHHIDULLAH** Head of EEE department

#### OCTOBER 2013

Department of Electrical And Electronic Engineering, IUT, OIC.

## ACKNOWLEDGMENTS

All praise and thanks to Almighty Allah who has showered us with His invaluable blessings throughout our lives, giving us strength and spirit to complete this project.

We would like to express our heartiest gratitude towards our project supervisor **Dr. KAZI KHAIRUL ISLAM** Professor of Electrical & Electronic Engineering Department, for their valuable and enthusiastic guidance, help and continuous encouragement during the completion of this project. Without his stimulus for work and knowledge of the project idea, the completion of the project would have been impossible.

We are also grateful to **Dr. MOHAMMAD SHAHIDULLAH, Head**, Department of Electrical & Electronic Engineering, for his kind support.

We would like to give a special thanks to all our friends for all the thoughtful and mind stimulating discussions, sharing of knowledge which prompted us to think beyond. The help and co-operation received from the staff of Department of

Electrical & Electronics Engineering is thankfully acknowledged.

In the end we would like to show our deepest respect & thank to our parents & family, for their prayers, understanding and moral support to finish with success.

3

## CANDIDATE'S DECLARATION

The matter embodied in the thesis is original and has not been submitted elsewhere for the award of any degree or diploma.

Signature of the Candidate

Signature of the Candidate

MAHBOOB ALI KHAN

(student id:092475)

SALMAN KHAN

(student id:092485)

Signature of the Candidate

MOHANAD A. A.MUAILEQ

(student id:082489)

## **DEDICATED TO MY BELOVED PARENTS**

# *"for their long lasting love, kind support and being a wind beneath my wings".*

## ABSTRACT

Control applications of switched mode power supplies have been widely investigated. The main objective of research and development (R&D) in this field is always to find the most suitable control method to be implemented in various DC/DC converter topologies. In other words, the goal is to select a control method capable of improving the efficiency of the converter, reducing the effect of disturbances (line and load variation), lessening the effect of EMI (electro-magnetic interference), and being less effected by component variation.

With the speed improvement and cost reduction of digital control, digital controller is becoming a trend for DC-DC converters in addition to existed digital monitoring and management technology. In this thesis, digital control is investigated for DC-DC converters applications.

To deeply understand the whole control systems, DC-DC converter models are investigated based on averaged state-space modeling. Considering Buck DC-DC converter, the thesis takes it as an example for digital control modeling and implementation.

In Chapter 3, unified steady-state DC models and small-signal models are developed for DC-DC buck converters. Based on the models, digital and analog controllers design is implemented. In Chapter 4, digital modeling platforms are established based on Matlab /Simulink, Digital and analog PID design and corresponding simulation results are provided. Also some critical issues and practical requirements are discussed.

Chapter 5, describes in detail SMC (Sliding Mode Controller) and a briefly reviews the history of SMC. In the next section, a review of the theory of SMC is given, more particularly; the existence condition, the reaching condition, the system description in sliding mode, the chattering. The researches on and applications of SMC in electrical systems are shown. The SMC is implemented to the DC/DC Buck converter. The results are verified with the simulation results. Finally, the researches on and applications of the SMC for DC/DC converters are given in details.

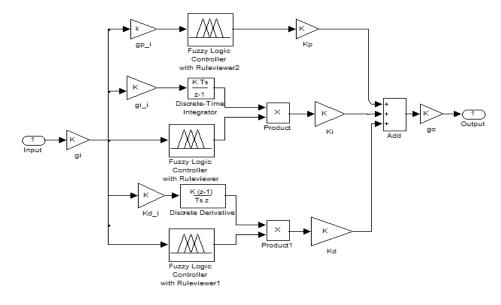

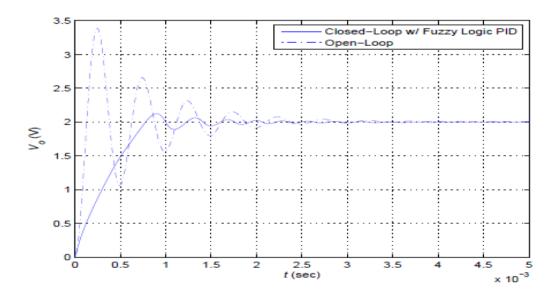

In Chapter 6, fuzzy logic control is introduced based on that knowledge an intelligent self- tuning fuzzy PID controller is proposed for the control of buck converter. The fuzzy logic control is used to tune the proportional, integral and derivative gain of the conventional PID controller. The compensated power converter is tested using the Simulink model in the presence of the disturbances, and it is shown that the self-tuning fuzzy controller is capable of keeping the power converter output voltage within the operating requirements, while improving system speed and stability.

In Chapter 7, a DSP-based digital controller is implemented with the TI's DSP chip TMS320F2812. Related implementation methods and technologies are discussed.

## CONTENTS

| ACKNOWLEDGEMENT           |  |

|---------------------------|--|

| ABSTRACT                  |  |

| LIST OF FIGURES           |  |

| LIST OF TABLES            |  |

| CHAPTER ONE: INTRODUCTION |  |

| 1.1 OVERVIEW              |  |

| 1.2 OBJECTIVE             |  |

| 1.3 PROBLEM STATMENT      |  |

| 1.4 THESIS ORGANIZATION   |  |

| CHAPTER TWO: DC TO DC POWER SUPPLY 21    |

|------------------------------------------|

| 2.1 INTRODUCTION                         |

| 2.2 LINEAR POWER SUPPLY                  |

| 2.3 SWITCH MODE POWER SUPPLY             |

| 2.4 TYPES OF CONVERTER                   |

| 2.4.1 NON-ISOLATED DC-DC CONVERTERS      |

| 2.4.2 ISOLATED DC-DC CONVERTER           |

| 2.4.3 MULTIPLE SWITCHED CONVERTER        |

| 2.5 FEEDBACK CONTROL FOR DC-DC CONVERTER |

| 2.5.1 DSP ADVANTAGES                     |

| 2.5.2 FPGA ADVANTAGES             |    |

|-----------------------------------|----|

| 2.5.3 CUSTOM IC DESIGN ADVANTAGES |    |

| 2.6 WHY WORK ON BLICK CONVERTER?  | 32 |

####

| 3 BUCK CONVERTER                                              | . 34 |

|---------------------------------------------------------------|------|

| 3.1 STATES OF OPERATION                                       | . 34 |

| 3.1.1 ON STATE                                                | . 34 |

| 3.1.2 OFF STATE                                               | . 35 |

| 3.2 CONTINUOUS AND DIS-CONTINUOUS CURRENT MODE                | . 35 |

| 3.3 DUTY RATIO CALCULATION                                    | . 36 |

| 3.4 INDUCTOR CALCULATION                                      | . 37 |

| 3.5 CAPACITOR CALCULATION                                     | . 40 |

| 3.6 LINEARIZATION USING STATE SPACE AVERAGING                 | . 42 |

| 3.6.1 POWER STAGE AND OUTPUT FILTER                           | . 42 |

| 3.6.2 BUCK CONVERTER                                          | . 44 |

| 3.7 DESIGN PARAMETERS                                         | . 47 |

| 3.8 TIME DOMAIN ANALYSIS OF OPEN LOOP DC-DC BUCK CONVERTER    | . 48 |

| 3.8.1 OUTPUT RESPONSEOF THE CONVERTER TO 12V DC POWER SOURCE  | . 48 |

| 3.8.2 OUTPUT RESPONSE TO 1AMP STEP CHANGE IN LOAD CURRENT     | . 49 |

| 3.8.3 OUTPUT RESPONSE TO 1V STEP CHANGE IN INPUT POWER SOURCE | 49   |

# CHAPTER FOUR: DESIGN OF ANALOG AND DIGITAL PID CONTROLLERS FOR<br/>DC-DC BUCK CONVERTER4 INTRODUCTION524.1 DESIGN OF ANALOG PID CONTROLLER52

| 4.1.1 DESIGN VIA ROOT LOCUS METHOD | 52 |

|------------------------------------|----|

|                                    |    |

| 4.1.1.1 DESIGN PROCEDURE OF AN ANALOG PID CONTROLLER VIA ROOT LOCUS               | 53 |

|-----------------------------------------------------------------------------------|----|

| 4.1.1.2 DESIGN OF PID CONTROLLER FOR DC-DC BUCK CONVERTER                         | 54 |

| 4.1.2 DESIGN VIA FREQUENCY RESPONSE METHOD                                        | 54 |

| 4.1.2.1 DESIGN PROCEDURE OF AN ANALOG PID CONTROLLER VIA FREQUENCY RESP<br>METHOD |    |

| 4.1.2.2 DESIGN OF PID CONTROLLER FOR DC-DC BUCK CONVERTER                         | 53 |

| 4.2 DIGITAL PID CONTROLLER                                                        | 57 |

| 4.2.1 DIRECT CONVERSION FROM ANALOG TO DIGITAL PID CONTROLLER                     | 57 |

| 4.2.2 DIGITAL PID DESIGN VIA DIRECT ROOT LOCUS METHOD                             | 58 |

| 4.2.3 DIGITAL PID DESIGN VIA DIRECT FREQUENCY METHOD                              | 58 |

## CHAPTER FIVE: DESIGN OF SLIDING MODE CONTROLLER FOR DC-DC BUCK

| 5.1 INTRODUCTION                                     |    |

|------------------------------------------------------|----|

| 5.1.1 BASICS OF SLIDING MODE CONTROL                 | 61 |

| 5.1.2 REVIEW ON SLIDING MODE CONTROL THEORY          | 62 |

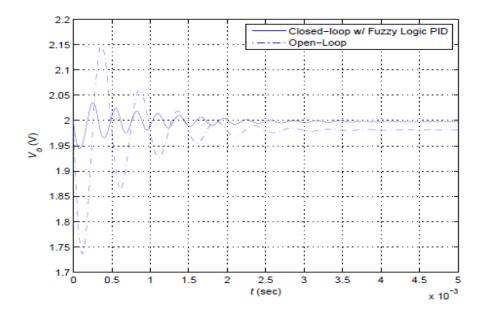

| 5.2 SLIDING MODE CONTROL FOR DC-DC BUCK CONVERTER    | 65 |

| 5.2.1 SYSTEM MODELING                                | 66 |

| 5.2.2 DESIGN OF SLIDING MODE CONTROLLER              | 69 |

| 5.2.3 DERIVATION OF SLIDING MODE EXISTENCE CONDITION | 70 |

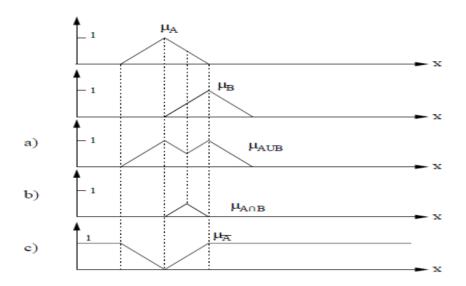

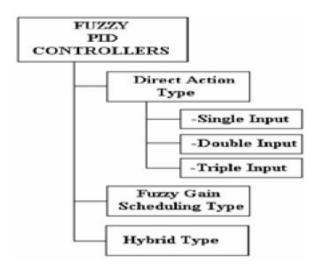

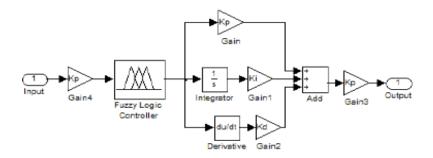

# CHAPTER SIX: DESIGN OF FUZZY LOGIC CONTROLLER & FUZZY BASED PIDFOR DC-DC CONVERTER746. INTRODUCTION756.1 FUZZY LOGIC OVERVIEW756.1.1 FUZZY NAMING CONVENTION766.1.2 MEMBERSHIP FUNCTIONS766.1.3 FUZZY OPERATIONS76

9 Department of Electrical And Electronic Engineering, IUT, OIC.

| 6.1.4 FUZZY RULE / FUZZY RULE BASE        | 77 |

|-------------------------------------------|----|

| 6.1.5 INFERENCE PROCEDURE                 | 79 |

| 6.1.6 DEFUZZIFICATION                     | 80 |

| 6.2 OVERVIEW OF FUZZY PID CONTROLLER      | 81 |

| 6.2.1 SINGLE INPUT FUZZY PID CONTROLLER   | 81 |

| 6.3 SELF TUNING FUZZY PID CONTROLLER      | 82 |

| 6.4 CONTROLLER DEVELOPMENT                | 83 |

| 6.4.1 INPUT SCALING                       | 83 |

| 6.4.2 CONTROL GAIN COEFFICIENT            | 83 |

| 6.4.3 FUZZY BASED PROPORTIONAL CONTROLLER | 83 |

| 6.4.4 FUZZY BASED INTEGRAL CONTROLLER     | 85 |

| 6.4.5 FUZZY BASED DERIVATIVE CONTROLLER   | 86 |

| 6.4.6 OUTPUT SCALING                      | 87 |

#### **CHAPTER SEVEN: IMPLEMENTATION OF DSP FOR DIGITAL CONTROLLERS**

|                                                | 88 |

|------------------------------------------------|----|

| 7. INTRODUCTION                                | 89 |

| 7.1 OVERVIEW OF DSPs                           | 89 |

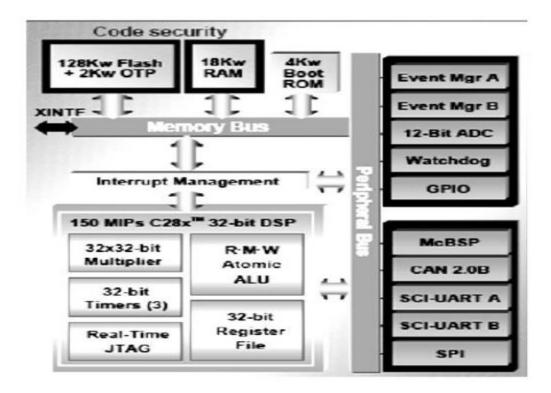

| 7.2 ARCHETECTURE OF TI C2000 AND TMS320F2812   | 90 |

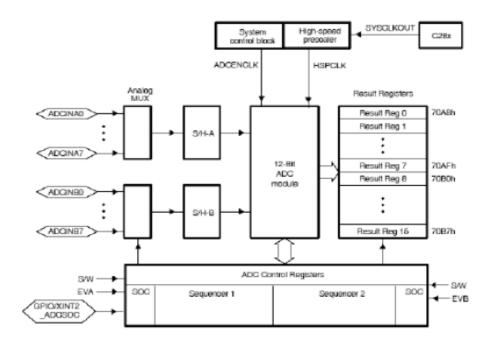

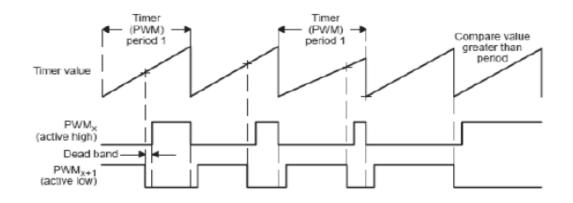

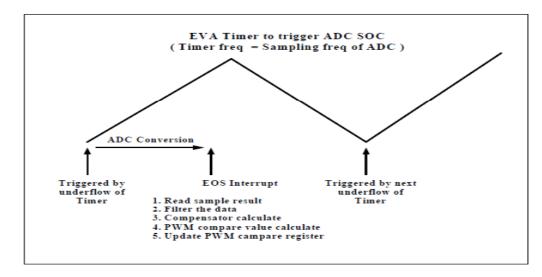

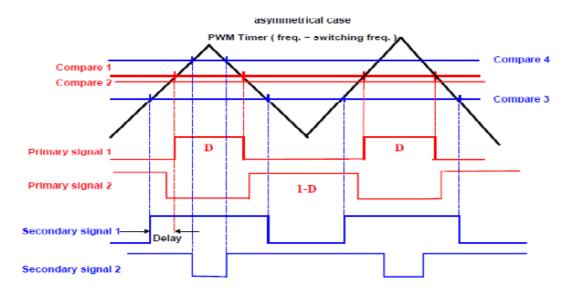

| 7.2.1 PWM GENERATORS AND ADC OF TMS320F2812    | 92 |

| 7.3 CONTROLLER IMPLEMENTATION WITH TMS320F2812 | 93 |

| 7.3.1 ADC IMPLEMENTATION                       | 93 |

| 7.3.2 PWM IMPLEMENTATION                       | 94 |

| 7.3.3 PROGRAM STRUCTURE                        | 95 |

| CHAPTER EIGHT: SIMULATION RESULTS              | 97 |

| 8. SIMULATED MODEL OF DC-DC BUCK CONVERTER     | 98 |

| 8.1 SIMULINK MODEL OF PID COMPENSATED SYSTEM                                         |

|--------------------------------------------------------------------------------------|

| 8.2 SYMULINK MODEL OF BUCK CONVERTER WITH FUZZY LOGIC CONTROLLER 100                 |

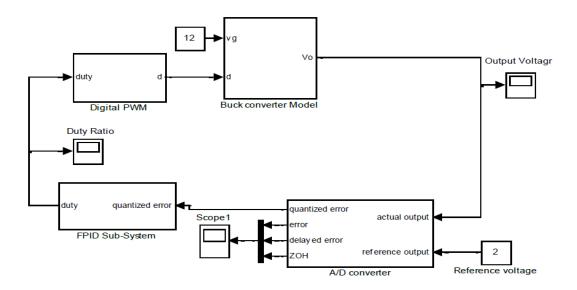

| 8.3 SIMULINK MODEL OF FPID COMPENSATED BUCK CONVERTER 101                            |

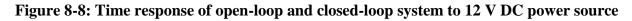

| 8.3.1 RESPONSE TO 12V DC POWER SOURCE 102                                            |

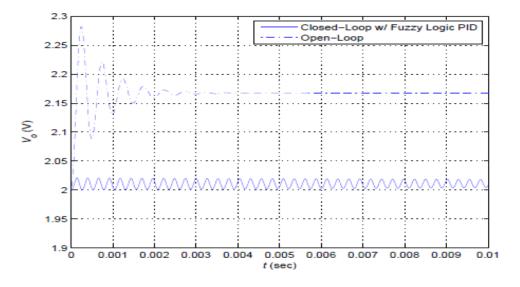

| 8.3.2 RESPONSE TO 1V STEP CHANGE IN POWER SOURCE                                     |

| 8.3.3 RESPONSE TO 1AMP STEP CHANGE IN LOAD CURRENT 103                               |

| 8.3.4 COMPARISON BETWEEN ANALOG PID, FUZZY AND FPID CONTROLLER 104                   |

| 8.4 SLIDING MODE CONTROL FOR DC-DC BUCK CONVERTER 105                                |

| 8.4.1 OUTPUT RESPONSE DUE TO CHANGE IN LOAD RESISTANCE FROM 150hm TO 100hm AND 150hm |

| 8.5 CONCLUSION                                                                       |

| 8.6 FUTURE WORK                                                                      |

| REFERANCES | 09 |

|------------|----|

|------------|----|

## **LIST OF FIGURES**

| Figure 1-1:Interdisciplinary nature of power electronics             | 16 |

|----------------------------------------------------------------------|----|

| Figure 1-2 : Power supply tree                                       | 17 |

| Figure 2-1: Practical linear series regulator circuit                | 23 |

| Figure 2-2: Basic circuits for linear regultors                      | 24 |

| Figure 2-3: practical circuit of switch mode regulator               | 25 |

| Figure 2-4: Non-isolated DC/DC converter topologies                  | 27 |

| Figure 2-5: Isolated DC/DC converter topologies                      | 28 |

| Figure 2-6: Multiple switches DC/DC converters                       | 29 |

| Figure 2-7: Feedback control loop for switching converter            | 30 |

| Figure 2-8: Buck regulator in the system                             | 32 |

| Figure 3-1: General DC-DC converter circuit                          | 34 |

| Figure 3-2: On state                                                 | 34 |

| Figure 3-3: Off state                                                | 35 |

| Figure 3-4: (a) continuous mode (b) Discontinuous                    | 35 |

| Figure 3-5: Step down converter states                               | 36 |

| Figure 3-6: Inductor current                                         | 39 |

| Figure 3-7: The source current                                       | 39 |

| Figure 3-8: Current through the low side MOSFET                      | 40 |

| Figure 3-9: Output voltage ripple in a step-down converter           | 41 |

| Figure 3-10: Buck converter circuit                                  | 45 |

| Figure 3-11: Buck converter (a) switch on,(b) switch off             | 45 |

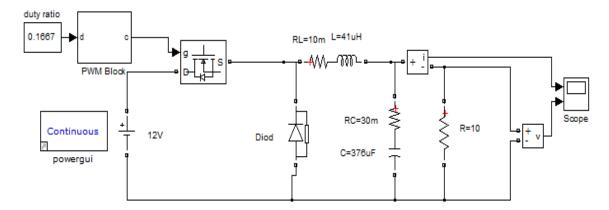

| Figure 3-12: Simulink model of buck converter                        | 48 |

| Figure 3-13: Uncompensated open loop time response of buck converter | 48 |

| Figure 3-14: Open loop response to 1Amp step change in load current  | 49 |

| Figure 3-15: Open loop response to 1v step change in source voltage  | 50 |

| Figure 4-1: PID compensated system                                   | 52 |

| Figure 4-2: Close loop system                                        | 53 |

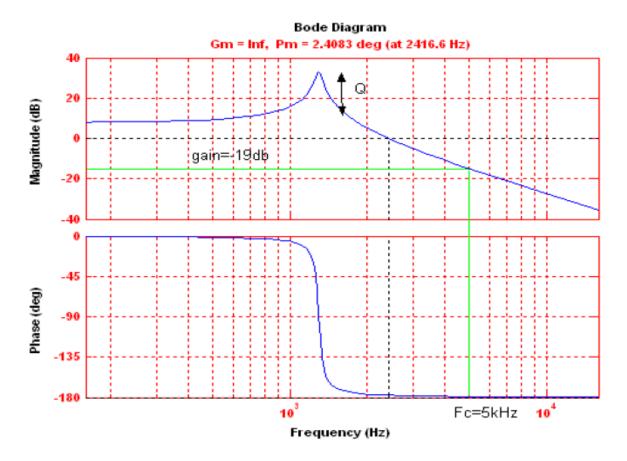

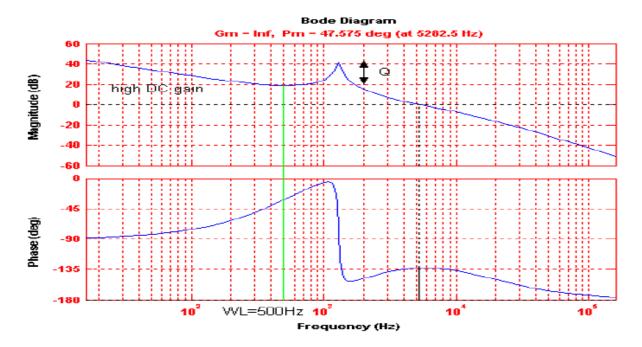

| Figure 4-3                                  | : Bode plot the open loop system                                             | 56 |  |

|---------------------------------------------|------------------------------------------------------------------------------|----|--|

| Figure 4-4                                  | : Bode plot of compensated system                                            | 57 |  |

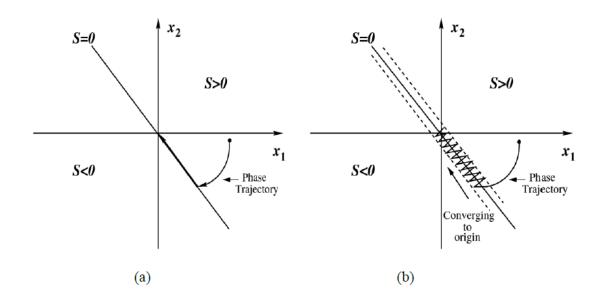

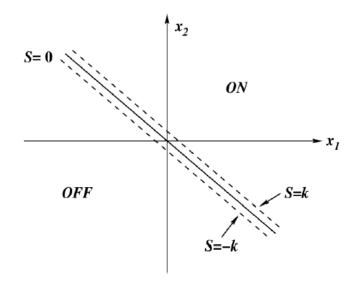

| Figure 5-1                                  | : Phase plot for (a) ideal SM control (b) actual SM control                  | 52 |  |

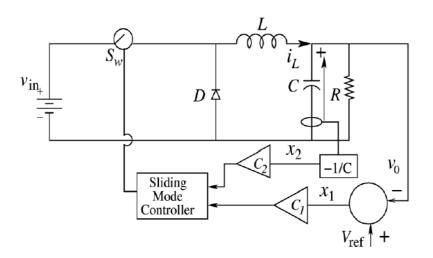

| Figure 5-2                                  | : Basic structure of SMC buck converter system                               | 56 |  |

| Figure 5-3                                  | : Sliding line on x1-x2 phase plane                                          | 70 |  |

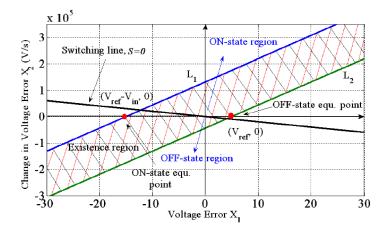

| Figure 5-4                                  | : Region of existence of sliding mode mapped in the phase plane              | 71 |  |

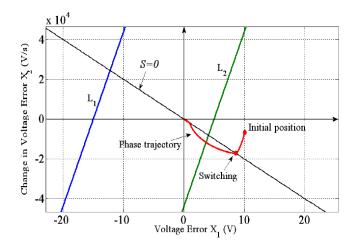

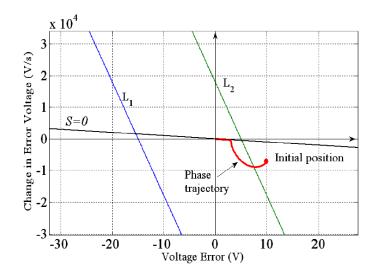

| Figure 5-5                                  | : Evolution of phase trajectory in phase plane C1>C2/RC                      | 72 |  |

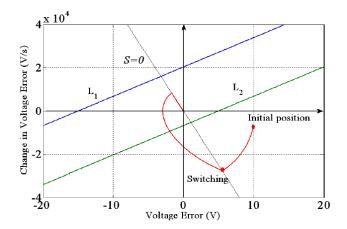

| Figure 5-6                                  | : Phase plane diagram C1>C2/RC                                               | 72 |  |

| Figure 5-7                                  | : Phase plane diagram for C1 <c2 rc<="" td=""><td>73</td></c2>               | 73 |  |

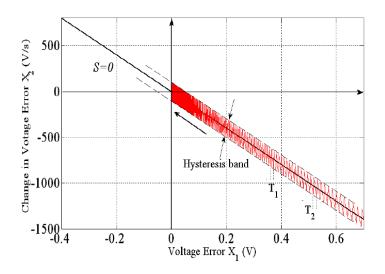

| Figure 5-8                                  | : Chattering phenomena of sliding mode control                               | 73 |  |

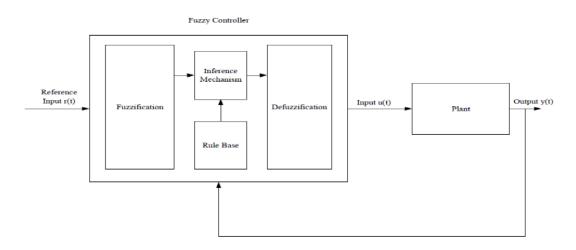

| Figure 6-1                                  | : Block diagram of fuzzy control system                                      | 75 |  |

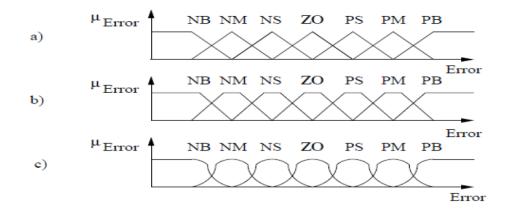

| Figure 6-2                                  | : Membership function shapes                                                 | 76 |  |

| Figure 6-3                                  | : Fuzzy operations                                                           | 78 |  |

| Figure 6-4                                  | : Fuzzy model rule base with two input and single output                     | 79 |  |

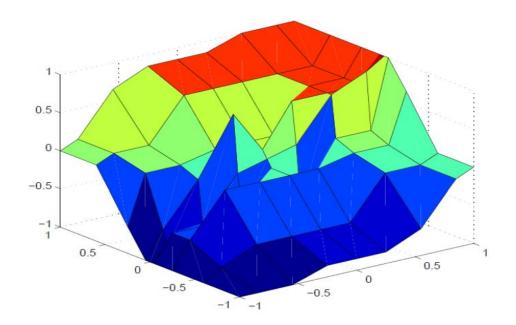

| Figure 6-5                                  | : Fuzzy model rule base with two input and single out put shown as a surface | 79 |  |

| Figure 6-6                                  | : Classification of fuzzy PID controller                                     | 81 |  |

| Figure 6-7                                  | : Single input fuzzy PID controller                                          | 81 |  |

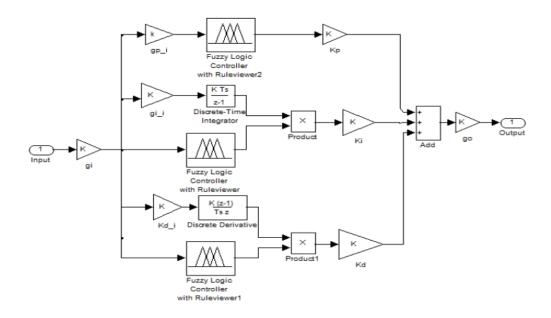

| Figure 6-8                                  | : Simulink model of self-tuning FPID controller                              | 82 |  |

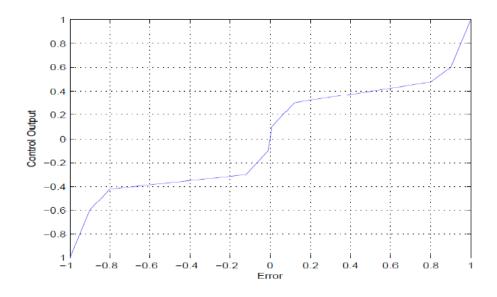

| Figure 6-9                                  | : Centers for input/output fuzzy set for proportional gain                   | 84 |  |

| Figure 6-1                                  | 0: Proportional gain control surface                                         | 85 |  |

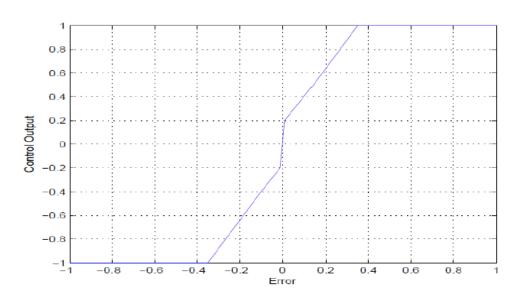

| Figure 6-1                                  | 1: Centers for input/output fuzzy set for integral gain                      | 86 |  |

| Figure 6-1                                  | Figure 6-12: Integral gain control surface                                   |    |  |

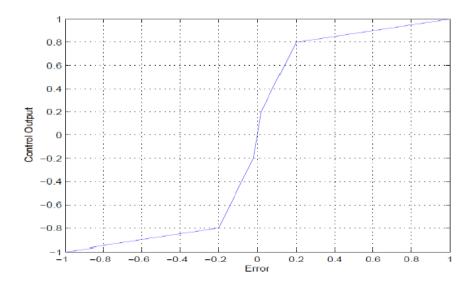

| Figure 6-1                                  | 3: Centers for input/output fuzzy set for derivative gain                    | 87 |  |

| Figure 6-1                                  | 4: Derivative gain control surface                                           | 87 |  |

| Figure 7-1                                  | : Architecture of TMS320C2812                                                | 91 |  |

| Figure 7-2: Structure of ADC in TMS320F2812 |                                                                              |    |  |

| Figure 7-3                                  | : Generating the PWM waveform in TMS320F2812                                 | 93 |  |

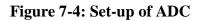

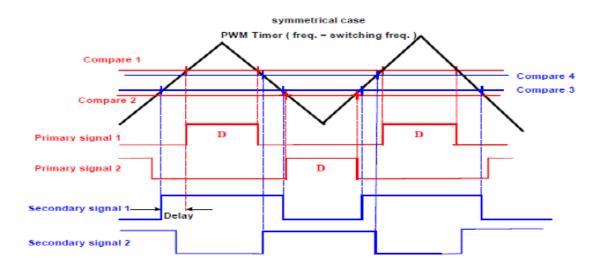

| Figure 7-4                                  | : Setup of ADC                                                               | 93 |  |

| 13                                          | Department of Electrical And Electronic Engineering, IUT, OIC.               |    |  |

| Figure 7-5: Symmetrical PWM signals generating                                                       | 95  |

|------------------------------------------------------------------------------------------------------|-----|

| Figure 7-6: Asymmetrical PWM signals generating                                                      | 95  |

| Figure 7-7: Flow chart of controller implementation in DSP                                           | 96  |

| Figure 8-1: open loop Simulink model of buck converter                                               | 98  |

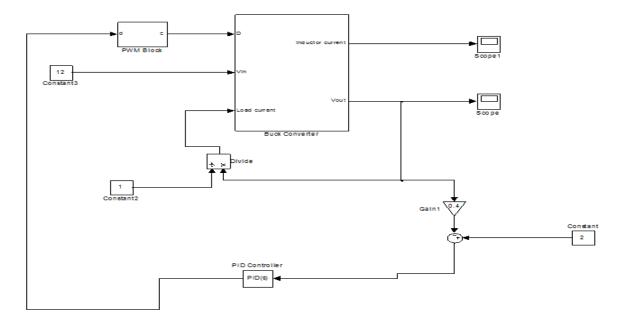

| Figure 8-2: PID compensated Buck converter                                                           | 99  |

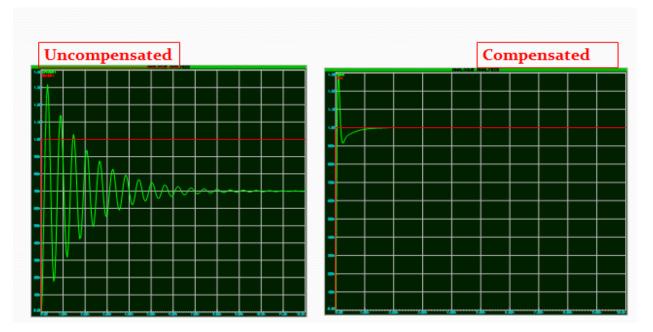

| Figure 8-3: Step response of uncompensated and PID Compensated Buck converter                        | 99  |

| Figure 8-4: Simulink model of Buck converter with Fuzzy logic Controller                             | 100 |

| Figure 8-5: Output response of Buck converter with Fuzzy logic controller                            | 100 |

| Figure 8-6: FPID controller                                                                          | 101 |

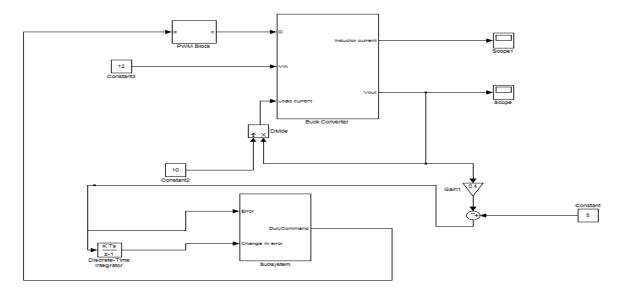

| Figure 8-7: Simulink model of FPID compensated Buck converter                                        | 101 |

| Figure 8-8: Time response of open loop and close loop system to 12v DC power source                  | 102 |

| Figure 8-9: Time response of open loop and close loop system to 1v step change in power source       | 103 |

| Figure 8-10: Time response of open loop and close loop system to 1A step change in load current      | 104 |

| Figure 8-11: Basic structure of an SMC Buck converter system                                         | 105 |

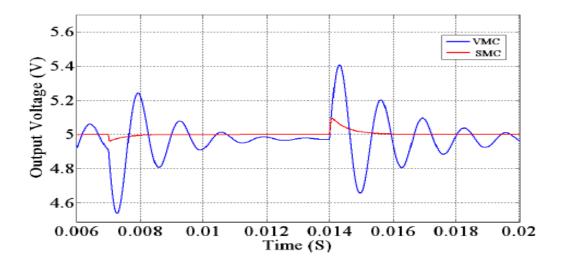

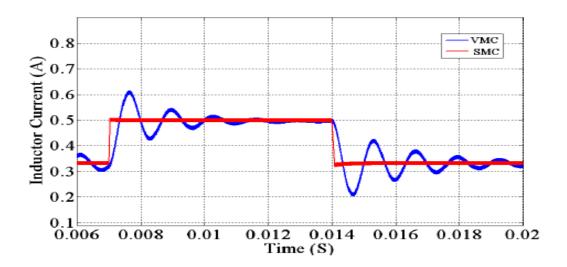

| Figure 8-12: Output response due to step change in load resistance from 150hm to100hm and back to 15 |     |

| Figure 8-13: Inductor current response due to step change in load resistance                         | 106 |

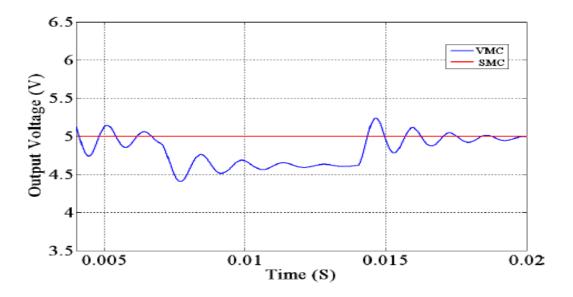

| Figure 8-14: Output voltage response for a change in input voltage from 20v to 15v and back to 20v   | 107 |

## **LIST OF TABLES**

| Table 2-1: Comparison between linear and switch mode regulators | 26  |

|-----------------------------------------------------------------|-----|

| Table 8-1: Circuit parameters of Buck converter                 | 98  |

| Table 8-2: Comparison between PID, FUZZY and FPID controller    | 104 |

# CHAPTER 01 INTRODUCTION

#### **1. INTRODUCTION**

#### **1.1 OVERVIEW:**

Over the years as the portable electronics industry progressed, different

requirements evolved such as increased battery lifetime, small and cheap systems, brighter, full-color displays and a demand for increased talk-time in cellular phones. An ever increasing demand from power systems has placed power consumption at a premium. To keep up with these demands engineers have worked towards developing efficient conversion techniques and also has resulted in the subsequent formal growth of an interdisciplinary field of Power Electronics. However it comes as no surprise that this new field has offered challenges owing to the unique combination of three major disciplines of electrical engineering: electronics, power and control [1].

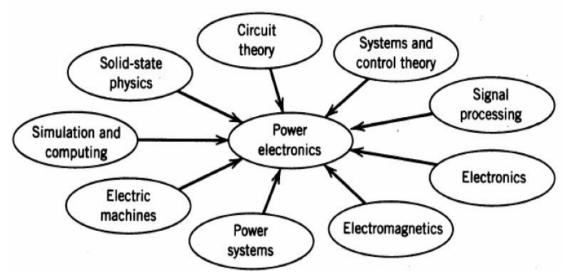

Figure 1-1: Interdisciplinary nature of Power Electronics [1]

These multi-discipline technologies, as highlighted in Figure 1-1, have involved control theory, filter synthesis, signal processing, thermal control, and magnetic components design [8].

Main target in power electronics is to convert electrical energy from one form to another. To make electrical energy to reach the load with highest efficiency is the target to be achieved. Power electronics also targets to reduce the size of the device to convert these energy which aims to reduce cost, smaller in size and high availability. In this project the power electronic device that use is dc to dc converter.

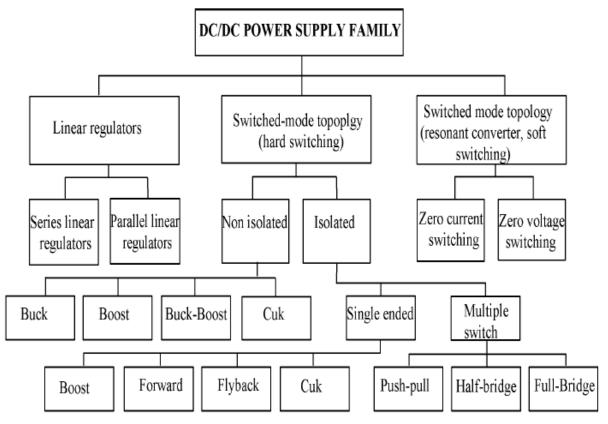

Figure 1-2: Power Supply Tree [2]

Figure 1-2 shows the different power supply families. The dc-dc converter for this project is buck converter. Buck converter is use to convert unregulated dc input to a controlled dc output with a desired voltage level.

#### **1.2 OBJECTIVE:**

Switched mode power supplies (SMPSs) are needed to convert electrical energy from one voltage level to another. SMPSs are widely used in DC-DC conversions, where the input is a DC voltage that can be, for example, a rectified line voltage, an output voltage of a power factor correction (PFC) circuit, a battery or fuel cell voltage.

In such power conversions, DC-DC converters operate at relatively high switching frequencies, and this enables the use of small inductive components which improve the dynamic behavior and reduce the size of the converter.

Despite the above-mentioned benefits of SMPSs, there are several parameters, which are not desired and have a strong influence on the converters behavior, being mainly:

- > Non-linear components in the converter structure,

- Line and load variations, and

Electro-magnetic interferences (EMI).

The DC-DC converter has non-linear components (capacitors, inductors, and resistors), the value of which changes non-linearly if the converter is disturbed or may change within time. The effects of these converter parameters variations are given in [4].

For the design of a DC-DC converter, a nominal input voltage and load values are suggested. In practice, these nominal values may deviate. For example, 20% line variation is expected or the nominal load may deviate to no-load or full load. These phenomena are studied in [4-9].

The purpose of electro-magnetic interference (EMC) is to ensure that an electronic system can operate in its electromagnetic environment without responding to electrical noise or generating unwanted electrical interference. For example, in DC-DC power supply EMI has an influence on the converter component. The EMI effects on the DC-DC converter are studied in [10].

These parameters force the converter to deviate from the desired operating condition. If the parameter deviation increases, this will cause the converter not to operate in steady state. Many control methods are used to control SMPSs and solve the problem mentioned above. Each control method has its own advantages and drawbacks due to which that particular control method appears to be the most suitable control method under specific conditions, compared to other control methods. It is always demanded to obtain a control method that has the best performances under any conditions.

#### **1.3 PROBLEM STATEMENT:**

The output voltage (Vo) of buck alone usually is unstable. So criteria must concern is rise time, overshoot, settling time and steady state error, to get the desired output and to reduce the undesired output.

Problem statement:

- Steady state error: The output of buck alone is not reaching the desire value Meaning it has error.

- ➢ Rise time : The rise time is too long

- Settling time : The output oscillating too long, it takes time to reach the stable state.

- > Overshoot : The over shoot is high.

#### **1.4 THESIS ORGANIZATION:**

The thesis defines the causes by which the selecting of a specific control method is influenced, i.e. the fuzzy PID control (FPID), over other control methods. A detailed research analysis is done for the FPID controller.

The research work is done in following logical sequence:

- Study of the DC-DC converter topologies,

- Study of the control methods used to control the DC-DC converters,

- > Study of the traditional PID control as one control method,

- > Study of Sliding mode control as the second control method,

- Study of the Fuzzy logic control as a third control method,

- > Study of a self-tuning FPID controller for the control of Buck Converter.

It is noticed that the influence of the FPID on the behavior of the converter in steady state and under dynamic conditions is better than that of the PID control, Sliding mode control and fuzzy logic control. The FPID is applied to the DC-DC buck converter and the response of the converter is analyzed in steady state and under dynamic conditions. The research work process can be described as follows:

In chapter two, linear power supply is analyzed and its advantages and drawbacks are discussed. In the next section, SMPSs are studied in detail and their benefits and drawbacks over linear regulators are shown. A classification of SMPSs into isolated and non-isolated DC/DC converters is given. In last section of the chapter the feedback control system is summarized.

Chapter three focuses on analyzing the topology and operation of the DC-DC buck converter. The modeling of the topology, including steady state average model and small-signal dynamic model, are established and the related controller compensation design issues are addressed based on the models and analysis.

Chapter four discusses digital and analog control, which includes the theory, methodology and critical issues of a digital and analog controller. As a case study, a digital and analog PID compensator is designed based on the specifications of the given power stage. Also, this chapter explores the modeling and simulation of a digital controller with DSPs.

Chapter five describes in detail SMC (Sliding Mode Controller) and a briefly reviews the history of SMC. The introductory part of the chapter introduces Prof. Utkin who is considered to be one of the first scientists having dealt with the subject of SMC, and briefly describes his most important researches in the field of SMC. In the next section, a review of the theory of SMC is given, more particularly; the existence condition, the reaching condition, the system description in sliding mode, the chattering. These mathematical equations are used to prove the analysis. The researches on and applications of SMC in electrical and mechanical systems are shown in a diagram. The SMC is implemented to the DC/DC Buck converter and the above-mentioned SMC theories are proven. The results are verified with the simulation results. Finally, the researches on and applications of the SMC for DC/DC converters are given in details.

In Chapter six fuzzy logic control is introduced based on that knowledge an intelligent selftuning fuzzy PID controller is proposed for the control of buck converter. The fuzzy logic control is used to tune the proportional, integral and derivative gain of the conventional PID controller based on certain function of the error signal to obtain stable and fast transient response in-spite of changes in load and source sides.

Chapter seven explores DSP implementation of a digital controller, which brings in the introduction of DSP chips, to be specific, TI C24X and TMS320F2812. Then, the PWM generators and ADC of TMS320F2812 are emphasized as the important devices in the controller. Controller implementation based on the TMS320F2812 is described as one of the important part of the thesis.

Chapter eight provides and analyzes the experimental results of closed-loop and open loop system. It should be noted that the overall performance of the closed system is improved significantly.

In chapter eight, the conclusions obtained from the research work are given. The main contribution of this thesis is summarized and suggestions for future research work are given. And in the last the references of the above studies are given.

## CHAPTER 02 DC-DC POWER SUPPLY

#### 2. DC-DC POWER SUPPLY

#### 2.1 INTRODUCTION:

DC-DC converters are electronic devices that are used whenever we want to change DC electrical power efficiently from one voltage level to another. Generically speaking the use of a switch or switches for the purpose of power conversion can be regarded as a SMPS. From now onwards whenever we mention DC-DC Converters we shall address them with respect to SMPS.

A few applications of interest of DC-DC converters are where 5V DC on a personal computer motherboard must be stepped down to 3V, 2V or less for one of the latest CPU chips; where 1.5V from a single cell must be stepped up to 5V or more, to operate electronic circuitry. In all of these applications, we want to change the DC energy from one voltage level to another, while wasting as little as possible in the process. In other words, we want to perform the conversion with the highest possible efficiency.

DC-DC Converters are needed because unlike AC, DC can't simply be stepped up or down using a transformer. In many ways, a DC-DC converter is the DC equivalent of a transformer. They essentially just change the input energy into a different impedance level. So whatever the output voltage level, the output power all comes from the input; there's no energy manufactured inside the converter. Quite the contrary, in fact some is inevitably used up by the converter circuitry and components, in doing their job.

The regulated power supply technology can be divided into two distinct forms: firstly, the linear regulator which can be either a series or parallel regulator and, secondly, the switched-mode conversion technique. Switched-mode technology is multi-facetted with a wide variety of topologies achieving the result of providing a regulated DC voltage.

The main difference between the linear and switched-mode regulator is in efficiency. The linear regulator utilizes simple techniques of controlled energy dissipation to achieve a regulated output voltage independent of line and load variations. It is, therefore, inherently inefficient, especially when a wide input voltage range has to be applied. When linear techniques are applied to regulate a low voltage from the mains (110V or 240V AC source) then the disadvantages of the technique become apparent.

#### 2.2 LINEAR POWER SUPPLY:

Linear power supplies provide significant advantages over switching regulators in:

- > Simplicity

- $\succ$  Cost and

- Output Noise

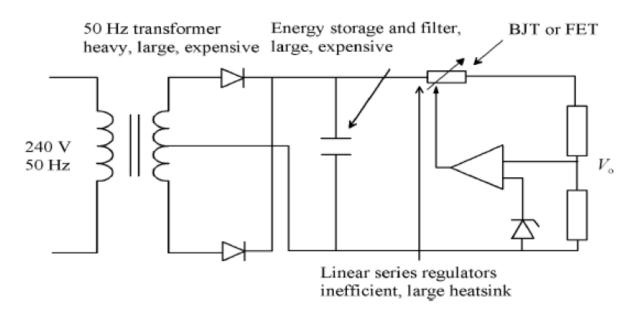

Figure 2-1: Practical linear series regulator circuit.

A typical linear power supply is shown in Figure 2-1, which has the following disadvantages:

- > The main transformer operating at a low frequency is heavy, large and expensive,

- > Large heat-sinking is required to dissipate the heat generated by the regulating element, and

- $\succ$  The efficiency is low.

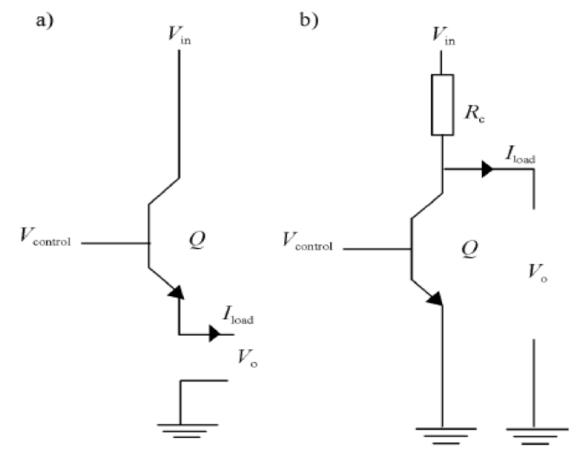

Two major types of linear regulators are considered and shown in Figure 2-2. The simple series regulator in Figure 2-2.a is a transistor connected as an emitter follower (or source follower in FET). The transistor operates in its linear active region rather than a switch. The emitter voltage *V*o becomes a function of *V* control rather than the input voltage or the load current and the term linear regulator is appropriate to describe the circuit. The power loss and efficiency are:

$$P_{\text{loss}} = (V_{\text{in}} - V_{\text{o}})I_{\text{load}}, \qquad (2.1)$$

$$V_{\text{o}}I_{\text{load}} = V_{\text{o}}$$

$$\eta = \frac{V_{\text{or}} I_{\text{load}}}{V_{\text{in}} I_{\text{load}}} = \frac{V_{\text{o}}}{V_{\text{in}}}.$$

(2.2)

The shunt regulator shown in Figure 2-2.b resembles a common emitter amplifier circuit. The transistor, once again, is used in the linear active region. The collector current will be  $\beta I$ b rather than the function of the load current. Again, the output is a linear function of the control and the

circuit is another example of a linear regulator. The losses and efficiency for the shunt regulator are:

$$P_{\rm loss} = V_{\rm o}I_{\rm c} + (I_{\rm load} + I_{\rm c})^2 R_{\rm c}, \qquad (2.3)$$

$$\eta = \frac{V_{\rm o}I_{\rm load}}{V_{\rm in}(I_{\rm load} + I_{\rm c})} \,. \tag{2.4}$$

With no load there is a significant loss because  $Ic \neq 0$ , and, in best the case where Iload >> Ic, the efficiency becomes Vo/Vin.

Figure 2-2: Basic circuits for linear regulators. a) Series regulator, b) shunt regulator

Linear regulators acting as converters limit the efficiency. However, since they bring the possibility of perfect regulation, linear regulators are often used as elements of larger conversion systems.

#### 2.3 SWITCH MODE POWER SUPPLY:

High frequency switching converters are power circuits in which the semiconductor devices switch at a rate that is *fast compared to the variation of the input and output waveforms*.

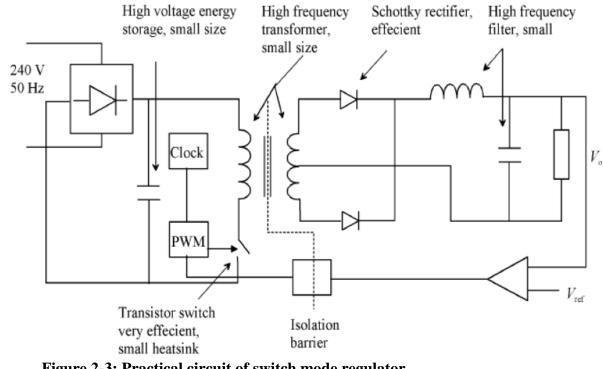

Figure 2-3 shows a Practical circuit of switch mode regulator. The difference between the switching frequency and the frequency of the external waveforms is large enough to permit the use of low-pass filters to remove the unwanted switching frequency components. High frequency switching converters are used most often as interfaces between dc systems of different voltage levels. These converters are known as *high-frequency dc/dc converters*, and examples of their use are the power supplies in computers and other electronic equipment. High frequency switching converters can also be used as an interface between dc and ac systems [11].

Figure 2-3: Practical circuit of switch mode regulator

The time that the switch remains closed during each switch cycle is varied to maintain a constant output voltage. The switching regulator is much more efficient than the linear regulator achieving efficiencies as high as 80% to 95% in some circuits. In contrast, the linear regulator usually exhibits only 50% to 60% efficiency. With higher efficiency smaller heat sinks will be required because lesser heat is dissipated. This further result in SMPS, that can be packaged in a fraction of the size of linear regulators.

There is also another advantage of Switching Regulators and that is that the energy stored by inductor & capacitor can be transformed to output voltages that can be greater than input (boost), negative (inverter), or can be transferred through a transformer to provide electrical isolation with respect to the input.

Unlike linear regulators, switched power supplies can step up or step down the input voltage [12].

All of our discussion can be summarized with a comparison in Table 2-1:

|              | Linear                                                                                                                                                                | Switching                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function     | <b>Only steps down</b> ; input voltage must be greater than output.                                                                                                   | Steps up, steps down, or inverts                                                                                                                              |

| Efficiency   | Low to medium, but actual battery<br>life depends on load current and<br>battery voltage over time; high if<br>V <sub>IN</sub> -V <sub>OUT</sub> difference is small. | <b>High,</b> except at very low load currents $(\mu A)$ , where switch-mode quiescent current is usually higher.                                              |

| Waste Heat   | <b>High,</b> if average load and/or input/output voltage difference are high                                                                                          | Low, as components usually run cool for power levels below 10W                                                                                                |

| Complexity   | Low, which usually requires only<br>the regulator and low-value bypass<br>capacitors                                                                                  | Medium to high, which usually<br>requires inductor, diode, and filter<br>caps in addition to the IC; for high-<br>power circuits, external FETs are<br>needed |

| Size         | <b>Small to medium</b> in portable designs, but may be larger if heat sinking is needed                                                                               | Larger than linear at low power, but<br>smaller at power levels for which<br>linear requires a heat sink                                                      |

| Total Cost   | Low                                                                                                                                                                   | Medium to high, largely due to external components                                                                                                            |

| Ripple/Noise | <b>Low</b> ; no ripple, low noise, better noise rejection.                                                                                                            | Medium to high, due to ripple at switching rate                                                                                                               |

Table 2-1: Comparison between Linear and Switch-Mode Regulators [13]

#### 2.4 **TYPES OF CONVERTERS:**

Currently, dc/dc converters can be divided into two broad categories:

- Non-isolated dc/dc converters

- Isolated dc/dc converters

- Multiple switched converter

#### 2.4.1 NON-ISOLATED DC-DC CONVERTERS:

The non-isolated converter usually employs an inductor, and there is no dc voltage isolation between the input and the output. The vast majority of applications do not require dc isolation between input and output voltages. The non-isolated dc-dc converter has a dc path between its input and output. Battery-based systems that don't use the ac power line represent a major application for nonisolated dc-dc converters. Point-of-load dc-dc converters that draw input power from an isolated dcdc converter, such as a bus converter, represent another widely used non-isolated application.

Most of these dc-dc converter ICs use either an internal or external synchronous rectifier. Their only magnetic component is usually an output inductor and thus less susceptible to generating electromagnetic interference. For the same power and voltage levels, it usually has lower cost and fewer components while requiring less pc-board area than an isolated dc-dc converter. For lower voltages (12V) non-isolated buck converters can be used.

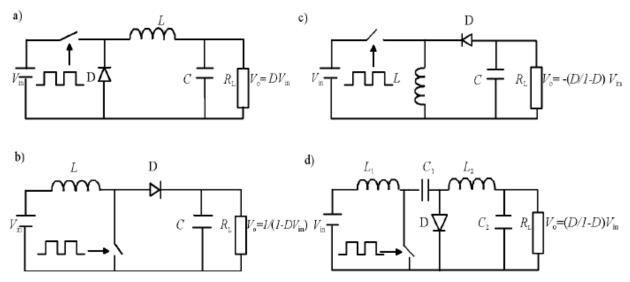

The non-isolated DC/DC converters family shown in Figure 2-4 can be classified as follows:

- Buck converter (step down DC/DC converter),

- Boost converter (step up DC/DC converter),

- Buck-Boost converter (step up/down DC/DC converter, opposite polarity), and

- Cuk converter (step up/down DC/DC converter).

Figure 2-4: Non- isolated DC/DC converter topologies a) Buck converter, b) Boost converter, c) Buck- Boost converter, and d) Cuk converter.

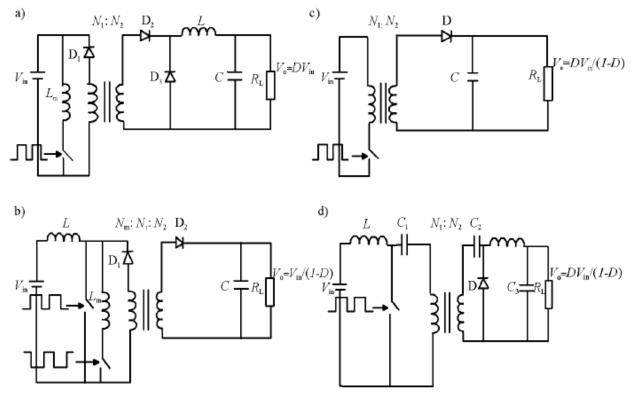

#### 2.4.2 ISOLATED DC-DC CONVERTER:

For safety considerations, there must be isolation between an electronic system's ac input and dc output. Isolation requirements cover all systems operating from the ac power line, which can include an isolated front-end ac-dc power supply followed by an isolated "brick" dc-dc converter, followed by a non-isolated point-of-load converter. Typical isolation voltages for ac-dc and dc-dc power supplies run from 1500 to 4000V, depending on the application. An isolated converter employs a transformer to provide dc isolation between the input and output voltage which eliminates the dc path between the two.

Isolated dc-dc converters use a switching transformer whose secondary is either diode-or synchronous-rectified to produce a dc output voltage using an inductor capacitor output filter. This configuration has the advantage of producing multiple output voltages by adding secondary transformer windings. For higher input voltages (48V) transformer isolated converters are more viable [14].

By inserting isolation transformers into the four basic non-isolated switching regulator topologies, four single-ended isolated switching DC/DC converters can be obtained, shown in Figure 2-5:

Figure 2-5: Isolated DC/DC converter topologies a) Forward converter, b) Isolated Boost converter, c) Flyback converter, and d) Isolated Cuk converter.

The four types of isolated dc-dc converters which are shown in figure 2-5 are:

> The Forward converter (step down DC/DC converter),

- > The Isolated Boost converter (step up DC/DC converter),

- > The Flyback converter (step up/down DC/DC converter), and

- > The Isolated Cuk converter (step up/down DC/DC converter).

The isolated DC/DC Buck and Buck-Boost topologies are more commonly referred to as the Forward and Flyback DC/DC converter respectively, and are the most used topologies in commercially manufactured switched-mode power supplies.

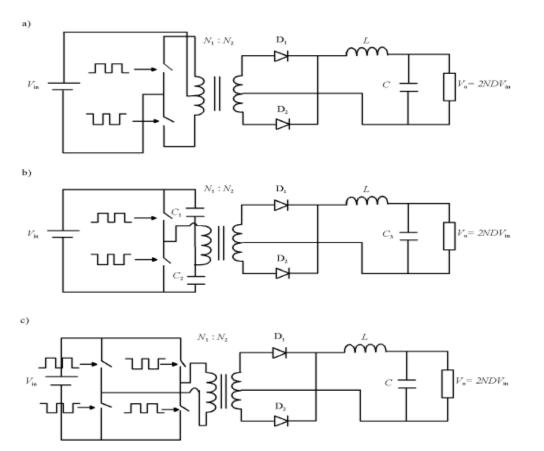

#### 2.4.3 MULTIPLE SWITCHED CONVERTERS:

The main disadvantage of single switch topologies is that the transistor switch should be capable of high-voltage blocking (twice the DC input voltage), especially when operating from a rectified AC mains supply. The single switch topology is not an ideal solution for higher power converters either, since these converters need a higher current rating of the transistor switch. Therefore, another group of isolated DC/DC converters utilizing more than one switch can be identified. Figure 2-6 illustrates three multiple switch topologies:

## Figure 2-6: Multiple switches DC/DC converters a) Push-pull converter, b) Half-bridge converter, and c) Full-bridge

The three types of Multiple switched Dc-Dc converters which are shown in figure 2-6 are:

- > The Half-bridge DC/DC converter,

- > The Full-bridge DC/DC converter, and

- The Push-pull DC/DC converter

These topologies have the additional advantage over the single-ended Forward and Flyback DC-DC converters that a full flux excitation of the transformer core occurs instead of only a half core flux capability. This makes these multiple switch topologies more suited for higher power operation.

#### 2.5 FEEDBACK CONTROL FOR DC-DC CONVERTER:

In a DC-DC converter application, it is desired to obtain a constant output voltage in spite of disturbances in input voltage and load current. Therefore, the idea behind the use of negative feedback for control is to build a circuit that automatically adjusts the duty cycle as needed to obtain the desired output voltage with high accuracy, regardless of disturbances in input and load.

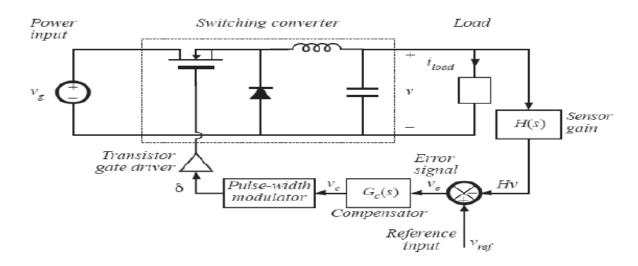

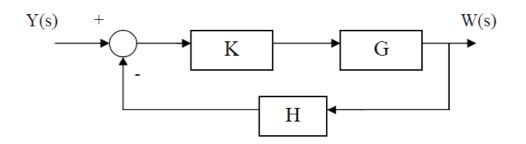

A block diagram of a feedback system is shown in Figure 2-7. The output voltage v(t) is measured using a —sensor with transfer function of H(s) [9]. The sensor output H(s)v(s) is compared with a voltage reference Vref(s). The error between H(s)v(s) and Vref(s) is feed to compensator that amplifies error signal and makes the output voltage regulated around reference voltage. In practice, the error is usually nonzero and nonetheless small enough. A compensator gain Gc(s) helps to obtain a small error and improve the stability and performance of the system. The PWM (pulse width modulator) modulator is used to generate —digital pulse width feed into the switch of converter. The pulse width changes with the comparator output voltage Vc(t).

#### Figure 2.7 Feedback control loop for switching converter

The traditional approaches for controllers of DC-DC converters based on duty ratio adjustment have relied on analog implementation schemes. The above mentioned control strategies based on analog techniques offer robust control, but suffer from serious limitations such as sensitivity to noise and temperature change. Hence, this trend has moved towards digital control schemes, which offer multitudinous benefits. Digital controllers for switching power supplies offer a number of advantages including a reduction of the number of passive components, programmability, implementation of more advanced control algorithms and additional processing options, as well as reduced sensitivity to parameter variations.

Generally, there are several implementation approaches for digital controllers today, which include Microprocessor/DSP's (Digital Signal Processors), FPGA (Field Programmed Gates Array) and Custom IC Design. The features of these approaches are compared in the following:

#### 2.5.1 DSP:

- > DSP chips can be reprogrammed;

- > The speed is generally slower than ICs;

- > Implementation is exceedingly complex for the intended application;

- > DSP is costly over custom IC design;

- High frequency power converters have to use high performance DSPs

#### 2.5.2 FPGA:

- FPGA can be programmed on site;

- > The processing is faster than a general purpose DSP;

- For FPGA design there is no physical manufacturing step, which results in very short design time;

- > FPGA's typical price is higher than DSPs;

#### 2.5.3 CUSTOM IC DESIGN:

- Due to physical design consideration shows typically better performance than FPGA;

- However it results in much longer design time than FPGA since there is a layout step;

- Custom IC design has lower price than FPGA and DSP.

In this thesis, the features that make DSPs effective computational engines for high frequency switching power converters are presented. A case study is introduced in which a DSP-based solution was developed as a controller for DC-DC buck converter, which is widely used in low voltage application. The design, implementation and testing of a DSP-based system are illustrated, and the techniques and challenges in system design based on DSPs are also addressed. DSP designs are optimized to handle real-time applications with high bandwidth requirements.

#### 2.6 WHY WORK ON BUCK CONVERTERS??:

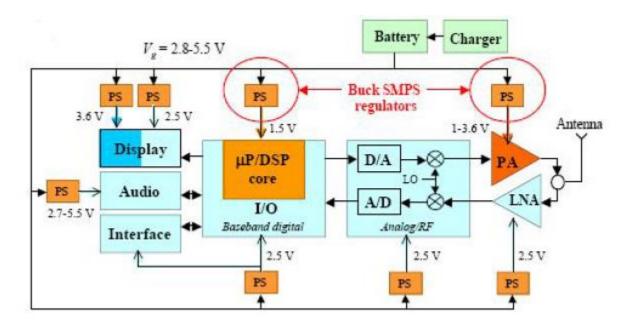

The buck converter is the most widely used dc-dc converter topology in power management and microprocessor voltage-regulator (VRM) applications. Those applications require fast load and line transient responses and high efficiency over a wide load current range. They can convert a voltage source into a lower regulated voltage. For example, within a computer system, voltage needs to be stepped down and a lower voltage needs to be maintained. For this purpose the Buck Converter can be used [15]. Furthermore buck converters provide longer battery life for mobile systems that spend most of their time in "stand-by". Buck regulators are often used as switchmode power supplies for baseband digital core and the RF power amplifier (PA) [35].

The Buck SMPS Regulator in the system is shown in figure 2-8.

Figure 2-8: Buck regulators in the system [35]

# CHAPTER 03 MODELING ANALYSIS AND DESIGN OF DC-DC BUCK CONVERTER

#### 3. BUCK CONVERTER

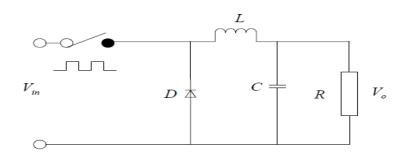

The general Dc-Dc Buck Converter circuit is given in figure 3-1.

Figure 3-1: General Dc-Dc Buck Converter circuit

#### **3.1 STATES OF OPERATION:**

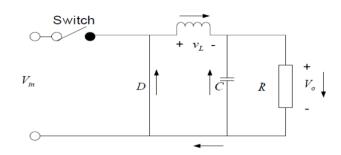

There are two states in which the circuit given in Figure 3-1 operates. That is the ON State and the OFF State. These two states and the active circuit part for those given states are shown in the Figure 3-2 and Figure 3-3.

#### **3.1.1 ON STATE:**

The operation of the buck converter is fairly simple, with an inductor and two switches (usually a transistor and a diode) that control the inductor. It alternates between connecting the inductor to source voltage to store energy in the inductor and discharging the inductor into the load.

Figure 3-2: ON State

Refer to Figure 3-2, when the switch is connected, L is connected to the switch which tends to oppose the rising current and begins to generate an electromagnetic field in its core. Diode D is reverse biased and is essentially an open circuit at this point. The inductor current increases, inducing a positive voltage drop across the inductor and a lower output supply voltage in reference to the input source voltage. The inductor serves as a current source to the output load impedance.

#### **3.1.2 OFF STSTE:**

In the OFF state the switch is open, diode D conducts and energy is supplied from the magnetic field of L and electric field of C. The current through the inductor falls linearly. When the FET switch is off, the inductor current discharges, inducing a negative voltage drop across the inductor. Because one port of the inductor is tied to ground, the other port will have a higher voltage level, which is the target output supply voltage. The output capacitance acts as a low-pass filter, reducing output voltage ripple as a result of the fluctuating current through the inductor. The diode prevents the current flowing from the inductor when the FET switch is off.

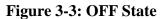

#### 3.2 CONTINUOUS AND DIS-CONTINUOUS CURRENT MODE:

During the ON state and then the subsequent OFF state the Buck Converter can operate in Continuous Mode or Discontinuous Mode. The difference between the two is that in CCM the current in the inductor does not fall to zero. See Figure 3-4.

Figure 3-4: (a) Continuous Mode (b) Discontinuous Mode

Current flows continuously in the inductor during the entire switching cycle in steady state operation. In most Buck regulator applications, the inductor current never drops to zero during full-load operation. Overall performance is usually better using continuous mode, and it allows maximum output power to be obtained from a given input voltage and switch current rating. Energy from the battery is supplying the load and is being stored in the inductor L as a magnetic field. The current through the inductor is rising linearly.

In the DCM the current in the inductor falls to zero and remains at zero for some portion of the switching cycle. It starts at zero, reaches a peak value, and returns to zero during each switching cycle. In applications where the maximum load current is fairly low, it can be advantageous to design for discontinuous mode operation. In these cases, operating in discontinuous mode can result in a smaller overall converter size (because a smaller inductor can be used). Often the output capacitor must be large to keep the voltage constant.

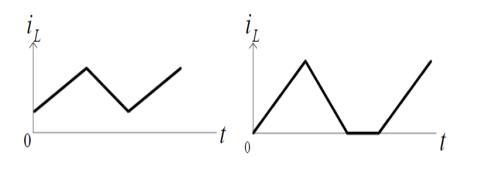

# **3.3 DUTY RATIO CALCULATION:**

For calculation of the duty ratio we will first of all assume that the converter is in steady state. The switches are treated as being ideal, and the losses in the inductive and the capacitive elements are neglected. Also it is important to point out that the following analysis does not include any parasitic resistances (all ideal case). The analysis also has the assumption that the converter is operating in Continuous conduction mode only i.e. iL(t) > 0.

When the switch is on for time duration *ton*, the switch conducts the inductor current and the diode becomes reverse biased. This results in a positive voltage vL = Vd - Vo across the inductor in Figure 3-5(a). This voltage causes a linear increase in the inductor current *iL*. When the switch is turned off, because of the inductive energy storage, *iL* continues to flow. This current now flows through the diode, and vL = -Vo in Figure 3-5(b).

Figure 3-5: Step-down converter circuit states: (a) switch on; (b) switch off

Since in steady-state operation waveform must repeat from one time period to the next, the integral of the inductor voltage vL over one time period must be zero, where Ts = ton + toff:

$$\int_{0}^{T_{S}} V_{L} dt = \int_{0}^{t_{on}} V_{L} dt + \int_{t_{on}}^{T_{S}} V_{L} dt = 0 \qquad (3-1)$$

From Figure 3.5, it implies that areas A and B must be equal. Therefore,

$$(V_d - V_o)t_{on} = V_o(T_s - t_{on})$$

(3-2)

OR

$$\frac{V_o}{V_d} = \frac{t_{on}}{T_s} = D \tag{3-3}$$

Hence in this mode, the voltage output varies linearly with the duty ratio of the switch for a given input voltage and does not depend on any other circuit parameter.

# **3.4 INDUCTOR CALCULATION:**

From Figure 3-5(a) we can derive a simplified differential equation based on the assumption that the voltage across the load, and thereby across the capacitor, is fairly constant. The differential equation in terms of the current through the inductor, when the switch is closed, may now be written as

$$L\frac{di_L(t)}{dt} = V_d - V_o \tag{3-4}$$

Assuming that the circuit has assumed steady state hence there may already be some current in the inductor, *Il,min*, just prior to the closing of switch S. Hence for a time interval  $0 \le t \le TON = DT$ , gives:

$$i_{L}(t) = \frac{V_{d} - V_{o}}{L}t + I_{L,min}$$

(3-5)

The inductor current increases linearly with time and attains its maximum value *IL*,max as

$t \rightarrow TON = DT$  such that

$$I_{L,max} = \frac{V_d - V_o}{L} DT + I_{L,min} \tag{3-6}$$

Defining the change in the current from its minimum to maximum value as the peak-to-peak current ripple *IL*, the equation 3-6 yields an expression for *IL*, as in Eq. 3-7.

$$\Delta I_L = I_{l,max} - I_{L,min} = \frac{V_d - V_o}{L} DT \qquad (3-7)$$

Note that the current ripple is directly proportional to D, the duty cycle, upon which we may not have any control because of the output voltage requirement. However, it is inversely

38 Department of Electrical And Electronic Engineering, IUT, OIC.

proportional to the inductance L upon which we can exert some controls. Thus, the current ripple can be controlled by a proper selection of the inductor.

Let us now analyze the circuit when the switch is in its open position. The inductor current completes its path through the lower side MOSFET and the corresponding differential equation, for  $0 \le t \le TOFF$ , is given by Eq. 3-8.

$$L\frac{di_L(t)}{dt} = -V_o \tag{3-8}$$

From the solution of the above first-order differential equation, we obtain

$$i_L(t) = -\frac{V_o}{L}t + I_{L,max}$$

(3-9)

Where *IL*max is the maximum value of the current in the inductor at the opening of the switch or the beginning of the off period. As  $t \rightarrow Toff = (1-D) T$ , the inductor current decreases to its minimum value *iLmin* such that.

$$i_{L,min}(t) = -\frac{V_o}{L}(1-D)T + I_{L,max}$$

(3-10)

The Eq. 3-10 yields another expression for the peak-to-peak current ripple as given in Eq. 3-11

$$\Delta I_L = I_{l,max} - I_{L,min} = -\frac{V_o}{L} (1 - D)T \qquad (3 - 11)$$

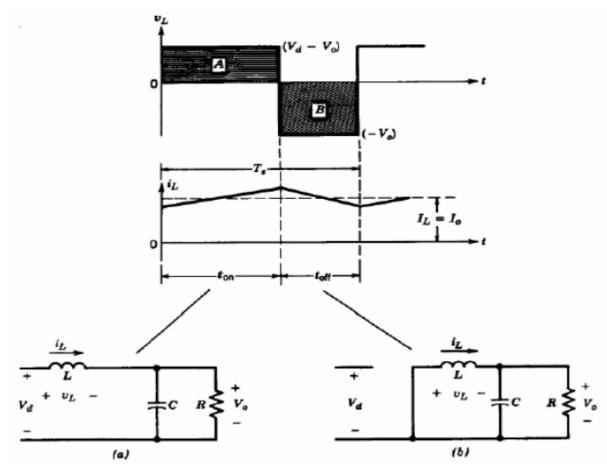

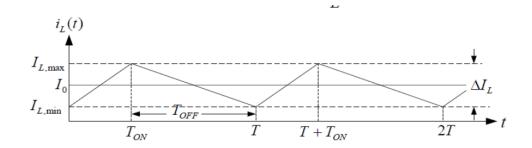

Figure 3-6: Inductor Current

The current through the inductor as given by Eq. 3-5 during the on time and by Eq. 3-9 during the off time is sketched in the Figure 3.6. The average current in the inductor must be equal to the dc current through the load. That is,

$$I_{L,avg} = I_o = \frac{V_o}{R} \tag{3-12}$$

The expressions for the maximum and minimum currents through the inductor may now be written as

$$I_{l,max} = I_{L,avg} + \frac{\Delta I_L}{2} = \frac{V_o}{R} + \frac{V_o}{2L}(1-D)T \qquad (3-13)$$

$$I_{l,min} = I_{L,avg} - \frac{\Delta I_L}{2} = \frac{V_o}{R} - \frac{V_o}{2L}(1-D)T \qquad (3-14)$$

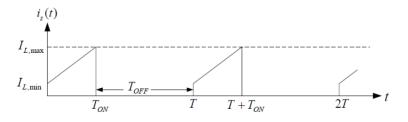

The current supplied by the source varies from *IL*,min to *IL*,max during the time the switch is closed and is zero otherwise as shown in Figure 3-7.

**Figure 3-7: The source current**

When the switch, the inductor, and the capacitor are treated as ideal elements, the average power dissipated by them is zero. Consequently, the average power supplied by the source must be equal to the average power delivered to the load. That is,

$$V_d I_d = V_o I_o = D V_s I_o \tag{3-15}$$

This equation helps us express the average source current in terms of the average load current as given in Eq. 3-16.

$$I_s = DI_o \tag{3-16}$$

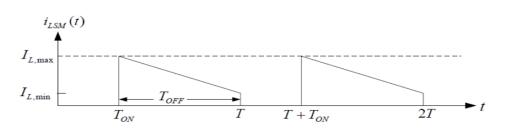

The current through the lower side MOSFET is shown in Figure 3.8. Its average value is given by Eq. 3-17.

Figure 3-8: Current through the low side MOSFET

We know the fact that the buck converter can either operate in its continuous conduction mode or discontinuous mode. When it operates in the continuous conduction mode, there is always a current in the inductor. The minimum current in the continuous conduction mode can be zero.

Consequently, there is a minimum value of the inductor that ensures its continuous conduction mode. It can be obtained from Eq. 3-14 by setting *IL*min to zero as

$$\frac{V_o}{R} - \frac{V_o}{2L_{min}} (1 - D)T = 0$$

(3 - 18)

Hence,

$$L_{min} = \frac{1-D}{2}RT = \frac{1-D}{2f}R$$

(3-19)

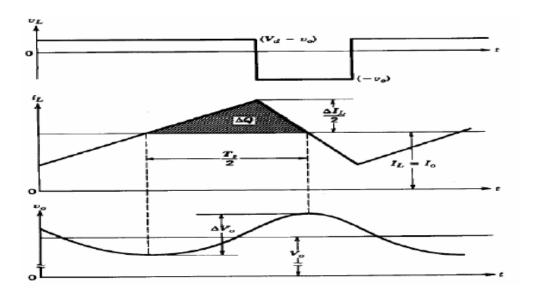

# **3.5 CAPACITOR CALCULATION:**

The output capacitor is assumed to be so large as to yield *vo* (*t*) =*Vo*. However, the ripple in the output voltage with a practical value of capacitance can be calculated by considering the waveforms shown in Figure 3.9 for a continuous-conduction mode of operation. Assuming that the entire ripple component in *iL* flows through the capacitor and its average component flows through the load resistor, the shaded area in Figure 3-9 represents an additional charge  $\Delta Q$

Figure 3-9: Output voltage ripple in a step-down converter

Therefore, the peak to peak voltage ripple  $\Delta Vo$  can be written as

$$\Delta V_o = \frac{\Delta Q}{C} = \frac{\Delta I_L T_s}{8C} \tag{3-20}$$

From Figure 3-9 during toff

41 Department of Electrical And Electronic Engineering, IUT, OIC.

$$\Delta I_L = -\frac{V_o}{L} (1 - D) T_s \tag{3-21}$$

Therefore, substituting  $\Delta$ IL from Eq. 3-21 into the Eq. 3-20 gives

$$\Delta V_o = \frac{T_s}{8C} \frac{V_o}{L} (1-D)T_s \qquad (3-22)$$

$$\frac{\Delta V_o}{V_o} = \frac{T_s^2}{8LC} (1-D)T_s = \frac{\pi^2}{2} (1-D) \left(\frac{f_c}{f_s}\right)^2 \qquad (3-23)$$

Where switching frequency fs = 1Ts and

$$f_c = \frac{1}{2\pi\sqrt{LC}} \tag{3-24}$$

Equation 3-23 shows that the voltage ripple can be minimized by selecting a corner frequency fc of the low pass filter at the output such that  $fc \ll fs$ . Also, the ripple is independent of the output load power, so long as the converter operates in the continuous-conduction mode. We should note that in switch-mode dc power supplies, the percentage ripple in the output voltage are usually specified to be less than, for instance, 1%.

The analysis carried out above assumes ideal components and if we were to make the analysis using all the non-ideal components it would make the derivation a bit more complex with a lot of other parameters included in the final equation. But for the calculation of initial values of the components the above approximations does result in reasonable values. It is also important to realize here that the ESR and ESL are also important and can even dominate. More about how the non-ideality can affect the overall system can be found on [21].

#### **3.6 LINEARIZATION USING STATE SPACE AVERAGING:**

The goal of the following analysis is to obtain a small signal transfer function  $\tilde{V}_o(s)/\tilde{d}(s)$ where  $\tilde{V}_o(s)$  and  $\tilde{d}(s)$  are small perturbations in the output voltage *Vo* and the switch duty ratio *d*, respectively, around their steady-state dc operating values Vo and D.

#### **3.6.1 POWER STAGE AND OUTPUT FILTER:**

**Step 1 State-Variable Description for Each Circuit State:** In a converter operating in a continuous-conduction mode, there are two circuit states: one state corresponds to when the switch is on and the other to when the switch is off. A third circuit state exists during the discontinuous interval, which is not considered in the following analysis because of the assumption of a continuous-conduction mode of operation.

During each circuit state, the linear circuit is described by means of the state-variable vector **x** consisting of the inductor current and the capacitor voltage. In the circuit description, the parasitic elements such as the resistance of the filter inductor and the equivalent series resistance (ESR) of the filter capacitor should also be included. Here Vd is the input voltage. A lowercase letter is used to represent a variable, which includes its steady-state dc value plus a small ac perturbation, for example, vo=Vo+ $\tilde{V}_o$  Therefore, during each circuit state, we can write the following state equations:

$$X = A_1 X + B_1 V_d \quad during \ d. T_s \qquad (3 - 26)$$

$$AND$$

$$\dot{X} = A_2 X + B_2 V_d \quad during \ (1 - d). T_s \qquad (3 - 27)$$

Where A1 and A2 are state matrices and B1 and B2 are vectors. The output *vo* in all converters can be described in terms of their state variables alone as

$v_o = C_1 X \qquad during \ d. T_s \qquad (3-28)$

and

$$v_o = C_2 X$$

during  $(1 - d).T_s$  (3 - 29)

Where C1 and C2 are transposed vectors.

**Step 2: Averaging the State-Variable Description Using the Duty Ratio** *d***.** To produce an average description of the circuit over a switching period, the equations corresponding to the two foregoing states are time weighted and averaged, resulting in the following equations:

$$\dot{X} = [A_1d + A_2]X + [B_1 + B_2(1 - d)]V_d \quad (3 - 30)$$

and

$$v_o = [C_1 d + C_2 (1 - d)]X \tag{3-31}$$

**Step 3: Introducing Small ac Perturbations and Separation into ac and dc Components.** Small ac perturbations, represented by —~I, are introduced in the dc steady-state quantities (which are represented by the upper case letters). Therefore

$$x = X + \tilde{x} \tag{3-32}$$

$$v_o = V_o + \widetilde{v_o} \tag{3-33}$$

and

$$d = D + \tilde{d} \tag{3-34}$$

In general,  $v_d = V_d + \tilde{v_d}$ . However, in view of our goal to obtain the transfer function between voltage  $\tilde{v_o}$  and the duty ratio  $\tilde{d}$ , the perturbation  $\tilde{v_d}$ . is assumed to be zero in the input voltage to simplify our analysis. Therefore

$$v_d = V_d \tag{3-35}$$

Using Eq. 3-32 through 3-35 in Eq 3-30 and recognizing that in steady state,

$\mathbf{X}=\mathbf{0},$

$\dot{\tilde{x}} = AX + BV_d + A\tilde{x} + [(A_1 - A_2)X + (B_1 - B_2)V_d]\tilde{d} + \text{terms containing products of } \tilde{x} \text{ and } \tilde{d} \text{ to be neglected}$ (3 - 36)

where

$$A = A_1 D + A_2 (1 - D) \tag{3-37}$$

and

$$B = B_1 D + B_2 (1 - D) \tag{3-38}$$

The steady-state equation can be obtained from Eq. 3-36 by setting all the perturbation terms and their derivatives to zero. Therefore, the steady-state equation is

$$AX + BV_d = 0 \tag{3-39}$$

And therefore in Eq. 3-36

$$\dot{\tilde{x}} = A\tilde{x} + [(A_1 - A_2)X + (B_1 - B_2)V_d]\tilde{d} \qquad (3 - 40)$$

Similarly, using Eq. 3-32 to 3-34 in Eq. 3-31 results in

$$V_o + \widetilde{v_o} = CX + C\tilde{x} + [(C_1 - C_2)X]\tilde{d} \qquad (3 - 41)$$

Where

$$C = C_1 D + C_2 (1 - D) \tag{3-42}$$

In Eq. 3-41, the steady-state output voltage is given as

$$V_o = CX \tag{3-43}$$

And therefore

$$\widetilde{v_o} = C\widetilde{x} + [(C_1 - C_2)X]\widetilde{d} \tag{3-44}$$

Using Eq. 3-39 and 3-43, the steady-state dc voltage transfer function is

$$\frac{v_o}{v_d} = CA^{-1}B \tag{3-45}$$

44 Department of Electrical And Electronic Engineering, IUT, OIC.

**Step 4: Transformation of the ac Equations in to** *s***-Domain to Solve for the Transfer Function.** Equations 3-40 and 3-44 consist of the ac perturbations. Using Laplace transformation

in Eq. 3-40.

$$\widetilde{Sx(s)} = A\widetilde{x(s)} + [(A_1 - A_2)X + (B_1 - B_2)V_d]\widetilde{d(s)}$$

(3-46)

Or

$$\widetilde{x(s)} = [SI - A]^{-1} + [(A_1 - A_2)X + (B_1 - B_2)V_d]\widetilde{d(s)}$$

(3-47)

Where **I** is the unity matrix. Using a Laplace transformation in Eq. 3-44 and expressing  $\overline{x(s)}$  in terms of  $\overline{d(s)}$  from Eq. 3-47 results in the desired transfer function Tp(s) of the power stages:

$$T_p(s) = \frac{\widetilde{v_{o(s)}}}{\widetilde{d(s)}} = C[SI - A]^{-1}[(A_1 - A_2)X + (B_1 - B_2)V_d] + (C_1 - C_2)X \quad (3 - 48)$$

#### **3.6.2 BUCK CONVERTER:**

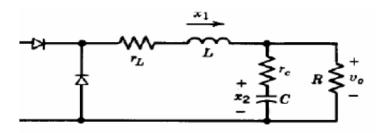

Now we will linearize the power stage and the output filter of the Buck Converter given in Figure 3-15. The two switches are represented by diodes.

Figure 3-10: Buck Converter Circuit

rL is inductor resistance, rc is the equivalent series resistance of the capacitor, and R is the load resistance.

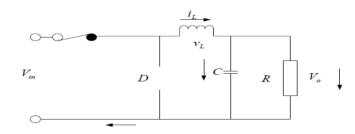

# Figure 3-11: Buck Converter (a) switch on;

(b) switch off

From Figure 3-16 the following equations can be derived.

$$-V_d + L\dot{x_1} + r_L x_1 + R(x_1 - C\dot{x}_2) = 0 \qquad (3 - 49)$$

And

$$-x_2 - Cr_c \dot{x}_2 + R(x_1 - C\dot{x}_2) = 0 \qquad (3 - 50)$$

In matrix form, these two equations can be written as

$$\begin{bmatrix} \dot{x_1} \\ \dot{x_2} \end{bmatrix} = \begin{bmatrix} -\frac{Rr_c + Rr_L + r_c r_L}{L(R + r_c)} & -\frac{R}{L(R + r_c)} \\ \frac{R}{C(R + r_c)} & -\frac{1}{C(R + r_c)} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_d$$

(3-51)

Comparing the equations with Eq. 3-26 yields

$$A_{1} = \begin{bmatrix} -\frac{Rr_{c} + Rr_{L} + r_{c}r_{L}}{L(R + r_{c})} & -\frac{R}{L(R + r_{c})} \\ \frac{R}{C(R + r_{c})} & -\frac{1}{C(R + r_{c})} \end{bmatrix}$$

(3 - 52)

And

$$B_1 = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} \tag{3-53}$$

The state equation for the circuit of Fig 3.15 with the switch off can be written by observation, noting that the circuit of Fig. 3.16(b) is exactly the same as the circuit of Fig 3.16(a) with Vd set to zero.

$$A_2 = A_1 \tag{3-54}$$

$$B_2 = 0$$

(3 – 55)

The output voltage in both the circuit states is given as

$$v_{o} = R(x_{1} - C\dot{x}_{2})$$

$$= \frac{Rr_{c}}{R + r_{c}}x_{1} + \frac{R}{R + r_{c}}x_{2}$$

(3 - 56)

Using  $\dot{x}_2$  from Eq. 3-50

$$= \begin{bmatrix} \frac{Rr_c}{R+r_c} & \frac{R}{R+r_c} \end{bmatrix} \begin{bmatrix} x_1\\ x_2 \end{bmatrix}$$

Therefore, in Eq. 3-28 and 3-29

$$C_1 = C_2 = \begin{bmatrix} \frac{Rr_c}{R + r_c} & \frac{R}{R + r_c} \end{bmatrix}$$

(3 - 57)

46 Department of Electrical And Electronic Engineering, IUT, OIC.

$$A = A_1$$

(from Eq - 37 and Eq - 54) (3 - 58)

$$B = B_1 D$$

(from Eq - 38 and Eq - 55) (3 - 59)

$$C = C_1 (from Eq - 42 and Eq - 57)$$

(3 - 60)

Model Simplification: In all practical circuits,

$$R \gg (r_C + r_L) \tag{3-61}$$

Therefore, A and C are simplified as:

$$A = A_1 = A_2 = \begin{bmatrix} -\frac{r_C + r_L}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix}$$

(3 - 62)  $C = C_1 = C_2$

=  $[r_C \quad 1]$ (3 - 63)

and **B** remains unaffected as:

$$B = B_1 D = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} D \tag{3-64}$$

Where **B**2=0. From Eq. 3-62,

$$A^{-1} = \frac{LC}{1 + (r_c + r_L)/R} \begin{bmatrix} -\frac{1}{RC} & \frac{1}{L} \\ -\frac{1}{C} & -\frac{r_c + r_L}{L} \end{bmatrix} \quad (3 - 65)$$

$$\frac{V_o}{V_d} = D \frac{R + r_c}{R + (r_c + r_L)} \cong D \quad (3 - 66)$$

$$G(s) = \frac{v_o(s)}{d(s)} \cong V_d \frac{1 + Sr_C C}{LC[S^2 + S\left\{\frac{1}{RC} + \frac{(r_C + r_L)}{L}\right\} + \frac{1}{LC}]}$$

(4 - 67)

Eq. 3-67 is the Open Loop Transfer Function of the circuit represented in Figure 3.16. The term in the third brackets in the denominator of Eq. 3-69 are of the form  $S^2 + 2\varepsilon\omega_o S + \omega_o^2$ , where 1

$$\omega_0 = \frac{1}{\sqrt{LC}}$$

(3-68)

$$\varepsilon = \frac{\frac{1}{RC} + \frac{r_C + r_L}{L}}{2\omega_0}$$

(3-69)

Therefore, from Eq. 3-67 the transfer function can be written as

47 Department of Electrical And Electronic Engineering, IUT, OIC.

$$\omega_0 = F_{LC}$$

$$T_p(s) = \widetilde{\frac{v_o(s)}{d(s)}} = V_d \frac{\omega_o^2}{\omega_z} \frac{S + \omega_z}{S^2 + \varepsilon \omega_o S + \omega_o^2} \qquad (3 - 70)$$

Where a zero is introduced due to the equivalent series resistance of the output capacitor at the frequency

$$\omega_z = F_{ESR} = \frac{1}{r_C C} \tag{3-71}$$

# **3.7 DESIGN PARAMETERS:**

The converter, in this thesis, is designed for CCM operation, and needs to operate from a  $12 \pm 3$  V DC source. The output voltage, Vo, from the converter must be  $2 \pm 0.1$  V with a steady-state ripple of less than 2.5 percent or 0.05 V. The converter is required to maintain output voltage while the output current, Io, varies between 1 A and 10 A.

#### **3.8 TIME DOMAIN ANALYSIS OF OPEN LOOP DC-DC BUCK CONVERTER:**

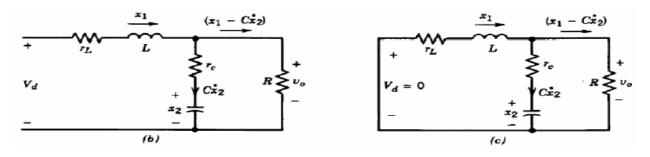

. The time-domain response of the buck converter needs to maintain within operating parameters stated within section 3.7. As the input source varies  $\pm 3$  V and loads vary between 1 A and 10 A, the output voltage is required to be  $2 \pm 0.1$  V. Three separate responses are analyzed to see if the buck converter remains within the required operating parameters: connection to the 12 V DC power source, 1 A step change in the load, and 1 V step change in the power source. The open loop Simulink model of Dc-Dc Buck converter is shown in figure 3-17.

#### Figure 3-12: Simulink model of buck converter

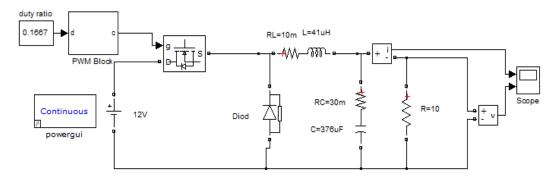

#### **3.8.1 OUTPUT RESPONSE OF THE CONVERTER TO 12V DC POWER SOURCE:**

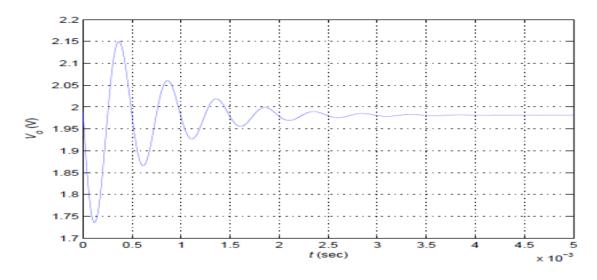

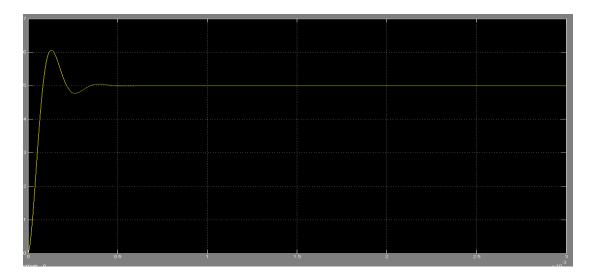

The buck circuit is required to reach a steady-state voltage of 2 V when connected to a 12 V power source. The converter is connected to the source operating under minimum loading conditions: 1 A. The duty cycle is set to 0.1667. From the response shown in Figure 3-18, it can be seen that the output voltage meets the steady-state operating conditions; the steady-state error is 0.4

percent. The transient characteristics are a maximum overshoot of 69.4 percent, a rise time of 88 sec, and a settling time of 2.75 msec.

Figure 3-13: Uncompensated open-loop time-response of buck converter to a 12 V power source with a duty cycle of 0.1667.

#### 3.8.2 OUTPUT RESPONSE TO 1AMP STEP CHANGE IN LOAD CURRENT:

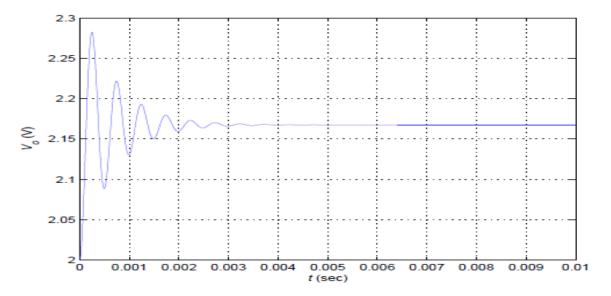

The load is capable of varying between 1 AMP and 10 AMP after the system has reached steady-state. The changes in the load alter the operating condition of the system and therefore changes in the load are analyzed to see if the system still remains within operating parameters after a change in the load has occurred. To test the system, a 1 AMP step change in the load is applied. The response can be seen in Figure 3.19. The output voltage response still meets steady-state operating conditions but the transient operating parameters are not satisfied. The steady-state error is 1 percent. The maximum overshoot is 7.5 percent, and the maximum undershoot is 13.5 percent, which exceed outside the 5 percent requirement

Figure 3-14: Uncompensated open-loop time-response to a 1 Amp step change in the load current with the same duty cycle.

#### 3.8.3 OUTPUT RESPONSE TO 1V STEP CHANGE IN INPUT POWER SOURCE:

The source is capable of varying  $\pm 3$  V, and changes in the source voltage affect the operating condition of the system, and therefore can impact the output voltage. To test if the system remains within operating parameters, a 1 V step change is applied to the converter after response from the power source has reached steady-state. The response of the output voltage can be seen in Figure 3-20. The output voltage no longer meets the steady-state operating requirements. The steady-state error is 8.4 percent. In addition, the peak response of the system is 2.282 V, which exceeds the 5 percent requirement.

Figure 3-15: Uncompensated open-loop time-response to a 1 V step change in source voltage with the same duty cycle.

# CHAPTER 04 DESIGN OF ANALOG AND DIGITAL PID CONTROLLERS FOR DC-DC BUCK CONVERTER

# 4. INTRODUCTION

In this chapter, typical methods used to design analog and digital PID controllers are discussed. First, PID compensator design based upon root locus is introduced, and the procedure for designing the compensator is explained. Next, PID design based on a frequency response method is discussed.

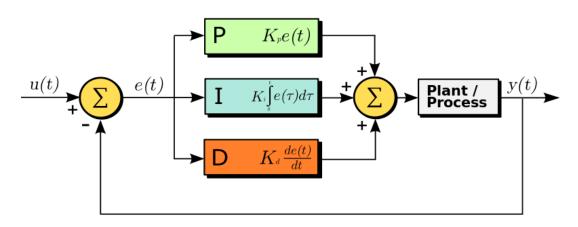

# 4.1 DESIGN OF ANALOG PID CONTROLLER:

Analog PID controllers are common in many applications. They can be easily constructed using analog devices such as operational amplifiers, capacitors and resistors. They are reliable in mechanical feedback systems, and able to satisfy many control problems. Different methods of PID controller design are discussed below. The general block diagram of PID compensated system is shown in the figure 4-1. Where P, I and D are the Proportional, Integral and Differential gains of controllers respectively. U(t) is the reference signal, e(t) is the error signal and Y(t) is the desired output.

Figure 4-1: PID compensated system

# 4.1.1 DESIGN VIA ROOT LOCUS METHOD:

Root locus is one of the methods used to design control systems. It is a technique that plots closed-loop poles in the complex plane as the gain varies from zero to infinity. It is a method that analyses the relationship between the poles, gain and the stability of the system. By understanding the root locus plot, one can design a controller to novel specifications, and understand clearly how different controller architectures affect the system.

In a root locus, the imaginary component of a pole corresponds to damped natural frequency, while the radius from the origin to the pole corresponds to natural frequency. The settling time for a system is determined by the slowest response among all responses. The least settling time

can be achieved if the roots fall to the far left on the left-hand plane; overshoot can be prevented by placing the poles on the real axis.

In order to design a PID controller using the root locus method, the system must be first transformed into a transfer function. In general, root locus technique analyzes only single input single output (SISO) systems. However, an appropriate approximation of transforming a multi input multi output (MIMO) system into a SISO model can produce a close estimation of the characteristics of the system. A root locus that passes through the right-hand plane is considered unstable, whereas one that remains in the left-hand plane implies a stable system. A root locus that falls in the  $j\omega$  axis (between the right- and left-hand planes) is considered marginal stable.